- •Центральный процессор

- •1. Повышение производительности процессоров

- •2.1. Технологии многопоточности

- •2.2. Технология Hyper-Threading

- •2.3. Многоядерность

- •2.4. Технология виртуализации Hypervisor

- •2.5. Технология удаленного управления компьютерами сети

- •2.6. Технология ускорения процесса ввода-вывода данных – Acceleration Technology

- •3. Многоядерные процессоры корпорации Intel

- •3.1. Архитектурные особенности процессора Pentium d

- •3.2. Судьба системной шины

- •3.3. Производительность

- •3.4. Многоядерное будущее

- •5. Многоядерные процессоры компании ibm

- •5.1. Двухъядерный (dual-core) процессор Power 4

- •5.2. Следующий шаг - Power 5

- •5.5. Процессорный элемент Cell -"суперкомпьютер-на-кристалле"

- •7. Заключение

- •8. Планы Intel на 2009/2010 гг по выпуску процессоров

- •9. Тенденции развития средств вычислительной техники

- •1. Повышение тактовой частоты.

- •2. Увеличение объема и пропускной способности подсистемы памяти.

- •4. Системы на одном кристалле и новые технологии.

2.2. Технология Hyper-Threading

Анонсированная в 2002 годукомпаниейIntel технологияHyper-Threading–пример многопоточной обработки команд. Данная технология является чем-то средниммежду многопоточной обработкой, реализованной в мультипроцессорныхсистемах, ипараллелизмомнауровнеинструкций, реализованном в однопроцессорныхсистемах. Фактически технология Hyper-Threading позволяет организовать два логическихпроцессора в одном физическом. Таким образом, с точки зренияоперационной системы изапущенногоприложения всистемесуществует двапроцессора,что дает возможность распределять загрузку задач между ними.

Посредством реализованного в технологииHyper-Threadingпринципапараллельностиможно обрабатыватьинструкции впараллельном (ане впоследовательном) режиме, то есть для обработки все инструкции разделяются на двапараллельных потока. Это позволяет одновременно обрабатывать два различныхприложения или два различных потока одного приложения и тем самым увеличить IPCпроцессора (количество инструкций, выполняемых процессором в секунду), чтосказываетсяна росте егопроизводительности.

В конструктивномпланепроцессор споддержкой технологииHyper-Threadingсостоитиз двух логическихпроцессоров,каждыйизкоторыхимеетсвои регистры иконтроллерпрерываний (ArchitectureState, AS). Азначит, двепараллельноисполняемыезадачиработаютсосвоимисобственныминезависимыми регистрами ипрерываниями, но при этом используют одни и те же ресурсы процессора для выполнения своих задач. После активизации каждый из логических процессоров можетсамостоятельно инезависимо от другогопроцессора выполнятьсвоюзадачу, обрабатыватьпрерывания либо блокироваться.

Таким образом, от реальной двухпроцессорнойконфигурацииновая технология отличается только тем,что оба логических процессора используют одни и те же исполняющие ресурсы, одну и ту же разделяемуюмеждудвумяпотокамикэш-память и одну иту жесистемную шину. Использование двух логических процессоров позволяет усилить процесс параллелизманауровнепотока, реализованный всовременных операционныхсистемах ивысокоэффективных приложениях. Команды от исполняемых параллельно потоков одновременно посылаются для обработки ядру процессора. Используя технологию out-of-order (исполнениекомандныхинструкцийне впорядкеихпоступления), ядропроцессораспособнопараллельно обрабатывать обапотоказасчѐтиспользованиянесколькихисполнительных модулей.

Идея технологииHyper-Threading тесносвязана смикроархитектурой NetBurstпроцессораPentium 4 и является вкаком-тосмыслееѐ логическимпродолжением.

МикроархитектураIntelNetBurstпозволяетполучитьмаксимальный выигрышпроизводительностипри выполнении одиночногопотокаинструкций, тоестьпри выполнении однойзадачи. Однако, даже вслучаеспециальнойоптимизациипрограммы, не все исполнительные модули процессора оказываютсязадействованнымина протяжении каждого тактового цикла. В среднем, при выполнении кода, типичного для набора команд IA-32, реально используется только 35% исполнительных ресурсовпроцессора, а 65%исполнительных ресурсовпроцессорапростаивают,что означаетнеэффективноеиспользование возможностейпроцессора.Было бы логично реализовать работу процессора таким образом, чтобы в каждом тактовом циклемаксимально использовать его возможности. Именно эту идею и реализует технологияHyper-Threading,подключаянезадействованные ресурсыпроцессора к выполнениюпараллельной задачи.

В современныхприложениях в любоймомент времени,какправило, выполняется не одна, а несколько задач или несколько потоков (тредов - threads) однойзадачи, называемых также нитями. В качестве примера рассмотрим работу двухпотоков. При одновременномисполнении обоихпотоковпроцессорбудетпостояннопереключаться междупотоками, за один такт процессора выполняются толькоинструкции какого-либо одного из потоков. На каждом такте процессора используются далеко не все исполнительные блоки процессора, поэтому имеется возможностьчастичносовместить выполнениеинструкций отдельныхпотоковнакаждом тактепроцессора. Например, выполнение двух арифметических операций с целыми числамипервогопотокаможносовместить сзагрузкой данныхизпамяти второгопотока и выполнить все три операцииза один тактпроцессора. Аналогичнона втором тактепроцессораможносовместить операциюсохранения результатовпервогопотока сдвумя операциями второго потока и т.д. Собственно, в таком параллельном выполнении двухпотоков изаключается основнаяидея технологииHyper-Threading.

Hyper-Threading - это виртуальная многопроцессорность, так как процессор на самом деле один, аоперационнаясистема видит двапроцессора. Классическому"одноядерному"процессору добавилиеще один логический блокуправления AS(Architectural State) технологии IA-32 (рис.1).

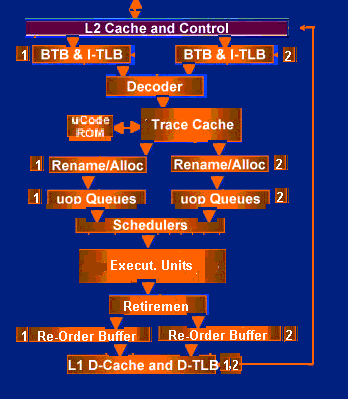

Рис.1. Блокиуправления AS (ArchitecturalState) технологииIA-32.

ArchitecturalState отслеживаетсостояние регистров (общегоназначения,управляющих,прерываний - APIC,служебных),используяединственное физическое ядро (блоки предсказания ветвлений, ALU, FPU, SIMD-блоки и пр.) AS1 представляетиз себя один логический процессор (LP1), AS2 — второй логический процессор (LP2).

У каждого логическогопроцессораестьсвойсобственныйконтроллерпрерываний (APIC — Advanced Programmable Interrupt Controller) и набор регистров. Длякорректного использования общих регистров двумя логическимипроцессорамисуществуетспециальная таблица — RAT(Register AliasTable),согласнокоторойможноустановитьсоответствиемежду регистрами общегоназначения общегопроцессорного ядра.Таблицаиспользования регистров RAT укаждого логическогопроцессора своя. В результате получается схема, при которой на одном и том же ядремогутсвободно выполняться два независимых потока программногокода.

У процессора с технологиейHyper-Threadingпредусмотрены два основных режима работы: Single-Task (ST) и Multi-Task (MT). В режиме ST активным являетсятолько один логический процессор, который безраздельно пользуется доступными ресурсами, другой логический процессор остановлен командой HALT. При появлении второгопрограммногопотока бездействовавший логическийпроцессорактивируется (посредствомпрерывания), и физическийпроцессорпереводится в режим работы с двумяпотоками (рис.2).

Рис.2.Разделение ресурсов двумя логическими процессорами.

При работе двух потоков поддерживаются две очереди инструкций (NextInstruction Pointers). Большая часть инструкций берется из кэш трассировки Trace Cache (TC), где онихранятся в декодированном виде, и доступ ккэш трассировки дваактивных логическихпроцессораполучаютпоочередно,через такт. В то же время,когда активен только один логический процессор, он получает монопольный доступ ккэш трассировки безчередованияпо тактам. Аналогичным же образомпроисходит и доступ кпамятимикропрограмм (Microcode ROM).Блоки трансляцииинструкций(ITLB -Instruction TranslationLook-asideBuffer) действуютприотсутствиинеобходимых инструкций в кэш команд и доставляют команды, каждый для своего отока.Блок декодированияинструкций(IA-32Instruction Decode) является разделяемым и в случае, когда требуется декодирование инструкций для обоихпотоков, обслуживаетихпоочередно (через такт).Блоки очереди декодированныхкоманд (Uop Queue) и блок распределениякомандпоисполнительнымустройствам (Allocator) разделяются надвое, отводя пополовине элементов длякаждого логическогопроцессора. Пять планировщиков (Schedulers) обрабатывают очереди декодированныхкоманд,независимо отпринадлежностиих ккакому либопотоку, инаправляюткомандына выполнениенужнымисполнительнымустройствам (Execution Units) взависимости от готовности к выполнениюкоманд и доступностиисполнительныхустройств. Кэшпамять всехуровней являетсяполностью разделяемоймежду двумя логическимипроцессорами,но для обеспеченияцелостности данныхзаписи вбуфер данных (DTLB - Data Translation Look-aside Buffer) снабжаются дескрипторами в видеидентификатора (ID) каждого логическогопроцессора.

Начальная часть конвейера Pentium 4 отвечает за подачу микроопераций (декодированных x86 инструкций) на исполнительную часть конвейера. Именно тут, в основном, и находятся дублирующиеся блоки для каждого из двух логическихпроцессоров. Кэш трассировки (Trace Cache)содержитуже декодированныеинструкции.Большинствокомандпри реальной работепроцессора декодированозаранее инаходится вкэш трассировки. Trace Cacheнедублируется длякаждогоиз логических процессоров, а разделяется между ними. Тем не менее, у каждого логического процессора существует свой собственный блок трассировки, ссылающийсяна следующую инструкцию для выполнения. Инструкции из Trace Cache выбираютсяпо очереди истановятся в такназываемуюочередь выборки, такжеиндивидуальную для обоих логическихпроцессоров.

При отсутствии очередной инструкции в Trace Cache, являющемся в Pentium 4посвоейиерархиикэшпамятьюпервогоуровня дляинструкций,процессор должен декодировать очередную x86инструкциюизL2 -кэш второго уровня.Выборкаинструкции осуществляетсяпри участии блока трансляцииадресакоманд(Instruction TranslationLookasideBuffer-ITLB),переводящемадрес,хранящийся в блоке трассировки, в физический адрес.ITLB является также индивидуальным для каждогопроцессора, а L2-кэш разделяется между логическими CPU. Декодер x86 инструкций в процессорах с технологией Hyper-Threading общий, поскольку его загрузка невелика –большинство декодированныхинструкцийужехранится в Trace Cache.Если же оба логических процессора обращаются к декодеру одновременно, он чередует свою работу между логическими процессорами, но только после выполнения полного цикла декодирования для одногоиз логическихCPU. Декодированныеинструкциизаписываются вTrace Cache.

К исполнительномуустройству декодированныепоследовательностиинструкцийприходят в двухочередях –своя очередь длякаждогоиз логическихпроцессоров. Впервую очередь инструкции из двух входящих очередей проходят через блоки выделения ресурсов(Allocator) ипереименования регистров(RegisterRename). Здесьпроисходит выделениенеобходимых ресурсов дляисполнениякоманд. Машинные регистры ибуферыделятсяпоровнумежду логическимипроцессорами, однако, при отказе одного из логических процессоров от использования тех или иных ресурсов, они могутбыть всецело выделены только одному логическому процессору. После прохождения этой стадии команды попадают в две отсортированные очереди – для операций с памятью и для остальных операций, которые также разделены пополам – длякаждогоиз логическихпроцессоров.

Затем, рассортированные микрооперации приходят на стадию определения очередности выполнения (Scheduling), где выполняется сортировка порядка следованияинструкцийприпоступлениинаисполнительныеустройства. Операциина блоки-планировщикиприходятпомерепоступления. Принеобходимости,планировщикипереключаются с очередей одного логическогопроцессора на очереди другого. На этом этапе,кстати,происходитокончательноесмешениемикроопераций,приходящих с логических процессоров, для возможности их одновременного исполнения. Посколькумашинные регистрыфизическогопроцессора к этомумоменту оказываются жесткопривязанными к регистрам обоих логическихпроцессоров,исполнениеинструкций действительностановится возможным без разборапринадлежностикоманд.

После этапа выполнения,накоторомпроцессорне различает логическиепроцессоры,следует блок восстановления (Retirement), где восстанавливаетсяизначальный порядок инструкций и их принадлежность к каждому из логических процессоров. При этомбуфер восстановленияпорядка ( Re-OrderBuffer) делитсяпополам между логическими процессорами.

Хотя кэш память первого и второго уровня является разделяемой между логическимипроцессорами,буфер трансляции данных (Data Translation LookasideBuffer - DTLB), сопоставляющий адреса данных и их физические адреса,хоть и делитсямежду процессорами, но записи в нем дополнены идентификатором процессора,которому принадлежит каждаяиз строк буфера.

Таким образом, технология Hyper-Threading действительно позволяет загрузитьисполнительныеустройствапроцессоразначительносильнеезасчет одновременного выполнения двух потоков. Однако, следует понимать, что эффект от такого приема не всегда может быть положительным. Во-первых, если выполняемые потоки похожи по типувыполняемыхинструкций, выигрышаможетне быть вовсе,поскольку одинизпотоковбудетполностьюзанимать все ресурсы,необходимые и другомупотоку. Простои же остальных исполнительных устройств процессора от этого не исчезнут. Во- вторых, возможна икуда болеекатастрофичнаяситуация. Одинизпотоковможетпопросту занять ресурсы, необходимые другому потоку, и ожидать при этом,например,поступления данных. Операционная система же при этом, пребывая в уверенности, чтоимеется два CPU,небудетпредприниматьникаких действий,насамомже делефункционированиепроцессорабудетпопроступарализовано. ИменнопоэтомуIntel обратилась спризывом к разработчикампрограммного обеспечения оптимизироватьсвоипрограммы дляHyper-Threading. Один из основных принципов такой оптимизации –применениеновойинструкцииPAUSE,не допускающейпустыхциклов ожидания.

В ноябре 2002 года, компания Intel официально анонсировала свой очереднойпроцессор всемействеPentium 4,IntelPentium 4 3.06 ГГц. Этотпроцессор являлсяпервым CPU в семействе,поддерживающем технологиюHyper-Threading.