- •ВВЕДЕНИЕ

- •1.1. Свойства электрона

- •1.2. Виды электронной эмиссии

- •Глава 2 ИОННЫЕ ПРИБОРЫ

- •2.1. Вольт-амперная характеристика газового разряда

- •2.2. Стабилитроны

- •2.3. Неоновые лампы

- •2.4. Тиратроны

- •2.5. Разрядники

- •Глава 3 ПОЛУПРОВОДНИКОВЫЕ ПРИБОРЫ

- •3.1. p-n переход и его свойства

- •3.2. Общие сведения о полупроводниковых диодах

- •3.3. Выпрямительные диоды

- •3.4. Опорные диоды

- •3.5. Варикапы

- •3.6. Туннельные диоды

- •3.7. Биполярные транзисторы

- •3.8. Полевые транзисторы

- •3.9. Составные транзисторы

- •3.10. Нагрузочный режим работы транзистора

- •3.11. Тиристоры

- •3.12. Полупроводниковые фотоприборы

- •3.13. Терморезисторы

- •3.14. Правила монтажа и эксплуатации полупроводниковых приборов

- •4.1. Ионные цифровые и знаковые индикаторы

- •4.2. Полупроводниковые индикаторы

- •4.3. Жидкокристаллические индикаторы

- •Глава 5 ВЫПРЯМИТЕЛИ И СГЛАЖИВАЮЩИЕ ФИЛЬТРЫ

- •5.1. Общие сведения о выпрямителях

- •5.2. Однофазные схемы выпрямления

- •5.3. Трёхфазные схемы выпрямления

- •5.4. Условно-многофазные вентильные схемы выпрямления

- •5.5. Управляемые выпрямители

- •5.6. Сглаживающие фильтры

- •5.7. Коммутация в выпрямителях

- •Глава 6 ПРЕОБРАЗОВАТЕЛИ И ИНВЕРТОРЫ

- •6.1. Общие сведения о преобразователях

- •6.2. Зависимые инверторы

- •6.3. Реверсивные преобразователи

- •Глава 7 ЭЛЕКТРОННЫЕ УСИЛИТЕЛИ

- •7.1. Общие сведения об усилителях

- •7.2. Режимы работы усилительных элементов

- •7.3. Обратные связи в усилителях

- •7.4. Каскады предварительного усиления

- •7.5. Выходные каскады

- •7.6. Многокаскадные усилители

- •7.7. Операционные усилители

- •7.8. Общие сведения об автогенераторах

- •7.9. Связанные контуры

- •7.10. Автогенераторы типа LC

- •7.11. Трёхточечные автогенераторы

- •7.13. Стабилизация частоты генераторов

- •Глава 8 МИКРОЭЛЕКТРОНИКА

- •8.1. Общие сведения об интегральных микросхемах

- •8.2. Классификация и маркировка интегральных микросхем

- •8.3. Область применения аналоговых ИМС

- •8.4. Область применения цифровых ИМС

- •8.5. Система обозначений интегральных микросхем

- •Глава 9 ОСНОВЫ ИМПУЛЬСНОЙ ТЕХНИКИ

- •9.1. Электрические импульсы и их параметры

- •9.2. Цепи формирования импульсов и ограничители

- •9.3. Работа транзисторов в ключевом режиме

- •9.4. Общие сведения об импульсных генераторах

- •9.5. Работа транзистора в импульсном режиме

- •9.6. Мультивибраторы

- •9.7. Мультивибраторы в интегральном исполнении

- •9.8. Триггеры

- •9.9. Блокинг-генераторы

- •9.10. Импульсные усилители

- •Глава 10 ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

- •10.1. Общие сведения о логических элементах

- •10.2. Основные логические элементы и функции

- •10.3. Комбинированные логические элементы

- •10.4. Логические элементы в интегральном исполнении

- •10.5. Триггеры на логических элементах

- •10.6. Счётчики

- •Глава 11 ДАТЧИКИ И РЕЛЕ

- •11.1. Датчики

- •11.2. Реле

- •Глава 12 ЗАЩИТА ЭЛЕКТРОННЫХ УСТРОЙСТВ

- •12.1. Бесконтактные защиты тиристорных устройств

- •12.2. Защита от перенапряжений

- •12.4. Стабилизаторы напряжения и тока

- •Список литературы

- •СОДЕРЖАНИЕ

—повышенное выходное сопротивление (до 1 Ком);

—значительный разброс всех параметров.

10.5. Триггеры на логических элементах

Триггеры или такназываемые триггерные элементы выполняют функцию запоминания значений логических переменных в цифровыхсхемах. Триггер— этоустройство, способноеформироватьдва устойчивыхзначениявыходногосигналаискачкообразноизменять этизначенияподдействиемвнешнегоуправляющегосигнала. Именно способность формировать на выходе два устойчивых значения сигнала, которые могут поддерживаться без изменения сколь угодно длительный промежуток времени, и позволяет применять триггер в качестве элемента памяти.

Существует большое разнообразие триггеров, выполненных в виде ИС малой степени интеграции. Кроме триггеров на транзисторахсоднимтипомпроводимости существуютсхемы, использующие транзисторы как на n-p-n, так и p-n-p типов (схемы с дополнительной симметрией).

Триггеры можно образовать соединением одной или нескольких микросхем многовходовых логических элементов или соединением микросхемы и при необходимости дискретных элементов (резисторов, конденсаторов).

Существующиетипытриггеровможноклассифицироватьпоразличным признакам. Наиболее часто триггеры классифицируют по типу используемых информационных входов. Различают следующие типы основных информационных входов триггера:

R — раздельный вход сброса триггера;

S — раздельный вход установки триггера; К — вход сброса универсального триггера;

J — вход установки универсального триггера; Т — счётный вход триггера установки триггера;

D — информационный вход переключения триггера в состояние, соответствующее логическому уровню на этом входе;

С — управляющий или синхронизирующий вход.

Кромеэтихосновныхвидовнекоторыетриггерымогутснабжаться входом V. Этот вход блокирует работу триггера и сколь угодно долго может сохранять ранее записанную в него информацию.

260

С точки зрения типа используемых входов различают RS-, Т-, |

|

D-, JK-, VD- и VT- триггеры. |

|

По моменту реакции на входной сигнал триггеры подразделяют |

|

на синхронные и асинхронные. Асинхронные триггеры переходят в |

|

новое состояние при воздействии той или иной комбинации сигна- |

|

лов, подаваемых на установочные (информационные) входы. Синх- |

|

ронныетриггерыпомимоинформационныхимеютдополнительный |

|

вход синхронизации (синхровход) С. Этот вход носит также назва- |

|

ние тактовый вход С (Сlock — времязадающий). Такой триггер мо- |

|

жетперейтивновоесостояние, есливместесопределённойкомбина- |

|

цией сигналов на информационных входах на входС поступает син- |

|

хронизирующий (управляющий) сигнал. Какой процесс при этом |

|

реализуется, зависит от типа и схемы триггера. |

|

Повидуактивногологическогосигнала, действующегонаинфор- |

|

мационных входах, триггеры делят на статические — управляемые |

|

уровнем, идинамические— управляемыеперепадомвходногосигна- |

|

ла. При этом сами входы могут быть прямыми и инверсными. Для |

|

переключения триггера на его прямой вход необходимо подать сиг- |

|

нал x, а на инверсный — x–. |

|

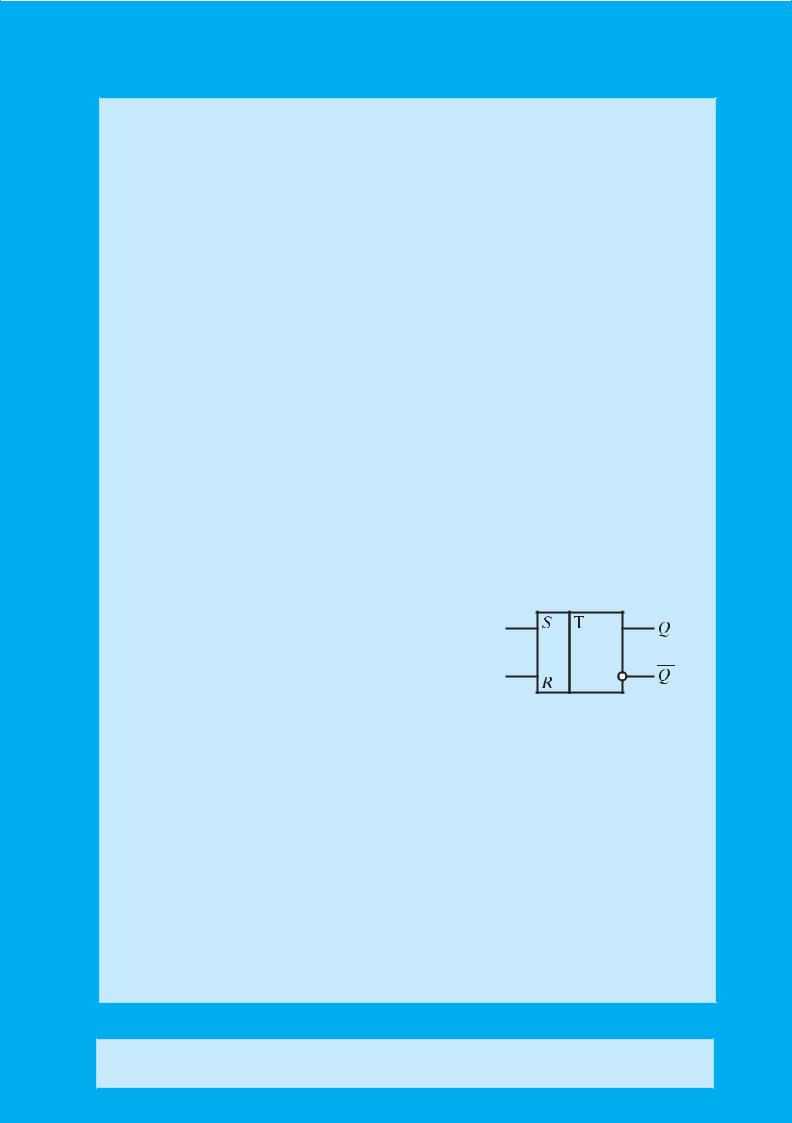

Нарис. 10.15, впоказаноусловноеграфическоеобозначениетриг- |

|

геровсасинхроннымиустановочнымиR иS исинхроннымивхода- |

|

ми. Реальныетриггерымогутнеиметьнекоторыхвходовилииметь |

|

дополнительные входы. Буква Т в |

|

изображенииотноситсякасинхронно- |

|

му или синхронному однотактному |

|

(одноступенчатому) триггеру, а ТТ — |

|

к двухступенчатому. В цифровых уст- |

|

ройствах широко используются RS |

Рис. 10.15. Условное графи- |

триггеры (R — первая буква от слова |

ческоеобозначениеасинхрон- |

Reset — сброс, S первая буква от сло- |

ного RS-триггера |

ва set — установка), D-триггеры (D |

|

первая буква от слова delay — задержка), Т-триггеры, универсаль- |

|

ные триггерные элементы JК-типа и некоторые другие. |

|

Асинхронные RS-триггеры |

|

Этот триггер строится на комбинированных логических элементах |

|

И-НЕ, а также на комбинированных логических элементах ИЛИ-НЕ. |

|

На рис. 10.16 представлен триггер на логических элементах И-НЕ и |

|

таблицапереключенийсхемы(таблицасоответствия10.3). Триггериме- |

|

|

261 |

Таблица 10.3 |

Рис. 10.16. Асинхронный RS-триггер на элементах И-НЕ |

етдвавыхода, состояниякоторыхдолжныбытьинверсными. Состоя- |

ниетриггераопределяетсяпоуровнюсигналанавыходе1 (Q). ЕслиQ |

= 0, триггернаходитсявнулевомсостоянии, априQ = 1 триггернахо- |

дитсявединичномсостоянии, приэтомнавыходе2 (Q—) долженбыть |

противоположный уровень сигнала (соответственно 1 или 0). |

Приподаченулевыхуровнейсигналоводновременнонаобавхо- |

да на выходах появляется единичный уровень сигнала, то есть Q = |

— |

(Q). Эта комбинация входных сигналов (R = S = 0) является запрет- |

— |

ной, так как должно соблюдаться условие инверсии Q = (Q). Для |

установки триггера в единичное состояние необходимо сохранить |

на входе 1 нулевой уровень сигнала (S = 0), а на вход 2 подать еди- |

ничный уровень сигнала (R = 1). Тогда—на выходе Q появится еди- |

ничный уровень сигнала, а на выходе (Q) — нулевой. |

Дляпереводатриггеравнулевоесостояниенеобходимоизменить |

состояние каждого из входов на противоположное (S = 1, R = 0). |

Тогда на выходе Q появится нулевой уровень сигнала, а на выходе |

— |

(Q ) — единичный. |

При подаче на оба входа единичного уровня сигнала (R = S = 1) |

триггернеизменяетсвоегосостояния, т.е. сохраняетсуществующее |

состояние. Поэтому данная комбинация входных сигналов обеспе- |

чивает режим хранения триггера. |

Аналогичнымспособомможнореализоватьтакойжетриггерна |

элементах ИЛИ-НЕ. В такой схеме рис.10.17 процессы переключе- |

ния и хранения аналогичны рассмотренным выше. Однако при за- |

мене операции И операцией ИЛИ все переменные необходимо ин- |

вертировать. Таблица состояний (10.4) имеет уже другой вид. |

262 |

Таблица 10.4 |

Рис. 10.17. Асинхронный RS-триггер на элементах ИЛИ-НЕ |

Синхронный одноступенчатый RS-триггер |

Такой триггер можно представить с помощью схем И—НЕ |

(рис. 10.18). Он имеет два информационных (установочных) входа |

R и S, вход синхронизации С и два выхода. Если на вход S посту- |

пает сигнал логической 1, а R = 0, то при действии синхросигнала |

С триггер устанавливается в состояние 1 независимо от того, в |

Рис. 10.18. Условное графическое обозначение (а), схема на элементах |

И—НЕ (б) и временные диаграммы синхронного RS-триггера. |

263 |

каком состоянии он находился до этого момента. При R = 1, S = 0 происходит сброс триггера. Если R = S = 0, то триггер под действием синхросигнала не меняет своего состояния. Комбинация R = S = 1 является запретной. Таблица переключений аналогична табл. 10.3 при С = 1. Условием чёткой работы рассматриваемого триггера является неизменность значений сигналов R и S во время действия синхросигнала С, причём длительность задержки выбирается больше суммарной задержки переключения элементов схемы. В силу сказанного время, которое проходит от времени изменения входных сигналов до соответствующего изменения состояния выходов, зависит от времени распространения по всем входящимвтриггервентилям. Этовремяназываетсявременемсрабатывания (или переключения) триггера tср и оно должно находиться в пределах между последним изменением входных сигналов и моментом установления логического нуля на входеС. В противномслучае триггер можетнеуспеть среагировать наизменение входных сигналов (см. временную диаграмму на рис. 10.18, в).

D-триггер

ШирокоиспользуемыеD-триггерыпредставляютсобойэлемент памяти с одним информационным входом, предназначенным для запоминания логических сигналов.

Иногдаэтоттриггерназываюттриггеромзадержки, таккаксигнал на его выходе повторяет сигнал на входе в предыдущем такте. D-триггер получают из RS-триггера путём соединения двух входов иинвертированияодногоизних. Отличительнойособенностьюего является наличие одного информационного входа. Триггер может иметь также один информационный вход D и вход синхронизации С (тактируемый D-триггер). Наиболее широкое применение полу- чилитактируемыеD-триггеры, выполненныеналогическихэлементах И-НЕ. Схему D-триггера можно строить и на элементах НЕ и ИЛИ-НЕ( рис. 10.19, б) илиспомощьюсинхронногооднотактного RS-триггера ( рис. 10.19, в) . Его таблица переключений очень проста: триггер приобретает (при действии сигнала синхронизации С состояние, равное уровню входа D, и хранит его до действия сле-

264

Рис. 10.19. Условноеграфическоеобозначение(а), схеманалогическихэлементах (б), схема на основе синхронного RS-триггера (в) и временные диаграммы (г) одноконтактного D-триггера

дующего сигнала С. Условием чёткого переключения триггера, как и ранее, является неизменность сигнала на входе D (нуль или единица) в течение действия всего сигнала С. Такой триггер называют D-триггером со статическим управлением (синхронизацией). Временная диаграмма работы D-триггера показана на рис.10.19, г. Иногда D-триггер дополняют ещё одним входом V, разрешающим его переключение. Такой DV-триггер работаетаналогично D-триг- геру при подаче на вход V единичного сигнала.

Другой важной разновидностью одноступенчатого D-триггера является D-триггер с динамических входом синхронизации (изображён на рис. 10.20, а линией со стрелкой). Схема его сложна и не рассматривается. Таблица переключения этого триггера такая же, как D-триггера со статическим управлением.

t |

t+1 |

D |

Q |

0 |

0 |

1 |

1 |

На рис. 10.20, б временные диаграммы работы D-триггера.

265

Рис. 10.20. D-триггер с динамическим входом синхро- |

низации (а — условное графическое обозначение; б — |

временная диаграмма работы). |

Требование устойчивой работы схем вызывает в ряде случаев не- |

обходимость задержек в переключении триггеров. Это обеспечива- |

ется использованием, в частности, двухтактных (двухступенчатых) |

триггеров. Например, бывает необходимо и опрашивать состояние |

триггера, и переключать его в новое состояние. При использовании |

одноступенчатых триггеров может возникнуть ситуация неопреде- |

лённости, когда новое состояние триггера окажется логически зави- |

сящим от самого себя. При решении таких задач используют двух- |

ступенчатые MS-триггеры (master — ведущий, slave — ведомый). |

Такой триггер состоит из двух ступеней. Первая их них принимает |

информациюотвходнойлинии, автораяуправляетсявыходамипер- |

вой ступени. Синхросигналы поступают в ступени в разные момен- |

тывремени. Следовательно, вкаждыйконкретныймоментможетме- |

няться состояние только одной ступени. Полное переключение MS- |

триггера осуществляется за два шага (такта). В первом такте под |

действием сигнала происходит приём информации в триггер первой |

ступени, однако выходной сигнал (в схеме это выход второй ступе- |

ни) не изменяется. Когда все переходные процессы первой ступени |

заканчиваются, под действием следующего синхросигнала переклю- |

чается вторая ступень и весь триггер приобретает новое состояние. |

Двухтактными могут быть RS-, D-, Т-триггеры и др. Они обо- |

значаютсядвумябуквамиТвполепрямоугольника. Ихможнопред- |

ставитькаксоединениедвуходнотактныхD-триггеров, приёмвпер- |

266 |

вый из которых синхронизируется сигналом С и происходит при С |

= 1. На входе С второго (выходного) действует инверсия сигнала С, |

— |

т.е. С. Временные диаграммы на рис. 10.20, б показывают особен- |

ность работы триггера при переключении в 1, а затем в 0. Она зак- |

лючаетсявтом, чтоновоесостояниетриггерначинаетприобретать |

при спаде синхросигнала , т. е. при единичном значении его инвер- |

сии С. С этого момента происходит перепись состояния, приобре- |

тённого первым триггером, во второй. |

Т-триггеры |

T-триггеры, называемыетакжетриггерамисосчётнымвходом, спо- |

собны переключаться в противоположное состояние при новом еди- |

ничномзначенииинформационногосигналаТ. Онимогутбытьасин- |

хронными рис. (10.21, а, б) и синхронными рис. 10.22, в. При Т = 0 |

Рис. 10.21. Несинхронизируемый Т-триггер: |

а — схема с использованием RS-триггера; б — временная диаграмма |

Рис. 10.22. Синхронный Т-триггер (а) и его временная диаграмма (б) |

267 |

триггер сохраняет приобретённое ранее состояние, а приТ= 1, переключается. Момент переключения определяется типом триггера.

Т-триггерымогутбытьпостроенысиспользованиемрассмотрен- ныхвышеRS-триггеров. ЕслиудвухступенчатогоRS-триггерасоеди- нитьвходыR иS свыходамиQ и(Q— ) соответственно, авходсинхронизациииспользоватькаксчётный, тополучитсяпростейшийвариант несихронизируемогоТ-триггера. Извременнойдиаграммы(рис. 10, б) видно, чтосостояниевыходаQ неменяетсядотехпор, покадействие единичногосигналанавходеТнезаканчивается. Этопроисходитпотому, чтосначаламеняетсясостояниепервогокаскада, азатемпоотрицательномупереходу(позаднемуфронту) сигналаТвторого. Благодаря этому исключается возможность генерации сигналов из-за имеющихсявсхемеобратныхсвязей. Именнопоэтомуиспользование одноступенчатогоRS-триггеравтакойсхемеисключено.

Синхронный Т-триггер используется в тех случаях, когда последовательность единиц на входе необходимо представлять в виде потенциала, действующего в течение нескольких тактов. Запись в триггер происходит в момент подачи единичного сигнала на вход С (по переднему фронту входного импульса), а смена состояния на выходе, как и в предыдущем случае по отрицательному перепаду. Таким образом, схема ведёт счёт синхросигналов при Т = 1. При Т = 0 состояние триггера не меняется. Т-триггер можно построить на основе двухтактного D-триггера (путём соединения инверсного выхода триггера с собственным входом D). Выход Q будет изменяться в такой схеме при спаде сигнала Т (по заднему фронту).

JK-триггер

JK-триггер (рис. 10.23) такой триггер, называемый универсальным, имеет особые значения. Он является двухступенчатым и переключается по спаду синхросигнала С в соответствии с табл. 10.5.

Сигналы J и К во время действия синхросигнала С, как и во всех триггерах со статическим управлением, должны сохраняться неизменными. JK-триггер легко превратить в двухступенчатый D-триг- гер (рис. 10.23, б), двухступенчатый Т-триггер (рис. 10.23, в) и др.

268