- •Features

- •Disclaimer

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •D-/SDATA

- •UGND

- •UVCC

- •UCAP

- •RESET/PC1/dW

- •XTAL1

- •XTAL2/PC0

- •AVR CPU Core

- •Introduction

- •Status Register

- •Stack Pointer

- •TABLE 1.

- •TABLE 2.

- •AVR AT90USB82/162 Memories

- •I/O Memory

- •Clock Systems and their Distribution

- •Clock Switch

- •Exemple of use

- •Swith from external clock to RC clock

- •Switch from RC clock to external clock

- •Clock Sources

- •Default Clock Source

- •External Clock

- •Internal PLL for USB interface

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Watchdog Reset

- •USB Reset

- •Watchdog Timer

- •TABLE 2.

- •TABLE 2.

- •Interrupts

- •TABLE 2.

- •Introduction

- •Configuring the Pin

- •Toggling the Pin

- •Reading the Pin Value

- •TABLE 3.

- •Unconnected Pins

- •Alternate Port Functions

- •Register Description for I/O-Ports

- •Timer/Counter0 and Timer/Counter1 Prescalers

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Normal Mode

- •Fast PWM Mode

- •8-bit Timer/Counter Register Description

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Input Capture Unit

- •Noise Canceler

- •Force Output Compare

- •Normal Mode

- •Fast PWM Mode

- •16-bit Timer/Counter Register Description

- •TABLE 2.

- •TABLE 2.

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Overview

- •Clock Generation

- •External Clock

- •Frame Formats

- •Parity Bit Calculation

- •TABLE 2.

- •TABLE 3.

- •TABLE 4.

- •Parity Generator

- •TABLE 3.

- •TABLE 2.

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •TABLE 2.

- •Using MPCMn

- •Receiver Flow Control

- •Overview

- •Clock Generation

- •Frame Formats

- •TABLE 2.

- •Data Transfer

- •TABLE 3.

- •USB controller

- •Features

- •Block Diagram

- •Typical Application Implementation

- •Device mode

- •Bus Powered device

- •Introduction

- •Interrupts

- •Power modes

- •Idle mode

- •Power down

- •Freeze clock

- •Memory access capability

- •Memory management

- •PAD suspend

- •D+/D- Read/write

- •Registers description

- •USB general registers

- •USB Software Operating modes

- •USB Device Operating modes

- •Introduction

- •Power-on and reset

- •Endpoint reset

- •USB reset

- •Endpoint selection

- •Endpoint activation

- •Address Setup

- •Detach

- •Remote Wake-up

- •STALL request

- •Special consideration for Control Endpoints

- •STALL handshake and Retry mechanism

- •CONTROL endpoint management

- •Control Write

- •Control Read

- •Overview

- •“Manual” mode

- •Detailed description

- •IN endpoint management

- •“Manual” mode

- •Detailed description

- •Abort

- •Isochronous mode

- •Underflow

- •CRC Error

- •Overflow

- •Interrupts

- •Registers

- •USB device general registers

- •USB device endpoint registers

- •Characteristics

- •Analog Comparator

- •Application Section

- •Boot Reset Fuse

- •Simple Assembly Code Example for a Boot Loader

- •debugWIRE On-chip Debug System

- •Features

- •Overview

- •Physical Interface

- •Software Break Points

- •Limitations of debugWIRE

- •debugWIRE Related Register in I/O Memory

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Chip Erase

- •Reading the Flash

- •Reading the EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Maximum speed vs. VCC

- •Supply Current of IO modules

- •Example 1

- •Example 2

- •Example 3

- •Instruction Set Summary

- •Packaging Information

- •TQFP32

SPI Status Register –

SPSR

SPI Data Register –

SPDR

Data Modes

142

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

7 |

6 |

5 |

|

4 |

|

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

SPIF |

WCOL |

– |

|

– |

– |

– |

– |

SPI2X |

SPSR |

||

|

|

|

|

|

|

|

|

|

|

|

||

Read/Write |

R |

R |

R |

R |

R |

R |

R |

R/W |

|

|||

Initial Value |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

• Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF Flag is set. An interrupt is generated if SPIE in SPCR is set and global interrupts are enabled. If SS is an input and is driven low when the SPI is in Master mode, this will also set the SPIF Flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register with SPIF set, then accessing the SPI Data Register (SPDR).

• Bit 6 – WCOL: Write COLlision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared by first reading the SPI Status Register with WCOL set, and then accessing the SPI Data Register.

• Bit 5..1 – Res: Reserved Bits

These bits are reserved bits in the AT90USB82/162 and will always read as zero.

• Bit 0 – SPI2X: Double SPI Speed Bit

When this bit is written logic one the SPI speed (SCK Frequency) will be doubled when the SPI is in Master mode (see Table 58). This means that the minimum SCK period will be two CPU clock periods. When the SPI is configured as Slave, the SPI is only guaranteed to work at fosc/4 or lower.

The SPI interface on the AT90USB82/162 is also used for program memory and EEPROM downloading or uploading. See page 248 for serial programming and verification.

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

MSB |

|

|

|

|

|

|

LSB |

SPDR |

|

|

|

|

|

|

|

|

|

|

Read/Write |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

Initial Value |

X |

X |

X |

X |

X |

X |

X |

X |

Undefined |

The SPI Data Register is a read/write register used for data transfer between the Register File and the SPI Shift Register. Writing to the register initiates data transmission. Reading the register causes the Shift Register Receive buffer to be read.

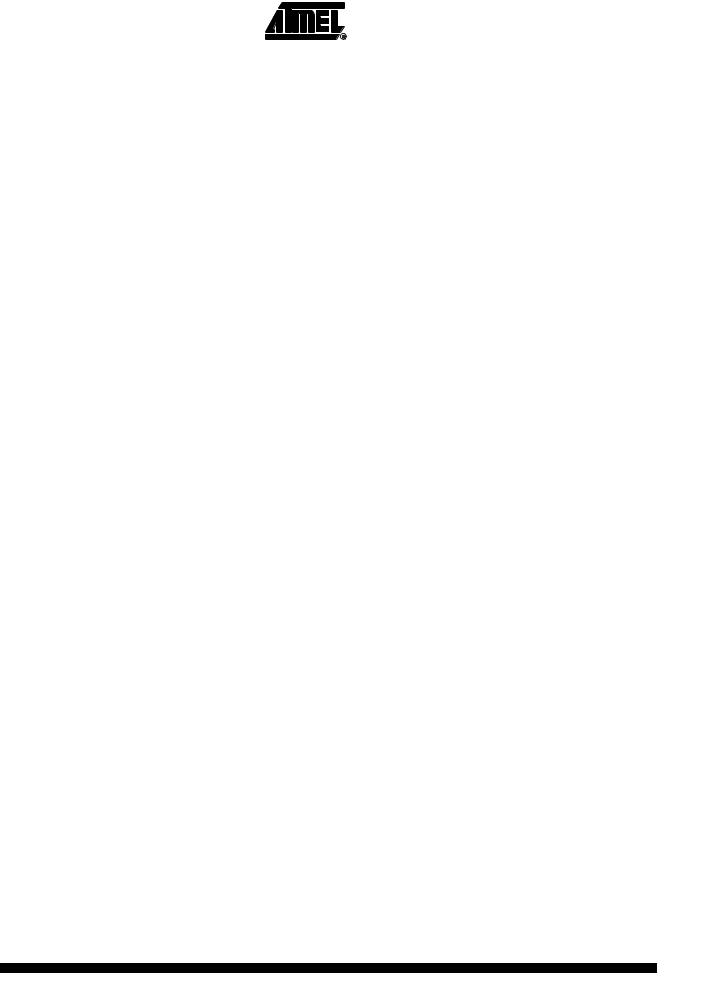

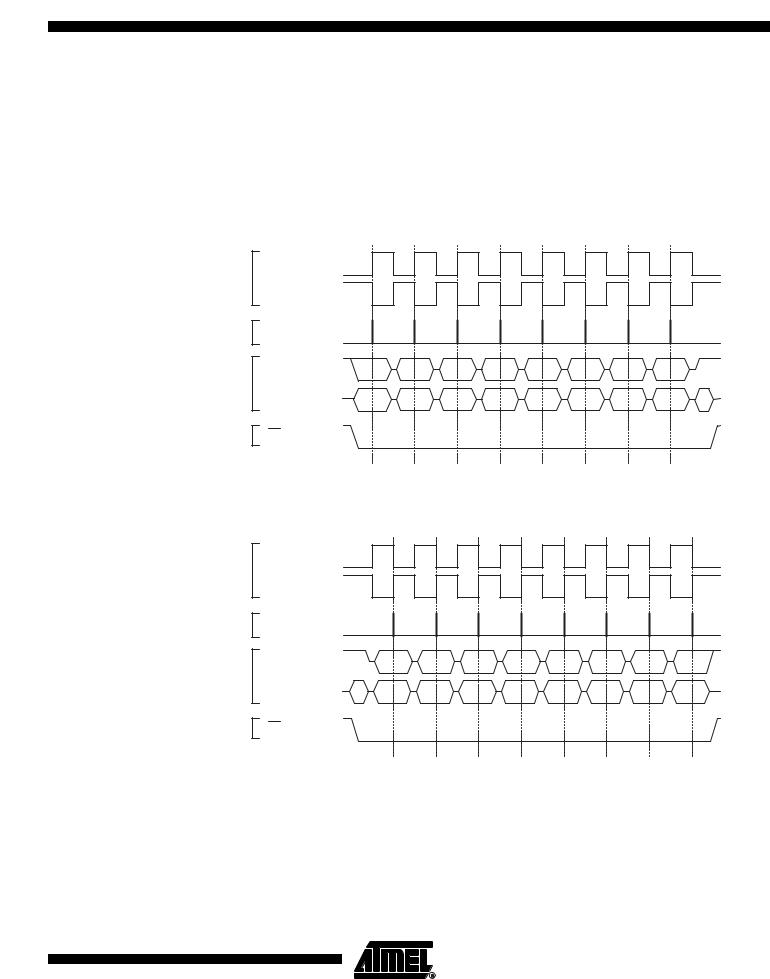

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 61 and Figure 62. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Table 56 and Table 57, as done below:

7707A–AVR–01/07

Table 59. CPOL Functionality

|

Leading Edge |

Trailing eDge |

SPI Mode |

|

|

|

|

CPOL=0, CPHA=0 |

Sample (Rising) |

Setup (Falling) |

0 |

|

|

|

|

CPOL=0, CPHA=1 |

Setup (Rising) |

Sample (Falling) |

1 |

|

|

|

|

CPOL=1, CPHA=0 |

Sample (Falling) |

Setup (Rising) |

2 |

|

|

|

|

CPOL=1, CPHA=1 |

Setup (Falling) |

Sample (Rising) |

3 |

|

|

|

|

Figure 61. SPI Transfer Format with CPHA = 0

SCK (CPOL = 0) mode 0

SCK (CPOL = 1) mode 2

SAMPLE I

MOSI/MISO

CHANGE 0

MOSI PIN

CHANGE 0

MISO PIN

SS

MSB first (DORD = 0) |

MSB |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

LSB |

LSB first (DORD = 1) |

LSB |

Bit 1 |

Bit 2 |

Bit 3 |

Bit 4 |

Bit 5 |

Bit 6 |

MSB |

Figure 62. SPI Transfer Format with CPHA = 1

SCK (CPOL = 0) mode 1

SCK (CPOL = 1) mode 3

SAMPLE I

MOSI/MISO

CHANGE 0

MOSI PIN

CHANGE 0

MISO PIN

SS

MSB first (DORD = 0) |

MSB |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

LSB |

LSB first (DORD = 1) |

LSB |

Bit 1 |

Bit 2 |

Bit 3 |

Bit 4 |

Bit 5 |

Bit 6 |

MSB |

143

7707A–AVR–01/07