- •Features

- •Disclaimer

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •D-/SDATA

- •UGND

- •UVCC

- •UCAP

- •RESET/PC1/dW

- •XTAL1

- •XTAL2/PC0

- •AVR CPU Core

- •Introduction

- •Status Register

- •Stack Pointer

- •TABLE 1.

- •TABLE 2.

- •AVR AT90USB82/162 Memories

- •I/O Memory

- •Clock Systems and their Distribution

- •Clock Switch

- •Exemple of use

- •Swith from external clock to RC clock

- •Switch from RC clock to external clock

- •Clock Sources

- •Default Clock Source

- •External Clock

- •Internal PLL for USB interface

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Watchdog Reset

- •USB Reset

- •Watchdog Timer

- •TABLE 2.

- •TABLE 2.

- •Interrupts

- •TABLE 2.

- •Introduction

- •Configuring the Pin

- •Toggling the Pin

- •Reading the Pin Value

- •TABLE 3.

- •Unconnected Pins

- •Alternate Port Functions

- •Register Description for I/O-Ports

- •Timer/Counter0 and Timer/Counter1 Prescalers

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Normal Mode

- •Fast PWM Mode

- •8-bit Timer/Counter Register Description

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Input Capture Unit

- •Noise Canceler

- •Force Output Compare

- •Normal Mode

- •Fast PWM Mode

- •16-bit Timer/Counter Register Description

- •TABLE 2.

- •TABLE 2.

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Overview

- •Clock Generation

- •External Clock

- •Frame Formats

- •Parity Bit Calculation

- •TABLE 2.

- •TABLE 3.

- •TABLE 4.

- •Parity Generator

- •TABLE 3.

- •TABLE 2.

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •TABLE 2.

- •Using MPCMn

- •Receiver Flow Control

- •Overview

- •Clock Generation

- •Frame Formats

- •TABLE 2.

- •Data Transfer

- •TABLE 3.

- •USB controller

- •Features

- •Block Diagram

- •Typical Application Implementation

- •Device mode

- •Bus Powered device

- •Introduction

- •Interrupts

- •Power modes

- •Idle mode

- •Power down

- •Freeze clock

- •Memory access capability

- •Memory management

- •PAD suspend

- •D+/D- Read/write

- •Registers description

- •USB general registers

- •USB Software Operating modes

- •USB Device Operating modes

- •Introduction

- •Power-on and reset

- •Endpoint reset

- •USB reset

- •Endpoint selection

- •Endpoint activation

- •Address Setup

- •Detach

- •Remote Wake-up

- •STALL request

- •Special consideration for Control Endpoints

- •STALL handshake and Retry mechanism

- •CONTROL endpoint management

- •Control Write

- •Control Read

- •Overview

- •“Manual” mode

- •Detailed description

- •IN endpoint management

- •“Manual” mode

- •Detailed description

- •Abort

- •Isochronous mode

- •Underflow

- •CRC Error

- •Overflow

- •Interrupts

- •Registers

- •USB device general registers

- •USB device endpoint registers

- •Characteristics

- •Analog Comparator

- •Application Section

- •Boot Reset Fuse

- •Simple Assembly Code Example for a Boot Loader

- •debugWIRE On-chip Debug System

- •Features

- •Overview

- •Physical Interface

- •Software Break Points

- •Limitations of debugWIRE

- •debugWIRE Related Register in I/O Memory

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Chip Erase

- •Reading the Flash

- •Reading the EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Maximum speed vs. VCC

- •Supply Current of IO modules

- •Example 1

- •Example 2

- •Example 3

- •Instruction Set Summary

- •Packaging Information

- •TQFP32

Watchdog Reset |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

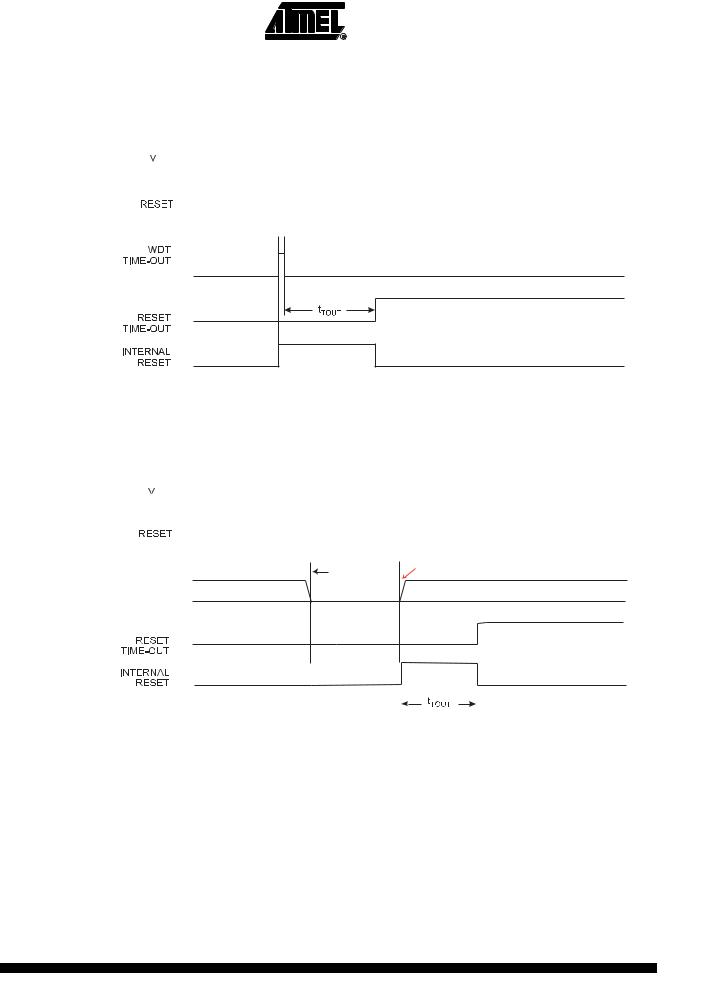

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On |

|||||||||

|

the falling edge of this pulse, the delay timer starts counting the Time-out period tTOUT. Refer to |

||||||||

|

on page 52 for details on operation of the Watchdog Timer. |

||||||||

|

Figure 25. Watchdog Reset During Operation |

||||||||

|

|

CC |

|

|

|||||

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CK

CK

USB Reset |

When the USB macro is enabled and configured with the USB reset MCU feature enabled, and |

||||

|

if a valid USB Reset signalling is detected, the microcontroller is reset unless the USB macro |

||||

|

that remains enabled. This allows the device to stay attached to the bus during and after the |

||||

|

reset, while enhancing firmware reliability. |

||||

|

Figure 26. USB Reset During Operation |

||||

|

|

CC |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

(USB Lines)

DP

DM

USB Traffic

t

USBRSTMIN

End of Reset

USB Traffic

MCU Status Register – The MCU Status Register provides information on which reset source caused an MCU reset.

MCUSR |

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

– |

– |

USBRF |

– |

WDRF |

BORF |

EXTRF |

PORF |

MCUSR |

|

Read/Write |

R |

R |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

|

|

Initial Value |

0 |

0 |

0 |

See Bit Description |

|

|

|

|

|

• Bit 7-6 – Res: Reserved Bit

These bits are reserved and will always read as zero.

• Bit 5 – USBRF: USB Reset Flag

This bit is set if a USB Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

• Bit 4– Res: Reserved Bit

50

7707A–AVR–01/07

This bit is reserved.

• Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

• Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

• Bit 1 – EXTRF: External Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

• Bit 0 – PORF: Power-on Reset Flag

This bit is set if a Power-on Reset occurs. The bit is reset only by writing a logic zero to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read and then Reset the MCUSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags.

Internal Voltage |

AT90USB82/162 features an internal bandgap reference. This reference is used for Brown-out |

||||||||

Reference |

Detection, and it can be used as an input to the Analog Comparator or the ADC. |

|

|

||||||

Voltage Reference |

The voltage reference has a start-up time that may influence the way it should be used. The |

||||||||

Enable Signals and |

start-up time is given in Table 18. To save power, the reference is not always turned on. The ref- |

||||||||

Start-up Time |

erence is on during the following situations: |

|

|

|

|

|

|

|

|

|

1. When the BOD is enabled (by programming the BODLEVEL [2..0] Fuse). |

|

|

||||||

|

2. When the bandgap reference is connected to the Analog Comparator (by setting the |

||||||||

|

ACBG bit in ACSR). |

|

|

|

|

|

|

|

|

|

3. When the ADC is enabled. |

|

|

|

|

|

|

|

|

|

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the user |

||||||||

|

must always allow the reference to start up before the output from the Analog Comparator or |

||||||||

|

ADC is used. To reduce power consumption in Power-down mode, the user can avoid the three |

||||||||

|

conditions above to ensure that the reference is turned off before entering Power-down mode. |

||||||||

|

Table 18. Internal Voltage Reference Characteristics(1) |

|

|

|

|

|

|

||

|

Symbol |

Parameter |

Condition |

Min |

Typ |

Max |

|

Units |

|

|

|

|

|

|

|

|

|

|

|

|

VBG |

Bandgap reference voltage |

TBD |

TBD |

1.1 |

TBD |

|

V |

|

|

tBG |

Bandgap reference start-up time |

TBD |

|

40 |

70 |

|

µs |

|

|

IBG |

Bandgap reference current |

TBD |

|

10 |

TBD |

|

µA |

|

|

consumption |

|

|

|

|||||

|

Note: 1. |

Values are guidelines only. Actual values are TBD. |

|

|

|

|

|

|

|

51

7707A–AVR–01/07