- •Features

- •1. Pin Configurations

- •2. Overview

- •2.1 Block Diagram

- •2.2 Automotive Quality Grade

- •2.3 Pin Descriptions

- •2.3.3 Port B (PB5..PB0)

- •2.3.4 RESET

- •3. About Code Examples

- •4. AVR CPU Core

- •4.1 Introduction

- •4.2 Architectural Overview

- •4.4 Status Register

- •4.5 General Purpose Register File

- •4.6 Stack Pointer

- •4.7 Instruction Execution Timing

- •4.8 Reset and Interrupt Handling

- •4.8.1 Interrupt Response Time

- •5. AVR ATtiny25/45/85 Memories

- •5.2 SRAM Data Memory

- •5.2.1 Data Memory Access Times

- •5.3 EEPROM Data Memory

- •5.3.1 EEPROM Read/Write Access

- •5.3.6 Atomic Byte Programming

- •5.3.7 Split Byte Programming

- •5.3.8 Erase

- •5.3.9 Write

- •5.3.10 Preventing EEPROM Corruption

- •5.4 I/O Memory

- •6. System Clock and Clock Options

- •6.1 Clock Systems and their Distribution

- •6.2 Clock Sources

- •6.3 Default Clock Source

- •6.4 Crystal Oscillator

- •6.6 Calibrated Internal RC Oscillator

- •6.7 External Clock

- •6.8 128 kHz Internal Oscillator

- •6.9 Clock Output Buffer

- •6.10 System Clock Prescaler

- •6.10.2 Switching Time

- •7. Power Management and Sleep Modes

- •7.1 Idle Mode

- •7.2 ADC Noise Reduction Mode

- •7.4 Power Reduction Register

- •7.5 Minimizing Power Consumption

- •7.5.1 Analog to Digital Converter

- •7.5.2 Analog Comparator

- •7.5.4 Internal Voltage Reference

- •7.5.5 Watchdog Timer

- •7.5.6 Port Pins

- •8. System Control and Reset

- •8.0.1 Resetting the AVR

- •8.0.2 Reset Sources

- •8.0.3 Power-on Reset

- •8.0.4 External Reset

- •8.0.6 Watchdog Reset

- •8.1 Internal Voltage Reference

- •8.2 Watchdog Timer

- •8.3 Timed Sequences for Changing the Configuration of the Watchdog Timer

- •8.3.1 Safety Level 1

- •8.3.2 Safety Level 2

- •9. Interrupts

- •9.1 Interrupt Vectors in ATtiny25/45/85

- •10. I/O Ports

- •10.1 Introduction

- •10.2 Ports as General Digital I/O

- •10.2.1 Configuring the Pin

- •10.2.2 Toggling the Pin

- •10.2.3 Switching Between Input and Output

- •10.2.4 Reading the Pin Value

- •10.2.5 Digital Input Enable and Sleep Modes

- •10.2.6 Unconnected Pins

- •10.3 Alternate Port Functions

- •10.3.2 Alternate Functions of Port B

- •11. External Interrupts

- •12. 8-bit Timer/Counter0 with PWM

- •12.1 Overview

- •12.1.1 Registers

- •12.1.2 Definitions

- •12.2 Timer/Counter Clock Sources

- •12.3 Counter Unit

- •12.4 Output Compare Unit

- •12.4.1 Force Output Compare

- •12.4.2 Compare Match Blocking by TCNT0 Write

- •12.4.3 Using the Output Compare Unit

- •12.5 Compare Match Output Unit

- •12.5.1 Compare Output Mode and Waveform Generation

- •12.6 Modes of Operation

- •12.6.1 Normal Mode

- •12.6.2 Clear Timer on Compare Match (CTC) Mode

- •12.6.3 Fast PWM Mode

- •12.6.4 Phase Correct PWM Mode

- •12.7 Timer/Counter Timing Diagrams

- •13. Timer/Counter Prescaler

- •13.0.1 Prescaler Reset

- •13.0.2 External Clock Source

- •14. 8-bit Timer/Counter1

- •14.1 Timer/Counter1

- •14.1.1 Timer/Counter1 Control Register - TCCR1

- •14.1.2 General Timer/Counter1 Control Register - GTCCR

- •14.1.3 Timer/Counter1 - TCNT1

- •14.1.4 Timer/Counter1 Output Compare RegisterA - OCR1A

- •14.1.5 Timer/Counter1 Output Compare RegisterB - OCR1B

- •14.1.6 Timer/Counter1 Output Compare RegisterC - OCR1C

- •14.1.7 Timer/Counter Interrupt Mask Register - TIMSK

- •14.1.8 Timer/Counter Interrupt Flag Register - TIFR

- •14.1.9 PLL Control and Status Register - PLLCSR

- •14.1.10 Timer/Counter1 Initialization for Asynchronous Mode

- •14.1.11 Timer/Counter1 in PWM Mode

- •15. 8-bit Timer/Counter1 in ATtiny15 Mode

- •15.1 Timer/Counter1 Prescaler

- •15.2 Timer/Counter1

- •15.2.2 Timer/Counter1 Control Register - TCCR1

- •15.2.3 General Timer/Counter1 Control Register - GTCCR

- •15.2.4 Timer/Counter1 - TCNT1

- •15.2.5 Timer/Counter1 Output Compare RegisterA - OCR1A

- •15.2.6 Timer/Counter1 Output Compare Register C - OCR1C

- •15.2.7 Timer/Counter Interrupt Flag Register - TIFR

- •15.2.8 PLL Control and Status Register - PLLCSR

- •15.2.9 Timer/Counter1 in PWM Mode

- •16. Dead Time Generator

- •16.0.1 Timer/Counter1 Dead Time Prescaler register 1 - DTPS1

- •16.0.2 Timer/Counter1 Dead Time A - DT1A

- •16.0.3 Timer/Counter1 Dead Time B - DT1B

- •17.1 Overview

- •17.2 Functional Descriptions

- •17.2.2 SPI Master Operation Example

- •17.2.3 SPI Slave Operation Example

- •17.2.5 Start Condition Detector

- •17.3 Alternative USI Usage

- •17.3.4 Edge Triggered External Interrupt

- •17.3.5 Software Interrupt

- •17.4 USI Register Descriptions

- •18. Analog Comparator

- •18.1 Analog Comparator Multiplexed Input

- •19. Analog to Digital Converter

- •19.1 Features

- •19.2 Operation

- •19.3 Starting a Conversion

- •19.4 Prescaling and Conversion Timing

- •19.5 Changing Channel or Reference Selection

- •19.5.1 ADC Input Channels

- •19.5.2 ADC Voltage Reference

- •19.6 ADC Noise Canceler

- •19.6.1 Analog Input Circuitry

- •19.6.2 Analog Noise Canceling Techniques

- •19.6.3 ADC Accuracy Definitions

- •19.7 ADC Conversion Result

- •19.7.1 Single Ended Conversion

- •19.7.2 Unipolar Differential Conversion

- •19.7.3 Bipolar Differential Conversion

- •19.7.4 Temperature Measurement (Preliminary description)

- •19.7.7.1 ADLAR = 0

- •19.7.7.2 ADLAR = 1

- •20. debugWIRE On-chip Debug System

- •20.1 Features

- •20.2 Overview

- •20.3 Physical Interface

- •20.4 Software Break Points

- •20.5 Limitations of debugWIRE

- •20.6 debugWIRE Related Register in I/O Memory

- •21. Self-Programming the Flash

- •21.0.1 Performing Page Erase by SPM

- •21.0.2 Filling the Temporary Buffer (Page Loading)

- •21.0.3 Performing a Page Write

- •21.1.2 EEPROM Write Prevents Writing to SPMCSR

- •21.1.3 Reading the Fuse and Lock Bits from Software

- •21.1.4 Preventing Flash Corruption

- •21.1.5 Programming Time for Flash when Using SPM

- •22. Memory Programming

- •22.1 Program And Data Memory Lock Bits

- •22.2 Fuse Bytes

- •22.2.1 Latching of Fuses

- •22.3 Signature Bytes

- •22.3.1 ATtiny25 Signature Bytes

- •22.3.2 ATtiny45 Signature Bytes

- •22.3.3 ATtiny85 Signature Bytes

- •22.4 Calibration Byte

- •22.5 Page Size

- •22.6 Serial Downloading

- •22.6.1 Serial Programming Algorithm

- •22.6.2 Serial Programming Characteristics

- •22.7 High-voltage Serial Programming

- •22.8.2 Considerations for Efficient Programming

- •22.8.3 Chip Erase

- •22.8.4 Programming the Flash

- •22.8.5 Programming the EEPROM

- •22.8.6 Reading the Flash

- •22.8.7 Reading the EEPROM

- •22.8.8 Programming and Reading the Fuse and Lock Bits

- •22.8.9 Reading the Signature Bytes and Calibration Byte

- •23. Electrical Characteristics

- •23.1 Absolute Maximum Ratings*

- •23.2 External Clock Drive Waveforms

- •23.3 External Clock Drive

- •23.5 Calibrated RC Oscillator Accuracy

- •24. Typical Characteristics

- •24.1 Active Supply Current

- •24.2 Idle Supply Current

- •24.2.1 Using the Power Reduction Register

- •24.2.1.1 Example 1

- •24.5 Pin Driver Strength

- •24.6 Pin Thresholds and Hysteresis

- •24.7 BOD Thresholds and Analog Comparator Offset

- •24.8 Internal Oscillator Speed

- •24.9 Current Consumption of Peripheral Units

- •24.10 Current Consumption in Reset and Reset Pulse width

- •24.11 Analog to Digital Converter

- •25. Register Summary

- •26. Instruction Set Summary

- •27. Ordering Information

- •28. Packaging Information

- •29. Document Revision History

- •30. Errata

- •30.1 ATtiny25/45/85 Rev. A

ATtiny25/45/85 Auto

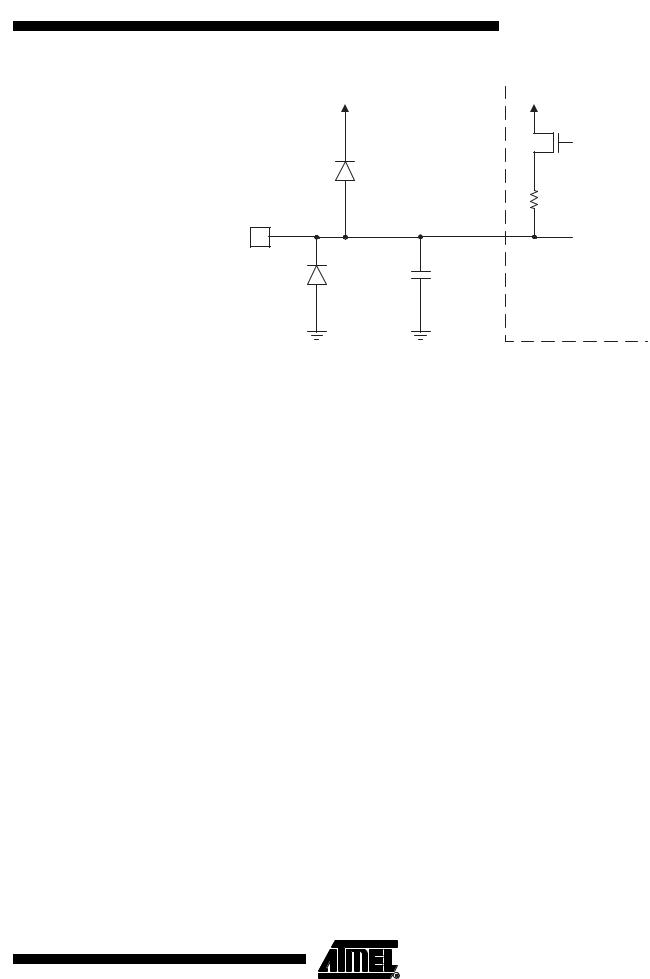

Figure 10-1. I/O Pin Equivalent Schematic

|

Rpu |

Pxn |

Logic |

Cpin |

See Figure |

|

"General Digital I/O" for |

|

Details |

All registers and bit references in this section are written in general form. A lower case “x” represents the numbering letter for the port, and a lower case “n” represents the bit number. However, when using the register or bit defines in a program, the precise form must be used. For example, PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in “Register Description for I/O-Ports” on page 57.

Three I/O memory address locations are allocated for each port, one each for the Data Register

– PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register and the Data Direction Register are read/write. However, writing a logic one to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register. In addition, the Pull-up Disable – PUD bit in MCUCR disables the pull-up function for all pins in all ports when set.

Using the I/O port as General Digital I/O is described in “Ports as General Digital I/O” on page 47. Most port pins are multiplexed with alternate functions for the peripheral features on the device. How each alternate function interferes with the port pin is described in “Alternate Port Functions” on page 52. Refer to the individual module sections for a full description of the alternate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

10.2Ports as General Digital I/O

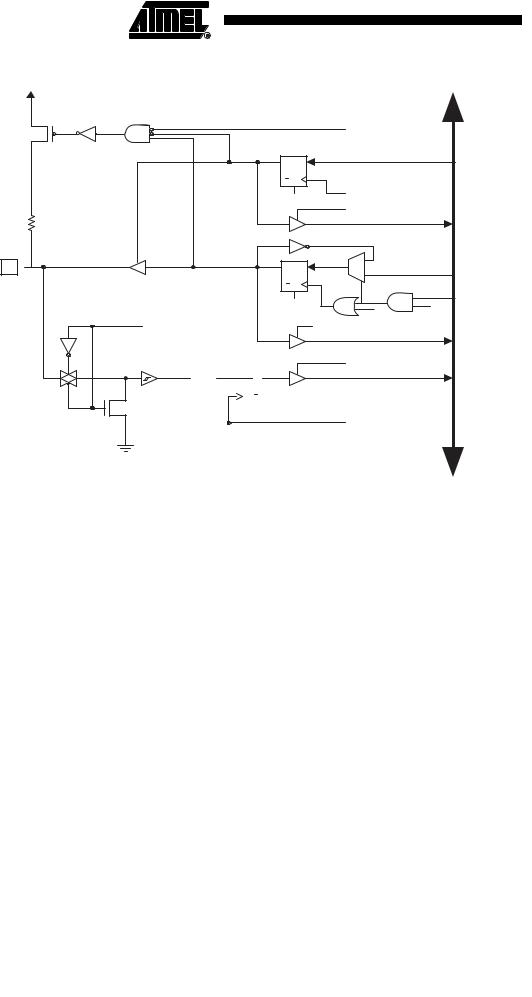

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 10-2 shows a functional description of one I/O-port pin, here generically called Pxn.

47

7598C–AVR–09/06

Figure 10-2. General Digital I/O(1)

Pxn

SLEEP

SYNCHRONIZER

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

Q |

|

|

|

|

|

|

|

D Q |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PINxn |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

L |

Q |

|

|

|

|

|

|

|

|

|

|

Q |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PUD |

|

|

Q |

D |

|

|

|

DDxn |

|

|

||

Q CLR |

|

|

|

|

RESET |

WDx |

|

||

RDx |

|

|||

|

|

|

||

Q |

D |

1 |

BUS |

|

|

DATA |

|||

PORTxn |

0 |

|||

|

||||

Q CLR |

|

|

|

|

RESET |

|

WPx |

||

|

|

WRx |

||

|

|

|

||

|

|

RRx |

|

|

|

|

RPx |

|

|

|

|

clk I/O |

|

|

PUD: |

PULLUP DISABLE |

WDx: |

WRITE DDRx |

RDx: |

READ DDRx |

||

SLEEP: |

SLEEP CONTROL |

WRx: |

WRITE PORTx |

clkI/O: |

I/O CLOCK |

RRx: |

READ PORTx REGISTER |

|

|

RPx: |

READ PORTx PIN |

|

|

WPx: |

WRITE PINx REGISTER |

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clkI/O,

SLEEP, and PUD are common to all ports.

10.2.1Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in “Register Description for I/O-Ports” on page 57, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

10.2.2Toggling the Pin

Writing a logic one to PINxn toggles the value of PORTxn, independent on the value of DDRxn. Note that the SBI instruction can be used to toggle one single bit in a port.

48 ATtiny25/45/85 Auto

7598C–AVR–09/06

ATtiny25/45/85 Auto

10.2.3Switching Between Input and Output

When switching between tri-state ({DDxn, PORTxn} = 0b00) and output high ({DDxn, PORTxn} = 0b11), an intermediate state with either pull-up enabled {DDxn, PORTxn} = 0b01) or output low ({DDxn, PORTxn} = 0b10) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the MCUCR Register can be set to disable all pull-ups in all ports.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ({DDxn, PORTxn} = 0b00) or the output high state ({DDxn, PORTxn} = 0b10) as an intermediate step.

Table 10-1 summarizes the control signals for the pin value.

Table 10-1. Port Pin Configurations

|

|

PUD |

|

|

|

DDxn |

PORTxn |

(in MCUCR) |

I/O |

Pull-up |

Comment |

|

|

|

|

|

|

0 |

0 |

X |

Input |

No |

Tri-state (Hi-Z) |

|

|

|

|

|

|

0 |

1 |

0 |

Input |

Yes |

Pxn will source current if ext. pulled low. |

|

|

|

|

|

|

0 |

1 |

1 |

Input |

No |

Tri-state (Hi-Z) |

|

|

|

|

|

|

1 |

0 |

X |

Output |

No |

Output Low (Sink) |

|

|

|

|

|

|

1 |

1 |

X |

Output |

No |

Output High (Source) |

|

|

|

|

|

|

10.2.4Reading the Pin Value

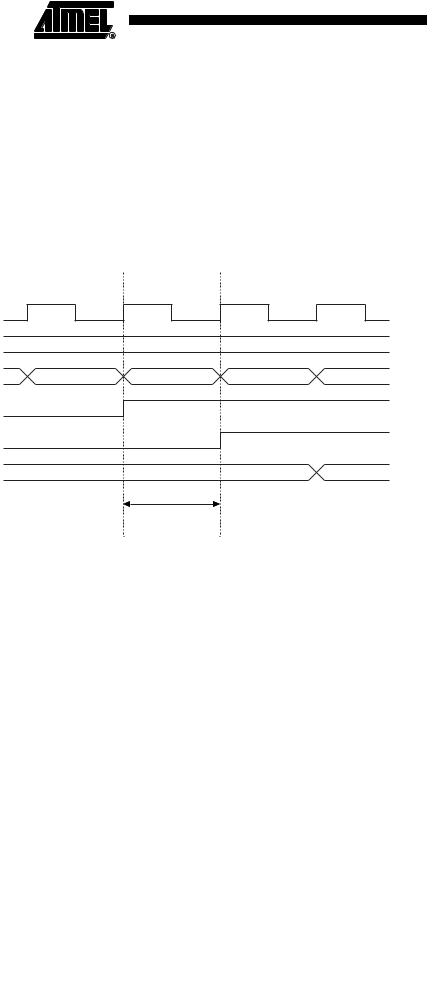

Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit. As shown in Figure 10-2, the PINxn Register bit and the preceding latch constitute a synchronizer. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay. Figure 10-3 shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted tpd,max and tpd,min respectively.

Figure 10-3. Synchronization when Reading an Externally Applied Pin value

SYSTEM CLK

INSTRUCTIONS

SYNC LATCH

PINxn

r17

XXX |

XXX |

in r17, PINx |

0x00 |

0xFF |

tpd, max

tpd, min

49

7598C–AVR–09/06

Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the “SYNC LATCH” signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed between ½ and 1½ system clock period depending upon the time of assertion.

When reading back a software assigned pin value, a nop instruction must be inserted as indicated in Figure 10-4. The out instruction sets the “SYNC LATCH” signal at the positive edge of the clock. In this case, the delay tpd through the synchronizer is one system clock period.

Figure 10-4. Synchronization when Reading a Software Assigned Pin Value

SYSTEM CLK

r16

INSTRUCTIONS

SYNC LATCH

PINxn

r17

0xFF

out PORTx, r16 |

nop |

in r17, PINx |

0x00 |

0xFF |

tpd

The following code example shows how to set port B pins 0 and 1 high, 2 and 3 low, and define the port pins from 4 to 5 as input with a pull-up assigned to port pin 4. The resulting pin values are read back again, but as previously discussed, a nop instruction is included to be able to read back the value recently assigned to some of the pins.

50 ATtiny25/45/85 Auto

7598C–AVR–09/06