- •Features

- •Pin Configurations

- •Disclaimer

- •Overview

- •Block Diagram

- •AT90S8535 Compatibility

- •Pin Descriptions

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •RESET

- •XTAL1

- •XTAL2

- •AVCC

- •AREF

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Default Clock Source

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Timer/Counter Oscillator

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Extended Standby Mode

- •Analog-to-Digital Converter

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 0

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •I/O-Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions Of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •Port A Data Register – PORTA

- •Port B Data Register – PORTB

- •Port C Data Register – PORTC

- •Port D Data Register – PORTD

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •8-bit Timer/Counter2 with PWM and Asynchronous Operation

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Timer/Counter Prescaler

- •Slave Mode

- •Master Mode

- •SPI Control Register – SPCR

- •SPI Status Register – SPSR

- •SPI Data Register – SPDR

- •Data Modes

- •USART

- •Overview

- •AVR USART vs. AVR UART – Compatibility

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 5 to 8 Data Bits

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Two-wire Serial Interface

- •Features

- •TWI Terminology

- •Electrical Interconnection

- •Transferring Bits

- •START and STOP Conditions

- •Address Packet Format

- •Data Packet Format

- •Overview of the TWI Module

- •SCL and SDA Pins

- •Bit Rate Generator Unit

- •Bus Interface Unit

- •Address Match Unit

- •Control Unit

- •TWI Register Description

- •TWI Bit Rate Register – TWBR

- •TWI Control Register – TWCR

- •TWI Status Register – TWSR

- •TWI Data Register – TWDR

- •Using the TWI

- •Transmission Modes

- •Master Transmitter Mode

- •Master Receiver Mode

- •Slave Receiver Mode

- •Slave Transmitter Mode

- •Miscellaneous States

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Operation

- •Starting a Conversion

- •Differential Gain Channels

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •ADLAR = 0

- •ADLAR = 1

- •Boot Loader Features

- •Application Section

- •BLS – Boot Loader Section

- •Boot Loader Lock Bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock Bits by SPM

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Two-wire Serial Interface Characteristics

- •ADC Characteristics – Preliminary Data

- •Instruction Set Summary

- •Ordering Information(1)

- •Packaging Information

- •Data Sheet Change Log for ATmega8535

- •Changes from Rev. 2502A-06/02 to Rev. 2502B-09/02

- •Table of Contents

ATmega8535(L)

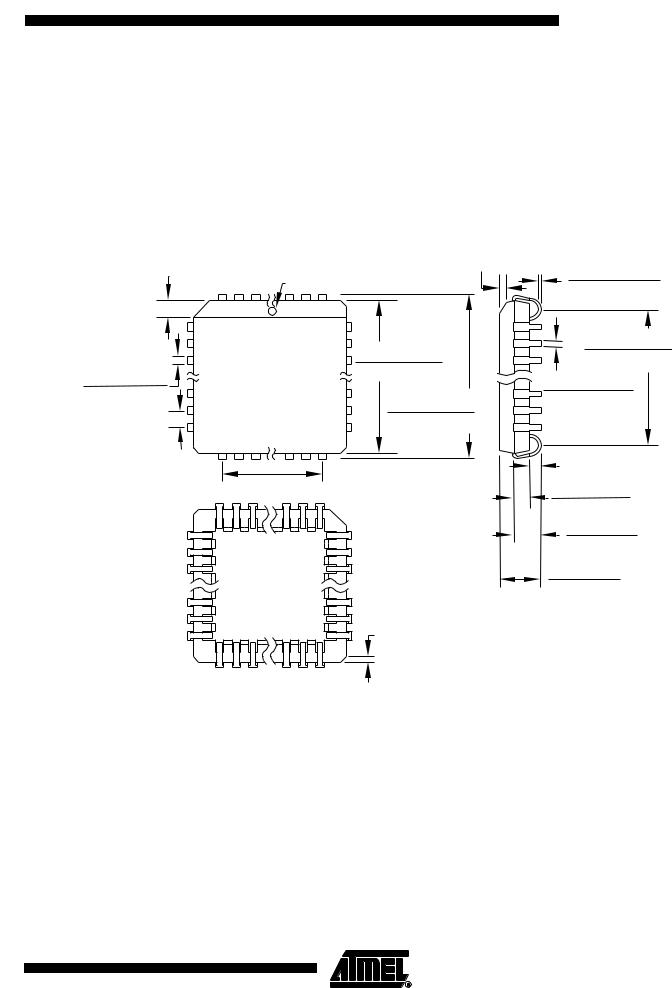

Packaging Information

44A

44-lead, Thin (1.0mm) Plastic Quad Flat Package (TQFP), 10x10mm body, 2.0mm footprint, 0.8mm pitch. Dimension in Millimeters and (Inches)*

JEDEC STANDARD MS-026 ACB

PIN 1 ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12.25(0.482) SQ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11.75(0.462) |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN 1 |

|

|

0.45(0.018) |

||||||||||||||||||||||||||||||

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

0.80(0.0315) BSC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.30(0.012) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10.10(0.394) SQ 9.90(0.386)

1.20(0.047) MAX

0.20(0.008) 0˚~7˚ 0.09(0.004)

0.75(0.030) 0.15(0.006) 0.45(0.018) 0.05(0.002)

*Controlling dimension: millimetter

REV. A 04/11/2001

267

2502B–AVR–09/02

40P6

40-lead, Plastic Dual Inline Parkage (PDIP), 0.600" wide

Demension in Millimeters and (Inches)* JEDEC STANDARD MS-011 AC

52.71(2.075)

51.94(2.045) PIN 1

48.26(1.900) REF

4.83(0.190)MAX

SEATING

PLANE

3.56(0.140) 3.05(0.120)

1.65(0.065)

2.54(0.100)BSC 1.27(0.050)

15.88(0.625)

15.24(0.600)

13.97(0.550)

13.46(0.530)

0.38(0.015)MIN

0.56(0.022)

0.38(0.015)

0.38(0.015) |

|

|

|

|

|

|

|

|

|

|

|

|

|

0º ~ 15º REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.20(0.008) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

17.78(0.700)MAX |

|

|

||||||||

|

|

|

|

|

|||||||||||

*Controlling dimension: Inches |

|||||||||||||||

REV. A 04/11/2001

268 ATmega8535(L)

2502B–AVR–09/02

ATmega8535(L)

44J

44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) Dimensions in Milimeters and (Inches)*

JEDEC STANDARD MS-018 AC

1.14(0.045) X 45˚ |

PIN NO. 1 |

1.14(0.045) X 45˚ |

0.318(0.0125) |

|

|||

|

IDENTIFY |

|

0.191(0.0075) |

|

|

|

|

|

16.70(0.656) |

16.00(0.630)SQ |

|

0.813(0.032) |

16.50(0.650)SQ |

15.00(0.590) |

|

0.533(0.021) |

|||

0.660(0.026) |

|

17.70(0.695) |

0.330(0.013) |

|

|

||

|

|

SQ |

|

|

|

17.40(0.685) |

|

1.27(0.050) TYP |

12.70(0.500) REF SQ |

0.50(0.020)MIN |

|

|

|||

|

2.11(0.083) |

||

|

|

|

|

|

|

|

1.57(0.062) |

|

|

|

3.05(0.120) |

|

|

|

2.29(0.090) |

|

|

|

4.57(0.180) |

|

|

|

4.19(0.165) |

|

|

0.51(0.020)MAX 45˚ MAX (3X) |

|

*Controlling dimensions: Inches

REV. A 04/11/2001

269

2502B–AVR–09/02

44M1-A

D

D

Marked pin#1 identifier

Marked pin#1 identifier

TOP VIEW

L

D2

D2

E2

b |

e |

|

BOTTOM VIEW |

E

PLANE

PLANE

SEATING

A1

A1

A3

A3

A

SIDE VIEW

PIN #1 CORNER

PIN #1 CORNER

COMMON DIMENSIONS

(*Unit of Measure = mm)

SYMBOL |

MIN |

NOM |

|

MAX NOTE |

|

|

|

|

|

A |

0.80 |

0.90 |

|

1.00 |

|

|

|

|

|

A1 |

0.00 |

0.02 |

|

0.05 |

|

|

|

|

|

A3 |

|

0.25 REF |

|

|

b |

0.18 |

0.23 |

|

0.30 |

|

|

|

|

|

D |

|

7.00 BSC |

|

|

|

|

|

|

|

D2 |

2.25 |

4.70 |

|

5.25 |

E |

|

7.00 BSC |

|

|

|

|

|

|

|

E2 |

2.25 |

4.70 |

|

5.25 |

|

|

|

|

|

e |

|

0.50 BSC |

|

|

|

|

|

|

|

L |

0.35 |

0.55 |

|

0.75 |

|

|

|

|

|

NOTE 1. JEDEC STANDARD MO-220, Fig 1 (Saw Singulation), VKKD-1

|

|

|

07/23/01 |

|

2325 Orchard Parkway TITLE |

44M1, 44-pad ,7 x 7 x 1.0 mm body, lead pitch 0.50mm |

DRAWING NO. REV |

||

R San Jose, CA 95131 |

44M1 |

A |

||

Micro lead frame package (MLF) |

||||

270 ATmega8535(L)

2502B–AVR–09/02