- •Features

- •Pin Configurations

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port A (PA2..PA0)

- •Port B (PB7..PB0)

- •Port D (PD6..PD0)

- •RESET

- •XTAL1

- •XTAL2

- •Disclaimer

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •Atomic Byte Programming

- •Split Byte Programming

- •Erase

- •Write

- •I/O Memory

- •General Purpose I/O Registers

- •Clock Systems and their Distribution

- •Clock Sources

- •Default Clock Source

- •Crystal Oscillator

- •External Clock

- •Idle Mode

- •Power-down Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Interrupts

- •I/O-Ports

- •Introduction

- •Configuring the Pin

- •Toggling the Pin

- •Reading the Pin Value

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions of Port B

- •Alternate Functions of Port D

- •Register Description for I/O-Ports

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •USART

- •Overview

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 5 to 8 Data Bit

- •Sending Frames with 9 Data Bit

- •Parity Generator

- •Disabling the Transmitter

- •Receiving Frames with 5 to 8 Data Bits

- •Receiving Frames with 9 Data Bits

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Overview

- •Functional Descriptions

- •Three-wire Mode

- •SPI Slave Operation Example

- •Two-wire Mode

- •Start Condition Detector

- •Alternative USI Usage

- •4-bit Counter

- •12-bit Timer/Counter

- •Software Interrupt

- •Analog Comparator

- •debugWIRE On-chip Debug System

- •Features

- •Overview

- •Physical Interface

- •Software Break Points

- •Limitations of debugWIRE

- •debugWIRE Related Register in I/O Memory

- •Performing a Page Write

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Page Size

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Active Supply Current

- •Idle Supply Current

- •Power-down Supply Current

- •Standby Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Errata

- •ATtiny2313 Rev B

- •ATtiny2313 Rev A

- •Changes from Rev. 2514F-08/04 to Rev. 2514G-10/04

- •Changes from Rev. 2514F-08/04 to Rev. 2514G-10/04

- •Changes from Rev. 2514E-04/04 to Rev. 2514F-08/04

- •Changes from Rev. 2514D-03/04 to Rev. 2514E-04/04

- •Changes from Rev. 2514C-12/03 to Rev. 2514D-03/04

- •Changes from Rev. 2514B-09/03 to Rev. 2514C-12/03

- •Changes from Rev. 2514A-09/03 to Rev. 2514B-09/03

- •Table of Contents

ATtiny2313/V

ATtiny2313/V

debugWIRE On-chip Debug System

Features

•Complete Program Flow Control

•Emulates All On-chip Functions, Both Digital and Analog, except RESET Pin

•Real-time Operation

•Symbolic Debugging Support (Both at C and Assembler Source Level, or for other HLLs)

•Unlimited Number of Program Break Points (Using Software Break Points)

•Non-intrusive Operation

•Electrical Characteristics Identical to Real Device

•Automatic Configuration System

•High-Speed Operation

•Programming of Non-volatile Memories

Overview |

The debugWIRE On-chip debug system uses a One-wire, bi-directional interface to con- |

|

trol the program flow, execute AVR instructions in the CPU and to program the different |

|

non-volatile memories. |

Physical Interface |

When the debugWIRE Enable (DWEN) Fuse is programmed and Lock bits are unpro- |

|

grammed, the debugWIRE system within the target device is activated. The RESET port |

|

pin is configured as a wire-AND (open-drain) bi-directional I/O pin with pull-up enabled |

|

and becomes the communication gateway between target and emulator. |

|

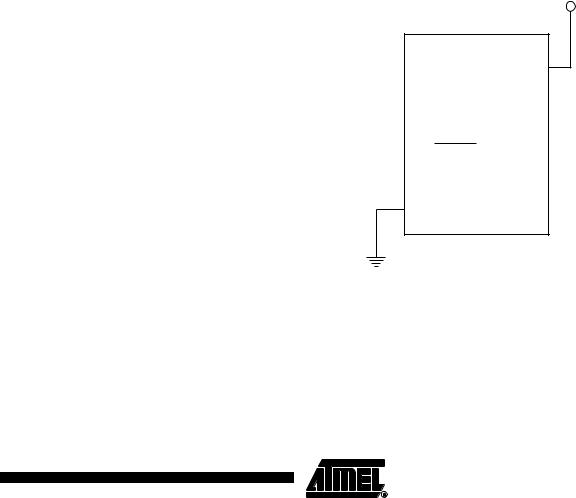

Figure 67. The debugWIRE Setup |

|

1.8 - 5.5V |

VCC

dW

dW(RESET)

dW(RESET)

GND

Figure 67 shows the schematic of a target MCU, with debugWIRE enabled, and the emulator connector. The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses.

When designing a system where debugWIRE will be used, the following observations must be made for correct operation:

•Pull-Up resistor on the dW/(RESET) line must be larger than 10k. However, the pullup resistor is optional.

•Connecting the RESET pin directly to VCC will not work.

151

2543H–AVR–02/05