- •Features

- •Pin Configurations

- •Overview

- •Block Diagram

- •Disclaimer

- •Pin Descriptions

- •Port C (PC5..PC0)

- •PC6/RESET

- •Port D (PD7..PD0)

- •RESET

- •AVCC

- •AREF

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Timer/Counter Oscillator

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Interrupts

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •Register Description for I/O Ports

- •External Interrupts

- •8-bit Timer/Counter0

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Operation

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •8-bit Timer/Counter2 with PWM and Asynchronous Operation

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Timer/Counter Prescaler

- •SS Pin Functionality

- •Slave Mode

- •Master Mode

- •SPI Control Register – SPCR

- •SPI Status Register – SPSR

- •SPI Data Register – SPDR

- •Data Modes

- •USART

- •Overview

- •AVR USART vs. AVR UART – Compatibility

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Two-wire Serial Interface

- •Features

- •TWI Terminology

- •Electrical Interconnection

- •Transferring Bits

- •START and STOP Conditions

- •Address Packet Format

- •Data Packet Format

- •Overview of the TWI Module

- •SCL and SDA Pins

- •Bit Rate Generator Unit

- •Bus Interface Unit

- •Address Match Unit

- •Control Unit

- •TWI Register Description

- •TWI Bit Rate Register – TWBR

- •TWI Control Register – TWCR

- •TWI Status Register – TWSR

- •TWI Data Register – TWDR

- •Using the TWI

- •Transmission Modes

- •Master Transmitter Mode

- •Master Receiver Mode

- •Slave Receiver Mode

- •Slave Transmitter Mode

- •Miscellaneous States

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Starting a Conversion

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •The ADC Data Register – ADCL and ADCH

- •ADLAR = 0

- •ADLAR = 1

- •Boot Loader Features

- •Application Section

- •BLS – Boot Loader Section

- •Boot Loader Lock Bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock Bits by SPM

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Two-wire Serial Interface Characteristics

- •ADC Characteristics

- •Active Supply Current

- •Idle Supply Current

- •Power-down Supply Current

- •Power-save Supply Current

- •Standby Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Ordering Information

- •Packaging Information

- •Erratas

- •Datasheet Change Log for ATmega8

- •Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03

- •Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03

- •Changes from Rev. 2486J-02/03 to Rev. 2486K-08/03

- •Changes from Rev. 2486I-12/02 to Rev. 2486J-02/03

- •Changes from Rev. 2486H-09/02 to Rev. 2486I-12/02

- •Changes from Rev. 2486G-09/02 to Rev. 2486H-09/02

- •Changes from Rev. 2486F-07/02 to Rev. 2486G-09/02

- •Changes from Rev. 2486E-06/02 to Rev. 2486F-07/02

- •Changes from Rev. 2486D-03/02 to Rev. 2486E-06/02

- •Changes from Rev. 2486C-03/02 to Rev. 2486D-03/02

- •Changes from Rev. 2486B-12/01 to Rev. 2486C-03/02

- •Table of Contents

ATmega8(L)

ATmega8(L)

• Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the XTAL frequency and the input clock to the ADC.

Table 76. ADC Prescaler Selections

ADPS2 |

ADPS1 |

ADPS0 |

Division Factor |

|

|

|

|

0 |

0 |

0 |

2 |

|

|

|

|

0 |

0 |

1 |

2 |

|

|

|

|

0 |

1 |

0 |

4 |

|

|

|

|

0 |

1 |

1 |

8 |

|

|

|

|

1 |

0 |

0 |

16 |

|

|

|

|

1 |

0 |

1 |

32 |

|

|

|

|

1 |

1 |

0 |

64 |

|

|

|

|

1 |

1 |

1 |

128 |

|

|

|

|

The ADC Data Register – ADCL and ADCH

ADLAR = 0

ADLAR = 1

Bit |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

– |

– |

– |

– |

– |

– |

ADC9 |

ADC8 |

ADCH |

|

|

|

|

|

|

|

|

|

ADCL |

|

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADC1 |

ADC0 |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Read/Write |

R |

R |

R |

R |

R |

R |

R |

R |

|

|

R |

R |

R |

R |

R |

R |

R |

R |

|

Initial Value |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Bit |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

ADC9 |

ADC8 |

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADCH |

|

|

|

|

|

|

|

|

|

ADCL |

|

ADC1 |

ADC0 |

– |

– |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Read/Write |

R |

R |

R |

R |

R |

R |

R |

R |

|

|

R |

R |

R |

R |

R |

R |

R |

R |

|

Initial Value |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

When an ADC conversion is complete, the result is found in these two registers.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted.

• ADC9:0: ADC Conversion result

These bits represent the result from the conversion, as detailed in “ADC Conversion

Result” on page 202.

205

2486M–AVR–12/03

Boot Loader Support

– Read-While-Write

Self-Programming

The Boot Loader Support provides a real Read-While-Write Self-Programming mechanism for downloading and uploading program code by the MCU itself. This feature allows flexible application software updates controlled by the MCU using a Flash-resi- dent Boot Loader program. The Boot Loader program can use any available data interface and associated protocol to read code and write (program) that code into the Flash memory, or read the code from the Program memory. The program code within the Boot Loader section has the capability to write into the entire Flash, including the Boot Loader Memory. The Boot Loader can thus even modify itself, and it can also erase itself from the code if the feature is not needed anymore. The size of the Boot Loader Memory is configurable with fuses and the Boot Loader has two separate sets of Boot Lock Bits which can be set independently. This gives the user a unique flexibility to select different levels of protection.

Boot Loader Features • Read-While-Write Self-Programming

•Flexible Boot Memory Size

•High Security (Separate Boot Lock Bits for a Flexible Protection)

•Separate Fuse to Select Reset Vector

•Optimized Page(1) Size

•Code Efficient Algorithm

•Efficient Read-Modify-Write Support

Note: 1. A page is a section in the Flash consisting of several bytes (see Table 93 on page 224) used during programming. The page organization does not affect normal operation.

Application and Boot

Loader Flash Sections

The Flash memory is organized in two main sections, the Application section and the Boot loader section (see Figure 102). The size of the different sections is configured by the BOOTSZ Fuses as shown in Table 82 on page 217 and Figure 102. These two sections can have different level of protection since they have different sets of Lock Bits.

Application Section |

The application section is the section of the Flash that is used for storing the application |

|

code. The protection level for the application section can be selected by the application |

|

boot Lock Bits (Boot Lock Bits 0), see Table 78 on page 209. The application section |

|

can never store any Boot Loader code since the SPM instruction is disabled when exe- |

|

cuted from the application section. |

BLS – Boot Loader Section |

While the application section is used for storing the application code, the The Boot |

|

Loader software must be located in the BLS since the SPM instruction can initiate a pro- |

|

gramming when executing from the BLS only. The SPM instruction can access the |

|

entire Flash, including the BLS itself. The protection level for the Boot Loader section |

|

can be selected by the Boot Loader Lock Bits (Boot Lock Bits 1), see Table 79 on page |

|

209. |

Read-While-Write and No

Read-While-Write Flash

Sections

Whether the CPU supports Read-While-Write or if the CPU is halted during a Boot Loader software update is dependent on which address that is being programmed. In addition to the two sections that are configurable by the BOOTSZ Fuses as described above, the Flash is also divided into two fixed sections, the Read-While-Write (RWW) section and the No Read-While-Write (NRWW) section. The limit between the RWWand NRWW sections is given in Table 83 on page 218 and Figure 102 on page 208. The main difference between the two sections is:

•When erasing or writing a page located inside the RWW section, the NRWW section can be read during the operation.

•When erasing or writing a page located inside the NRWW section, the CPU is halted during the entire operation.

206 ATmega8(L)

2486M–AVR–12/03

ATmega8(L)

Note that the user software can never read any code that is located inside the RWW section during a Boot Loader software operation. The syntax “Read-While-Write section” refers to which section that is being programmed (erased or written), not which section that actually is being read during a Boot Loader software update.

RWW – Read-While-Write If a Boot Loader software update is programming a page inside the RWW section, it is Section possible to read code from the Flash, but only code that is located in the NRWW section. During an on-going programming, the software must ensure that the RWW section never is being read. If the user software is trying to read code that is located inside the RWW section (i.e. by a call/rjmp/lpm or an interrupt) during programming, the software might end up in an unknown state. To avoid this, the interrupts should either be disabled or moved to the Boot Loader Section. The Boot Loader Section is always located in the NRWW section. The RWW Section Busy bit (RWWSB) in the Store Program memory Control Register (SPMCR) will be read as logical one as long as the RWW section is blocked for reading. After a programming is completed, the RWWSB must be cleared by software before reading code located in the RWW section. See “Store Program Memory

Control Register – SPMCR” on page 210. for details on how to clear RWWSB.

NRWW – No Read-While-Write The code located in the NRWW section can be read when the Boot Loader software is Section updating a page in the RWW section. When the Boot Loader code updates the NRWW

section, the CPU is halted during the entire page erase or page write operation.

Table 77. Read-While-Write Features

Which Section does the Z- |

Which Section Can be |

|

Read-While- |

pointer Address during the |

Read during |

Is the CPU |

Write |

Programming? |

Programming? |

Halted? |

Supported? |

|

|

|

|

RWW section |

NRWW section |

No |

Yes |

|

|

|

|

NRWW section |

None |

Yes |

No |

|

|

|

|

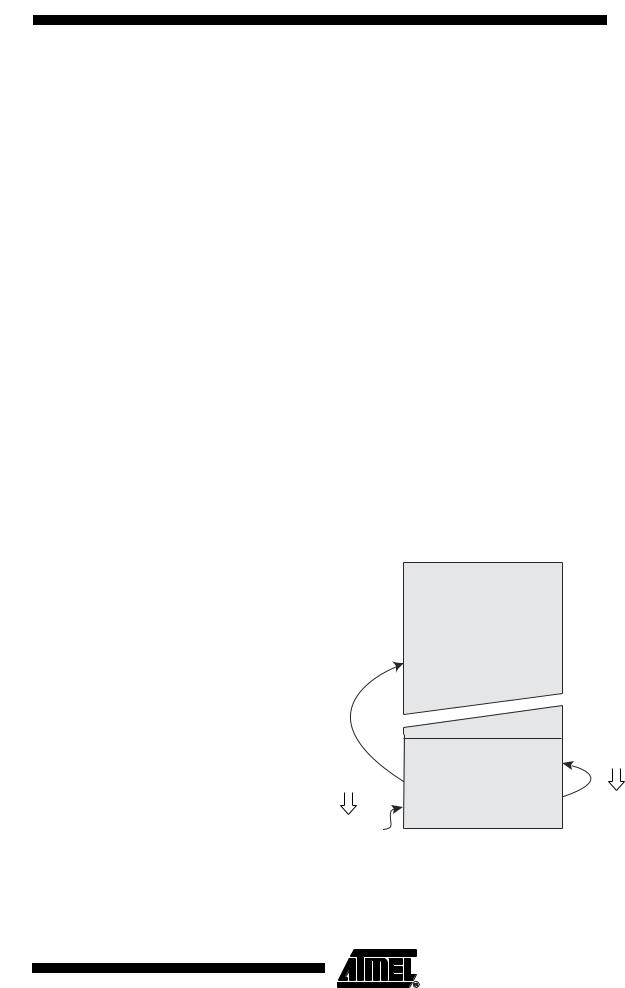

Figure 101. Read-While-Write vs. No Read-While-Write

Read-While-Write

(RWW) Section

|

Z-pointer |

|

Addresses NRWW |

Z-pointer |

section |

|

|

Addresses RWW |

No Read-While-Write |

section |

(NRWW) Section |

|

CPU is Halted |

Code Located in |

during the Operation |

|

|

NRWW Section |

|

Can be Read during |

|

the Operation |

|

207

2486M–AVR–12/03