- •Features

- •Pin Configurations

- •Overview

- •Block Diagram

- •Disclaimer

- •Pin Descriptions

- •Port C (PC5..PC0)

- •PC6/RESET

- •Port D (PD7..PD0)

- •RESET

- •AVCC

- •AREF

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Timer/Counter Oscillator

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Interrupts

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •Register Description for I/O Ports

- •External Interrupts

- •8-bit Timer/Counter0

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Operation

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •8-bit Timer/Counter2 with PWM and Asynchronous Operation

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Timer/Counter Prescaler

- •SS Pin Functionality

- •Slave Mode

- •Master Mode

- •SPI Control Register – SPCR

- •SPI Status Register – SPSR

- •SPI Data Register – SPDR

- •Data Modes

- •USART

- •Overview

- •AVR USART vs. AVR UART – Compatibility

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Two-wire Serial Interface

- •Features

- •TWI Terminology

- •Electrical Interconnection

- •Transferring Bits

- •START and STOP Conditions

- •Address Packet Format

- •Data Packet Format

- •Overview of the TWI Module

- •SCL and SDA Pins

- •Bit Rate Generator Unit

- •Bus Interface Unit

- •Address Match Unit

- •Control Unit

- •TWI Register Description

- •TWI Bit Rate Register – TWBR

- •TWI Control Register – TWCR

- •TWI Status Register – TWSR

- •TWI Data Register – TWDR

- •Using the TWI

- •Transmission Modes

- •Master Transmitter Mode

- •Master Receiver Mode

- •Slave Receiver Mode

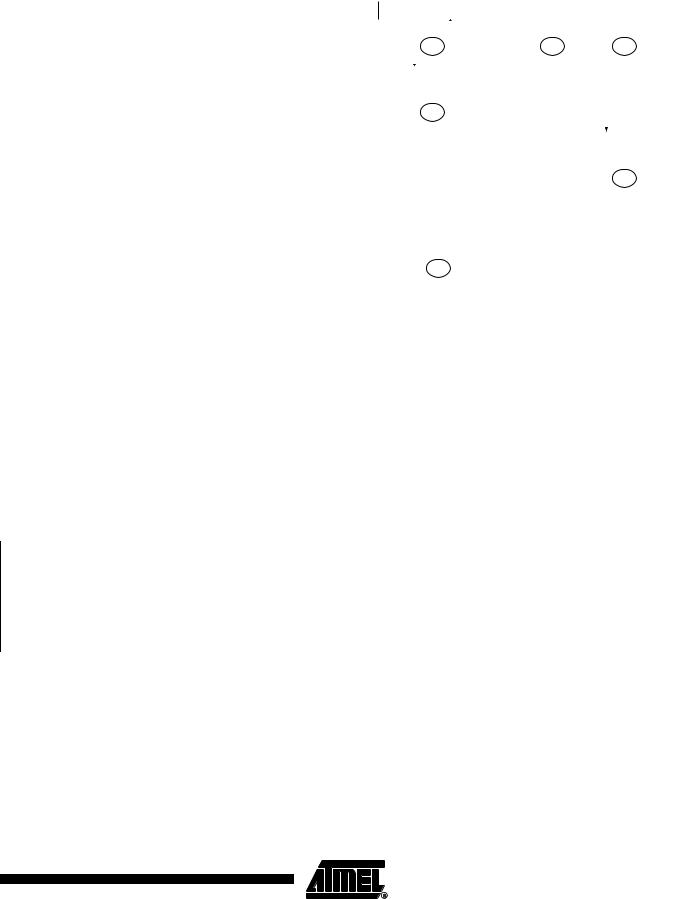

- •Slave Transmitter Mode

- •Miscellaneous States

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Starting a Conversion

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •The ADC Data Register – ADCL and ADCH

- •ADLAR = 0

- •ADLAR = 1

- •Boot Loader Features

- •Application Section

- •BLS – Boot Loader Section

- •Boot Loader Lock Bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock Bits by SPM

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Two-wire Serial Interface Characteristics

- •ADC Characteristics

- •Active Supply Current

- •Idle Supply Current

- •Power-down Supply Current

- •Power-save Supply Current

- •Standby Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Ordering Information

- •Packaging Information

- •Erratas

- •Datasheet Change Log for ATmega8

- •Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03

- •Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03

- •Changes from Rev. 2486J-02/03 to Rev. 2486K-08/03

- •Changes from Rev. 2486I-12/02 to Rev. 2486J-02/03

- •Changes from Rev. 2486H-09/02 to Rev. 2486I-12/02

- •Changes from Rev. 2486G-09/02 to Rev. 2486H-09/02

- •Changes from Rev. 2486F-07/02 to Rev. 2486G-09/02

- •Changes from Rev. 2486E-06/02 to Rev. 2486F-07/02

- •Changes from Rev. 2486D-03/02 to Rev. 2486E-06/02

- •Changes from Rev. 2486C-03/02 to Rev. 2486D-03/02

- •Changes from Rev. 2486B-12/01 to Rev. 2486C-03/02

- •Table of Contents

|

|

|

ATmega8(L) |

|

|

|

|

|

Slave Transmitter Mode |

|

|

|

In the Slave Transmitter mode, a number of data bytes are transmitted to a Master |

||

|

|||

|

|

Receiver (see Figure 84). All the status codes mentioned in this section assume that the |

|

prescaler bits are zero or are masked to zero.

Figure 84. Data Transfer in Slave Transmitter Mode

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Device 1 |

|

Device 2 |

|

Device 3 |

........ |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

Device n |

|

|

R1 |

|

R2 |

|

|

||||||||||||||

|

|

|

SLAVE |

|

|

MASTER |

|

|

|

|

|

|

|||||||||||||

|

|

TRANSMITTER |

|

|

RECEIVER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

SDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

To initiate the Slave Transmitter mode, TWAR and TWCR must be initialized as follows:

TWAR |

|

TWA6 |

TWA5 |

TWA4 |

TWA3 |

TWA2 |

TWA1 |

TWA0 |

TWGCE |

|

|

|

|

|

|

|

|

|

|

value |

|

|

Device’s Own Slave Address |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

The upper seven bits are the address to which the Two-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

TWCR |

TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

– |

TWIE |

value |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

X |

|

|

|

|

|

|

|

|

|

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device’s own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is “1” (read), the TWI will operate in ST mode, otherwise SR mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 69. The Slave Transmitter mode may also be entered if arbitration is lost while the TWI is in the Master mode (see state 0xB0).

If the TWEA bit is written to zero during a transfer, the TWI will transmit the last byte of the transfer. State 0xC0 or state 0xC8 will be entered, depending on whether the Master Receiver transmits a NACK or ACK after the final byte. The TWI is switched to the not addressed Slave mode, and will ignore the Master if it continues the transfer. Thus the Master Receiver receives all “1” as serial data. State 0xC8 is entered if the Master demands additional data bytes (by transmitting ACK), even though the Slave has transmitted the last byte (TWEA zero and expecting NACK from the Master).

While TWEA is zero, the TWI does not respond to its own slave address. However, the Two-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the Two-wire Serial Bus.

185

2486M–AVR–12/03

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the |

||||||||||

|

TWEA bit is set, the interface can still acknowledge its own slave address or the general |

||||||||||

|

call address by using the Two-wire Serial Bus clock as a clock source. The part will then |

||||||||||

|

wake up from sleep and the TWI will hold the SCL clock will low during the wake up and |

||||||||||

|

until the TWINT Flag is cleared (by writing it to one). Further data transmission will be |

||||||||||

|

carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is |

||||||||||

|

set up with a long start-up time, the SCL line may be held low for a long time, blocking |

||||||||||

|

other data transmissions. |

|

|

|

|

|

|

|

|

||

|

Note that the Two-wire Serial Interface Data Register – TWDR does not reflect the last |

||||||||||

|

byte present on the bus when waking up from these sleep modes. |

||||||||||

Table 69. Status Codes for Slave Transmitter Mode |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||

Status Code |

|

Application Software Response |

|

|

|||||||

(TWSR) |

Status of the Two-wire Serial Bus |

|

|

To TWCR |

|

|

|||||

Prescaler Bits |

and Two-wire Serial Interface |

|

|

|

|

||||||

To/from TWDR |

STA |

STO |

|

TWINT |

TWEA |

|

|||||

are 0 |

Hardware |

|

Next Action Taken by TWI Hardware |

||||||||

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|||

0xA8 |

Own SLA+R has been received; |

Load data byte or |

X |

0 |

|

|

|

1 |

|

0 |

Last data byte will be transmitted and NOT ACK should |

|

ACK has been returned |

|

|

|

|

|

|

|

|

|

be received |

|

|

Load data byte |

X |

0 |

|

|

|

1 |

|

1 |

Data byte will be transmitted and ACK should be re- |

|

|

|

|

|

|

|

|

|

|

|

ceived |

0xB0 |

Arbitration lost in SLA+R/W as |

Load data byte or |

X |

0 |

|

|

|

1 |

|

0 |

Last data byte will be transmitted and NOT ACK should |

|

Master; own SLA+R has been |

|

|

|

|

|

|

|

|

|

be received |

|

received; ACK has been returned |

Load data byte |

X |

0 |

|

|

|

1 |

|

1 |

Data byte will be transmitted and ACK should be re- |

|

|

|

|

|

|

|

|

|

|

|

ceived |

0xB8 |

Data byte in TWDR has been |

Load data byte or |

X |

0 |

|

|

|

1 |

|

0 |

Last data byte will be transmitted and NOT ACK should |

|

transmitted; ACK has been |

|

|

|

|

|

|

|

|

|

be received |

|

received |

Load data byte |

X |

0 |

|

|

|

1 |

|

1 |

Data byte will be transmitted and ACK should be re- |

|

|

|

|

|

|

|

|

|

|

|

ceived |

0xC0 |

Data byte in TWDR has been |

No TWDR action or |

0 |

0 |

|

|

|

1 |

|

0 |

Switched to the not addressed Slave mode; |

|

transmitted; NOT ACK has been |

|

|

|

|

|

|

|

|

|

no recognition of own SLA or GCA |

|

received |

No TWDR action or |

0 |

0 |

|

|

|

1 |

|

1 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

own SLA will be recognized; |

|

|

|

|

|

|

|

|

|

|

|

GCA will be recognized if TWGCE = “1” |

|

|

No TWDR action or |

1 |

0 |

|

|

|

1 |

|

0 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

no recognition of own SLA or GCA; |

|

|

|

|

|

|

|

|

|

|

|

a START condition will be transmitted when the bus |

|

|

|

|

|

|

|

|

|

|

|

becomes free |

|

|

No TWDR action |

1 |

0 |

|

|

|

1 |

|

1 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

own SLA will be recognized; |

|

|

|

|

|

|

|

|

|

|

|

GCA will be recognized if TWGCE = “1”; |

|

|

|

|

|

|

|

|

|

|

|

a START condition will be transmitted when the bus |

|

|

|

|

|

|

|

|

|

|

|

becomes free |

0xC8 |

Last data byte in TWDR has been |

No TWDR action or |

0 |

0 |

|

|

|

1 |

|

0 |

Switched to the not addressed Slave mode; |

|

transmitted (TWEA = “0”); ACK |

|

|

|

|

|

|

|

|

|

no recognition of own SLA or GCA |

|

has been received |

No TWDR action or |

0 |

0 |

|

|

|

1 |

|

1 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

own SLA will be recognized; |

|

|

|

|

|

|

|

|

|

|

|

GCA will be recognized if TWGCE = “1” |

|

|

No TWDR action or |

1 |

0 |

|

|

|

1 |

|

0 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

no recognition of own SLA or GCA; |

|

|

|

|

|

|

|

|

|

|

|

a START condition will be transmitted when the bus |

|

|

|

|

|

|

|

|

|

|

|

becomes free |

|

|

No TWDR action |

1 |

0 |

|

|

|

1 |

|

1 |

Switched to the not addressed Slave mode; |

|

|

|

|

|

|

|

|

|

|

|

own SLA will be recognized; |

|

|

|

|

|

|

|

|

|

|

|

GCA will be recognized if TWGCE = “1”; |

|

|

|

|

|

|

|

|

|

|

|

a START condition will be transmitted when the bus |

|

|

|

|

|

|

|

|

|

|

|

becomes free |

186 ATmega8(L)

2486M–AVR–12/03

ATmega8(L)

ATmega8(L)

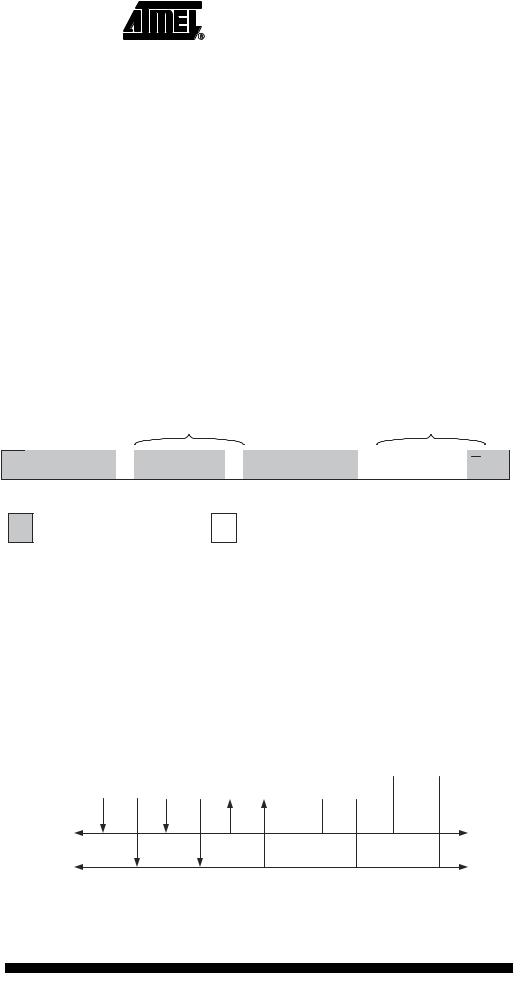

Figure 85. Formats and States in the Slave Transmitter Mode

|

|

Reception of the own |

S |

SLA |

R |

|

A |

|

DATA |

A |

|

DATA |

|

|

|

|

|

|

P or S |

|

|

|

|||

|

|

slave address and one or |

|

|

|

|

|

A |

|

|

|

|

|

||||||||||||

|

|

more data bytes |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

$A8 |

|

|

$B8 |

|

|

$C0 |

|

|

|

|

|||||||

|

|

Arbitration lost as master |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

and addressed as slave |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

$B0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Last data byte transmitted. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

All 1's |

P or S |

|

|||||

|

|

Switched to not addressed |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

slave (TWEA = '0') |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

$C8 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Any number of data bytes |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

From master to slave |

|

DATA |

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

and their associated acknowledge bits |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

From slave to master |

|

|

|

|

n |

|

This number (contained in TWSR) corresponds |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

to a defined state of the Two-Wire Serial Bus. The |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

prescaler bits are zero or masked to zero |

|

|

|

|

||||||||||

Miscellaneous States |

There are two status codes that do not correspond to a defined TWI state, see Table 70. |

||||||||||||||||||||||||

Status 0xF8 indicates that no relevant information is available because the TWINT Flag is not set. This occurs between other states, and when the TWI is not involved in a serial transfer.

Status 0x00 indicates that a bus error has occurred during a Two-wire Serial Bus transfer. A bus error occurs when a START or STOP condition occurs at an illegal position in the format frame. Examples of such illegal positions are during the serial transfer of an address byte, a data byte, or an acknowledge bit. When a bus error occurs, TWINT is set. To recover from a bus error, the TWSTO Flag must set and TWINT must be cleared by writing a logic one to it. This causes the TWI to enter the not addressed Slave mode and to clear the TWSTO Flag (no other bits in TWCR are affected). The SDA and SCL lines are released, and no STOP condition is transmitted.

Table 70. |

Miscellaneous States |

|

|

|

|

|

|

||

Status Code |

|

|

|

Application Software Response |

|

|

|||

(TWSR) |

|

Status of the Two-wire Serial |

|

|

To TWCR |

|

|

||

Prescaler Bits |

|

Bus and Two-wire |

Serial Inter- |

|

|

|

|

||

|

To/from TWDR |

STA |

STO |

TWINT |

TWEA |

|

|||

are 0 |

|

face Hardware |

|

Next Action Taken by TWI Hardware |

|||||

|

|

|

|||||||

|

|

|

|

|

|

|

|||

0xF8 |

|

No relevant state |

information |

No TWDR action |

|

No TWCR action |

|

Wait or proceed current transfer |

|

|

|

available; TWINT = “0” |

|

|

|

|

|

|

|

0x00 |

|

Bus error due to an illegal |

No TWDR action |

0 |

1 |

1 |

X |

Only the internal hardware is affected, no STOP condi- |

|

|

|

START or STOP condition |

|

|

|

|

|

tion is sent on the bus. In all cases, the bus is released |

|

|

|

|

|

|

|

|

|

|

and TWSTO is cleared. |

187

2486M–AVR–12/03

Combining Several TWI |

|

|

|

|

|

|

|

|

|

|

|

|

|

In some cases, several TWI modes must be combined in order to complete the desired |

||||||

Modes |

action. Consider for example reading data from a serial EEPROM. Typically, such a |

|||||

|

transfer involves the following steps: |

|||||

|

1. |

The transfer must be initiated. |

||||

|

2. |

The EEPROM must be instructed what location should be read. |

||||

|

3. |

The reading must be performed. |

||||

|

4. |

The transfer must be finished. |

||||

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multimaster system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

Figure 86. Combining Several TWI Modes to Access a Serial EEPROM

|

|

|

Master Transmitter |

|

|

|

Master Receiver |

|

S |

SLA+W |

A |

ADDRESS |

A Rs |

SLA+R |

A |

DATA |

A P |

S = START |

|

|

Rs = REPEATED START |

|

|

P = STOP |

||

|

Transmitted from master to slave |

Transmitted from slave to master |

|

|||||

Multi-master Systems

and Arbitration

If multiple masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

Figure 87. An Arbitration Example

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Device 1 |

|

Device 2 |

|

Device 3 |

........ |

|

|

|

|

|

|

|

|

|

|

|

Device n |

|

|

R1 |

|

R2 |

|

||||||

MASTER |

|

MASTER |

|

SLAVE |

|

|

|

|

||||||

TRANSMITTER |

|

TRANSMITTER |

|

RECEIVER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA

SCL

Several different scenarios may arise during arbitration, as described below:

188 ATmega8(L)

2486M–AVR–12/03

ATmega8(L)

ATmega8(L)

•Two or more masters are performing identical communication with the same Slave. In this case, neither the Slave nor any of the masters will know about the bus contention.

•Two or more masters are accessing the same Slave with different data or direction bit. In this case, arbitration will occur, either in the READ/WRITE bit or in the data bits. The masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Losing masters will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

•Two or more masters are accessing different slaves. In this case, arbitration will occur in the SLA bits. Masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Masters losing arbitration in SLA will switch to Slave mode to check if they are being addressed by the winning Master. If addressed, they will switch to SR or ST mode, depending on the value of the READ/WRITE bit. If they are not being addressed, they will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

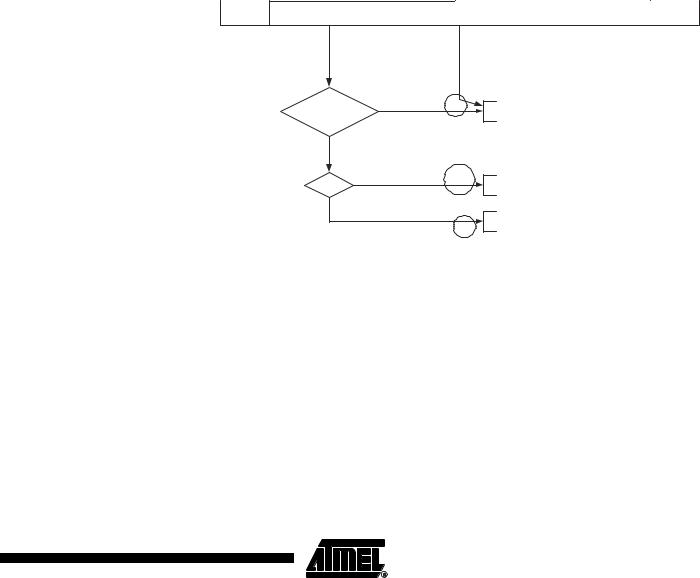

This is summarized in Figure 88. Possible status values are given in circles.

Figure 88. Possible Status Codes Caused by Arbitration

START |

SLA |

|

Data |

STOP |

|

|

Arbitration lost in SLA |

Arbitration lost in Data |

|

||

|

Own |

No |

38 |

TWI bus will be released and not addressed slave mode will be entered |

|

|

|

||||

|

Address / General Call |

|

A START condition will be transmitted when the bus becomes free |

||

|

received |

|

|

||

|

|

|

|

|

|

|

Yes |

|

|

|

|

|

Direction |

Write |

68/78 |

Data byte will be received and NOT ACK will be returned |

|

|

|

|

Data byte will be received and ACK will be returned |

|

|

|

|

|

|

|

|

|

|

Read |

|

Last data byte will be transmitted and NOT ACK should be received |

|

|

|

|

B0 |

Data byte will be transmitted and ACK should be received |

|

189

2486M–AVR–12/03