- •Фгбоу впо «Уфимский государственный авиационный технический университет»

- •Расчетно-пояснительная записка к выпускной квалификационной работе

- •Фгбоу впо «уфимский государственный авиационный технический университет»

- •Задание по подготовке выпускной квалификационной работы _____Низамова Захара Дмитриевича________________

- •Фгбоу впо «уфимский государственный авиационный технический университет»

- •Календарный план работы над выпускной квалификационной работой

- •Памятка дипломнику

- •Введение.

- •Обзор существующих методов и устройств для определения параметров дыхания.

- •1.1 Методы и устройства для определения параметров дыхания

- •Дыхательный аппарат человека составляют:

- •Cпирометрия

- •Спирография

- •Вентиляция

- •Пикфлоуметрия

- •Сопротивление воздухоносных путей.

- •Капнограф

- •Пневмотахограф

- •1.2 Патентные исследования

- •1.3 Выбор и обоснование структурной схемы

- •2Проектирование и расчет электрической принципиальной cхемы

- •2.1 Турбинный преобразователь расхода

- •2.2 Формирователь импульсов

- •2.3 Схема «и»

- •2.4 Регистратор

- •2.5 Блок выделения времени выдоха

- •2.6 Блок управления

- •2.7 Источник питания с батарейкой

- •3Метрологическая часть

- •3.1 Погрешность пороговой схемы

- •3.2 Погрешность операционного усилителя

- •4. Анализ надежности разрабатываемого устройства

- •4.1 Ориентировочный расчет надежности

- •5. Технологическая часть

- •5.1 Технологический процесс производства печатных плат

- •5.1.1 Химический способ изготовления печатных плат

- •5.1.2 Электрохимический способ получения печатных плат

- •5.2 Технологический процесс сборки печатных плат

- •6.Организационно-экономическое обоснование целесообразности инженерной разработки и внедрения результатов дипломного проектирования

- •6.1.Обоснование актуальности разработки

- •6.2.Функционально-стоимостной анализ. Выбор и оценка показателей качества

- •Построение функциональной схемы и определение значимостей функций.

- •Выбор варианта реализации каждой функции.

- •Построение функционально-стоимостных диаграмм(фсд).

- •Определение экономической целесообразности

- •7 Безопасность и экологичность проекта Обеспечение безопасных условий труда на стадии изготовления устройства измерения параметров дыхания

- •7.1 Идентификация и анализ опасных и вредных факторов на рабочем месте.

- •7.1.1 Повышенное значение напряжения в электрической цепи, замыкание которой может произойти через тело человека

- •7.1.2 Повышенный уровень запыленности и загазованности рабочей зоны

- •7.1.3Повышенный уровень шума

- •7.1.4 Недостаточная освещенность рабочей зоны

- •7.2 Мероприятия по обеспечению электро безопасности при пайке

- •7.3 Расчет защитного заземления

- •7.4 Расчет местной вентиляции

- •Заключение

- •Список литературы

- •Приложение а

- •Приложение б

- •Приложение в

- •Приложение г

- •Приложение д

- •Приложение е

- •Приложение ж

- •Приложение з

- •Приложение и Определение издержек при эксплуатации

2.6 Блок управления

Блок управления служит для стабилизации напряжения питания устройства, выдачи сигнала о необходимости замены батареи источника питания в случае ее разряда, а на схему "И" 5 сигнал блокировки, генерирования опорного сигнала, одиночного секундного импульса и формирования импульса автоматического сброса в нуль делителя импульсов и узлов памяти регистратора при подаче питания на устройство и с началом выдоха, обеспечивая такую организацию по времени работы узлов и блоков устройства, которая позволяет исключать подсчет и регистрацию ложных импульсов, возникающих на выходе датчика преобразователя расхода из-за инерционности вращения его турбины. Блок управления содержит стабилизатор питания, пороговую схему (рисунок 2.6.1) и времязадающий узел (рисунок 2.6.2). Стабилизатор питания и пороговая схема обеспечивают стабилизацию напряжения питания устройства и отработку пороговой схемой сигнала запрета на прохождение информационных импульсов через схему "И" при разряде батареи источника питания. При разряженной батарее источника питания этот сигнал имеет низкий уровень, запрещающий прохождение через схему "И" информационных импульсов и приводящий к высвечиванию светодиода VD3, сообщающего о разряде батареи, до замены которой благодаря запрету на прохождение информационных импульсов через схему "И" измерения проводить невозможно. Этим исключается возможность регистрации результатов измерения, искаженных за счет понижения уровня амплитуды информационного сигнала, искажения его формы в светочувствительном элементе датчика и ухода частоты опорного сигнала. При нормальном уровне ЭДС батареи источника питания сигнал на выходе пороговой схемы имеет высокий уровень, разрешая по схемы "И" прохождение информационных импульсов на регистратор. При этом светодиод не высвечивается, что говорит о возможности проведения измерений.

Рисунок 2.6.1 Схема стабилизатора питания и пороговой схемы.

В качестве стабилизатора питания используем DA2 выбираем микросхему L7809CV.

Ее основные параметры:

Uвх=35÷12В;

Uвых=9В;

I н мах=1,5А;

Iпот=10мА.

Пороговая схема построена на компараторе DD21-4A71OM.

Ее основные параметры:

Напряжения смещения нуля 7,5мВ

Средний входной ток 75мкА

Коэффициент усиления напряжения 750

Время задержки выключения 130нс

В качестве инверторов выбираем микросхемы К561ЛЕ2.

R22 R23выполняют роль делителя напряжения.

(2.6.1)

(2.6.1)

(2.6.2)

(2.6.2)

Уровень срабатывания V=8В

(2.6.3)

(2.6.3)

(2.6.4)

(2.6.4)

Светодиод выбираем АЛ102АМ.

Основные характеристики:

I=5мА;

Диаметр 5мм;

Цвет свечения – красный.

![]() (2.6.5)

(2.6.5)

Времязадающий узел предназначен для генерирования опорного сигнала, одиночного секундного импульса и формирования импульса автоматического сброса в нуль счетчиков регистратора.

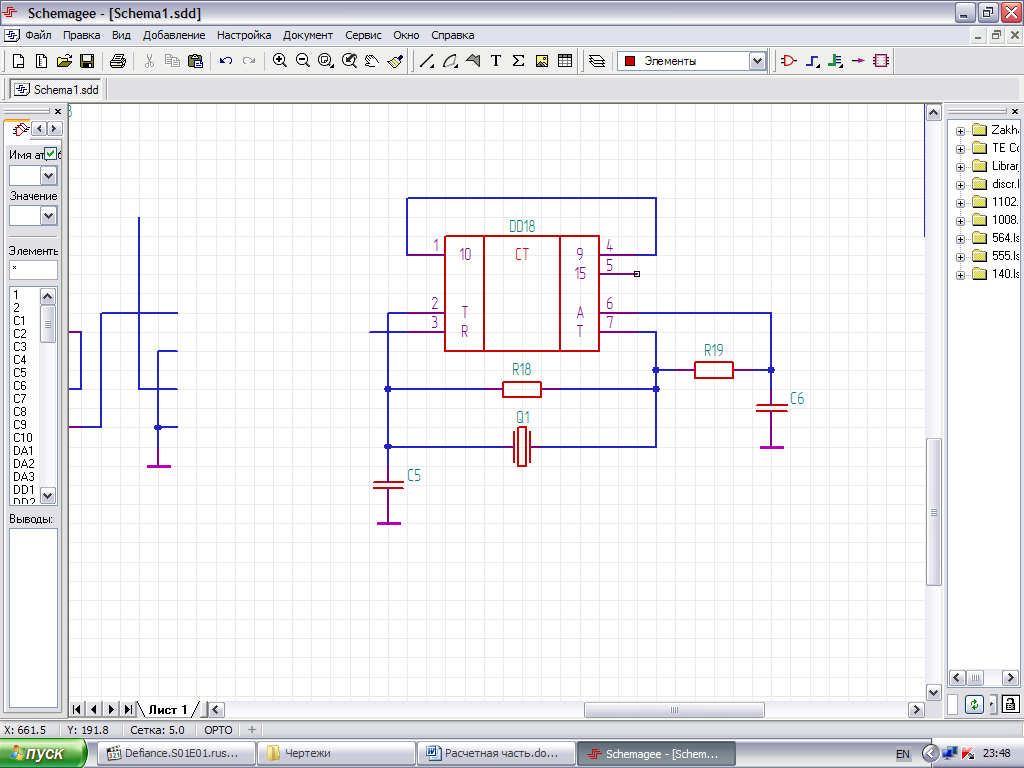

Рисунок 2.6.2 Времязадающий узел.

В о

времязадающий узел входят триггерDD17,

типа К561ТМ2, описанная выше, счетчик DD18

типа К555ИЕ5,

содержащий кварцевый генератор с внешним

резонатором на 32768 Гц и подключенным к

нему девятиразрядным делителем частоты

и шестиразрядный делитель частоты, и

логические элементы "И-НЕ" DD6.1÷DD6.2

и DD6.3

построенных на микросхемах типа К555ЛА3,

описанная ранее, связанные, между собой

и с рядом резисторов R и конденсаторов

С. Времязадающий узел, формирует опорный

сигнал частоты 32 Гц.

о

времязадающий узел входят триггерDD17,

типа К561ТМ2, описанная выше, счетчик DD18

типа К555ИЕ5,

содержащий кварцевый генератор с внешним

резонатором на 32768 Гц и подключенным к

нему девятиразрядным делителем частоты

и шестиразрядный делитель частоты, и

логические элементы "И-НЕ" DD6.1÷DD6.2

и DD6.3

построенных на микросхемах типа К555ЛА3,

описанная ранее, связанные, между собой

и с рядом резисторов R и конденсаторов

С. Времязадающий узел, формирует опорный

сигнал частоты 32 Гц.

Формирование секундного импульса разрешения счета для узла памяти осуществляется времязадающим узлом по поступлению на его вход логического элемента DD6.1 информационных импульсов со схемы "И", и стробирующего сигнала высокого уровня с инверсного выхода триггера DD15.1 узла фильтрации, причем длительность фронта стробирующего сигнала на входе времязадающего узла должна быть такой, чтобы обеспечить прохождение через его логические элементы DD6.1÷DD6.2 на вход S триггера DD17 только первого информационного импульса.

Сигнал низкого уровня с инверсного выхода триггера DD17, поступая на вход R счетчика DD18, дает разрешение на формирование на 15-м выходе счетчика одиночного секундного импульса. При этом счетчик работает в режиме двойного деления частоты, поддерживая в течение 1 секунды низкий уровень сигнала на своем 15-м выходе. По истечении одной секунды на 15-м выходе счетчика DD18 появляется сигнал высокого уровня, перебрасывающий триггер DD17 по его входу С в нулевое состояние, в результате чего на его прямом выходе заканчивается формирование одиночного секундного импульса и до следующего цикла измерения устанавливается сигнал низкого уровня, запрещающий прохождение информации через узел памяти DD9 регистратора .

Таким образом, начало секундного импульса разрешения счета, управляющего узлом памяти DD9, всегда будет совпадать с поступлением в блок регистрации первого информационного импульса, а длительность его действия, формируемая блоком управления, равна одной секунде, после чего до завершения цикла измерения (один полный выдох) вход узла памяти удерживает его в закрытом состоянии. Этим обеспечивается возможность измерения устройством объема выдоха за первую секунду выдоха.

В ремязадающем

узле формируется секундный импульс

следовательно τ=1с.

ремязадающем

узле формируется секундный импульс

следовательно τ=1с.

![]() (2.6.6)

(2.6.6)

Примем С7=10мкФ

(2.6.7)

(2.6.7)

Аналогично рассчитываются R21 и C8.

Нами используется типовое включение счетчика DD19 построенного на микросхеме К555ИЕ5. Рисунок 2.6.3.

Рисунок 2.6.3 Схема включения микросхемы К555ИЕ5.

К выводам 2 и 7 подключен кварцевый

резонатор. Частота кварцевого резонатора

32768Гц. Чтобы счетчик давал секундную

последовательность, выводы 1 и 2 следует

перемкнуть, поскольку вывод2 – это вход

частотыf/28.

выводам 2 и 7 подключен кварцевый

резонатор. Частота кварцевого резонатора

32768Гц. Чтобы счетчик давал секундную

последовательность, выводы 1 и 2 следует

перемкнуть, поскольку вывод2 – это вход

частотыf/28.

В блоке управления использовались следующие элементы:

DA2 – L7809CV;

DD19 – 4A71OM;

DD2.5,DD2.6,DD3.1- K561ЛЕ2;

VD3- АЛ102АМ;

R22- C2-29В-0,125-2 кОм±0,05%

R23- C2-29В-0,25-18 кОм±0,5%

R24- C2-29В-0,25-1,8 кОм±0,05%

C9,C10- К53-16-20В-100 мкФ±20%

DD5.1,DD6.2,DD6.3- К555ЛА3;

DD17- К561ТМ2;

DD18- К555ИЕ5;

R18- С2-29В-0,125-22 МОм±0,5%

R19- С2-29В-0,25-2 МОм±0,5%

R20,R21- C2-29В-0,125-100 кОм±0,5%

C5- К71-7-250В-62 нФ±5%

C6- К10-17а-25В-М75-22 нФ±5%

C7,C8- К71-6-250В-10 мкФ±10%

ZQ1- DT-26