4 Описание схемы на hdl

По

варианту было определенно, что для

работы будет использоваться язык

описания SV.

Ниже, на рисунках 4.1 – 4.3

представлен код описывающий схему

вычислительного блока.

Р исунок

4.1

— Описание на SV

исунок

4.1

— Описание на SV

Рисунок

4.2

— Описание на SV

Рисунок

4.3

— Описание на SV

На

строках 1-6

описаны входы и выходы необходимые для

описания.

На

строках 9-15

описаны используемые сигналы.

На

строках 22-32 описана работа

счетчика сигналов и кодов.

На

строках 34-55 описана

реализация

задачи, логической и арифметической

функций, а так же

флормирование res.

На

строках 57-117 описан конечный

автомат для получения конечного

результата Q и cout.

На

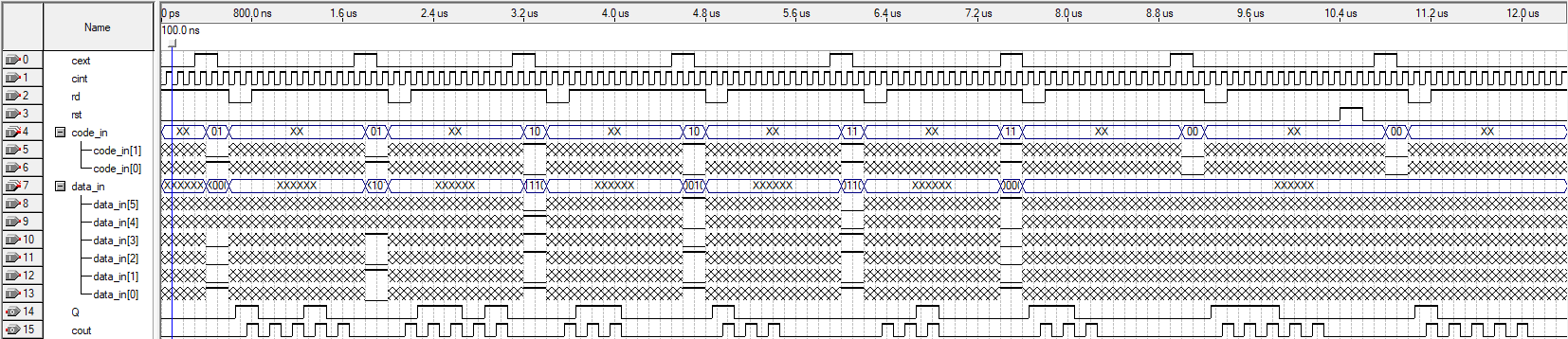

рисунках 4.3 – 4.4 представлены результаты

моделирования кода в

режимах

Timing и Functional соответственно.

Р исунок

4.3 — Моделирования в

режиме Timing

исунок

4.3 — Моделирования в

режиме Timing

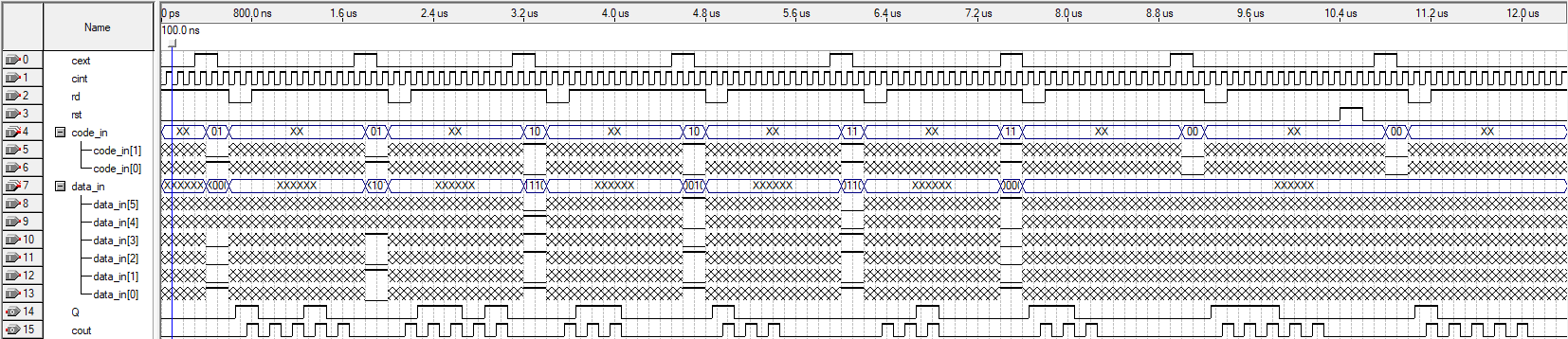

Р исунок

4.4 – Моделирования

в режиме Functional

исунок

4.4 – Моделирования

в режиме Functional

На

рисунке 4.5

представлена RTL на базе написанного

кода.

На

рисунке 4.6,

4.7 представлен

граф переходов состояний и таблица

условий

перехода состояний.

Р исунок

4.5 — RTL схема

исунок

4.5 — RTL схема

Рисунок

4.6 — Граф перехдов

Рисунок

4.7— Условия перехдов

Заключение

В

результате лабораторной работы был

разработан вычислительный блок,

реализующий задачу

кодирования двоичного числа в 4b5b-кода,

выполнение

логической

операции

и арифметической

A-B. . Сам же

вход схемы осуществляется убывающим

фронтом с параллельным

кодос, при

этом обладающий асинхронным сбросом.

Выход осуществляется нарастающим

фронтом с

последовательным кодом сладшими

разрядами вперед

с активным уровнем сигнала 0.

Помимо

этого было произведено моделирование

и описание схемы на языке описания

аппаратуры SystemVerilog. Результаты

моделирований совпали с таблицей

истинности.

23

исунок

4.1

— Описание на SV

исунок

4.1

— Описание на SV

исунок

4.3 — Моделирования в

режиме Timing

исунок

4.3 — Моделирования в

режиме Timing исунок

4.4 – Моделирования

в режиме Functional

исунок

4.4 – Моделирования

в режиме Functional исунок

4.5 — RTL схема

исунок

4.5 — RTL схема