Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение Высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР) Кафедра безопасности информационных систем (БИС)

ПРИМЕНЕНИЕ ТРИГГЕРОВ, РЕГИСТРОВ И СЧЁТЧИКОВ Отчёт по лабораторной работе №3

По дисциплине «Электроника и схемотехника» Вариант №16

Студент гр. 733-1 Сметанников Д.Е

05 . 06 .2024

Руководитель Доцент кафедры

КИБЭВС, к.т.н., доцент А.Н. Мальчуков

. .2025

Томск 2025

Введение

Цель работы – научиться совместно применять триггеры, регистры и счётчики.

Постановка задачи:

•Из ЛР1 взять функции функций X= A B(C D), X=( A B)C D,

X=( A B)C D, X= A(B C)D.

•Собрать схемы на холсте .bdf согласно полученным формулам.

•Составить таблицу истинности для данных функций.

•Для выполнения 4-х параллельныъ операций организовать прием и выдачу согласно данным параметрам: прием - нарастающий, последовательным кодом младшими разрядами вперед и асинхронный сброс. Выдача - убывающая, параллельным кодом и активный уровень сигнала «read» равный 0.

•Промоделировать схемы в режимах «Timing» и «Functional» так, чтобы в результате каждая функция принимала значения 0 и 1.

•Сверить с результатами из таблицы истинности и результатом моделирования.

•Повторить эти пункты, только для описания устройств вместо схем на .bdf использовать HDL VHDL и реализовать автомат для выдачи данных и их тактирования.

•Создать схему из RTL Viewer для кода HDL.

•Написать выводы о проделанной работе.

2

|

|

|

|

|

Ход работы |

|

|

|

|

||

|

В ходе работы был |

реализованы |

функции |

X= A B( |

|

, |

|||||

C D) |

|||||||||||

X=( |

|

)C D,X=( |

|

)C D, |

X= A( |

|

)D |

на холсте |

.bdf. Составил |

||

A B |

A B |

B C |

|||||||||

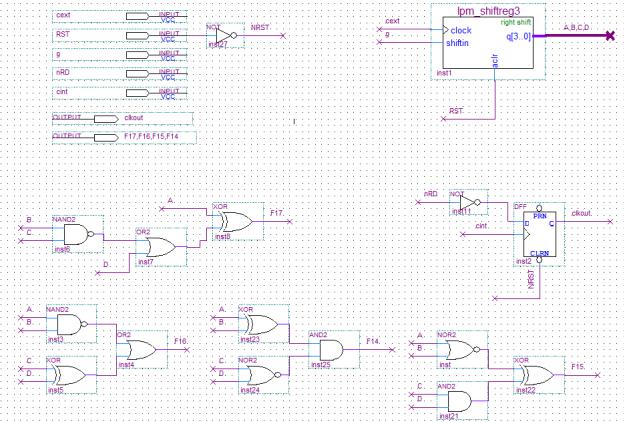

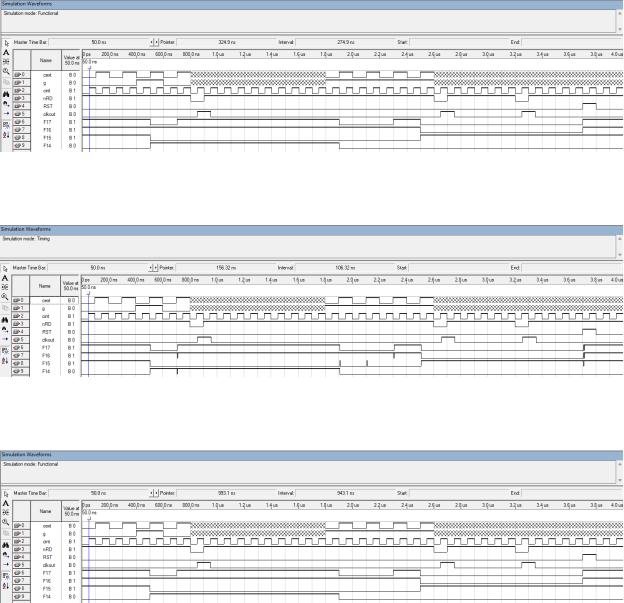

таблицу истинности для данных функций. Для выполнения 4-х параллельных операций собрал схемы lpm_shiftreg и DFF. Промоделировал их в режимах «Timing» и «Functional». Результаты, полученные в результате моделирования, совпали с таблицей истинности. Описал функции на HDL VHDL и реализовал в нем конечный автомат для выдачи данных и их тактирования. Промоделировал его в режимах «Timing» и «Functional». Результаты, полученные в результате моделирования, совпали с таблицей истинности. По коду HDL собрал схему с помощью инструмента RTL Viewer.

Для моделирования были выбраны 5 и 16 строки таблицы истинности, которые задаются в моделировании в таком же порядке.

Строка 0100. Интервал для приема 4х бит данных cext находится на временных отрезках в 100, 300, 500, 700 нс. Интервал времени при котором nRD=0 равен 800-900. Момент убывающего фронта clkout соответствует интервалу 850-950 нс. На выходе функция имеет значение 1101.

Строка 1111. Интервал для приема 4х бит данных cext находится на временных отрезках в 1.9, 2.1, 2.3 и 2.5 мкс. Интервал времени при котором nRD=0 равен 2.6 — 2.8 мкс. Момент убывающего фронта clkout соответствует интервалу 2.65 — 2.75 мкс. На выходе функция имеет значение 0010.

Строки 6 — 7 описывают входы и выходы. Строки 11 — 13 описывают инициализацию сигналов. Строки 17 — 25 опсывают логические выражения для функций F14, F15, F16, F17. Строки 28 — 32 описывают тактовый сигнал для ввода входных значений нарастающим фронтом. Строки 35 — 39 описывают асинхронных сброс.

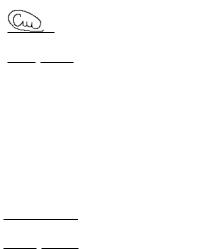

Схема представлена на рисунке 1. Код представлен на рисунке 2.

Результаты моделирования представлены на рисунках 3-6.

3

Схема из RTL Viewer для кода HDL представлена на рисунке 7.

Рисунок 1 — Схема на холсте .bdf

4

Рисунок 2 — Код на HDL VHDL

Рисунок 3 — Моделирование схемы в режиме «Timing»

5

Рисунок 4 — Моделирование схемы в режиме «Functional»

Рисунок 5 — Моделирование кода в режиме «Timing»

Рисунок 6 — Моделирование кода в режиме «Functional»

6

Рисунок 7 — Схема из RTL Viewer для кода HDL

Таблица 1 — Таблца истинности

|

Входы |

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

x |

y |

|

z |

w |

F17 |

F16 |

F15 |

F14 |

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

7

Окончание таблицы 1

|

Входы |

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

x |

y |

|

z |

w |

F17 |

F16 |

F15 |

F14 |

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

8

Заключение

В результате лабораторной работы были собраны логические схемы функций X= A B(C D), X=( A B)C D, X=( A B)C D, X= A(B C)D. Была составлена таблица истинности для функций.

Также были смоделированы работы данных схем в режимах «Timing» и «Functional». Результаты моделирования были сравнены с таблицей истинности. Результаты совпали. Также были описаны схемы на языке HDL VHDL и так же промоделированы режимах «Timing» и «Functional». Результаты моделирования были сравнены с таблицей истинности. Результаты совпали.

Было приведено описание HDL кода и моделирования.

По описанию была собрана схема с помощью инструмента RTL Viewer.

9