Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение

Высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра безопасности информационных систем (БИС)

КОМБИНАЦИОННЫЕ УСТРОЙСТВА

Отчёт по лабораторной работе №2

По дисциплине «Электроника и схемотехника»

Вариант №16

-

С

тудент

гр. 733-1

тудент

гр. 733-1Сметанников Д.Е

24 . 05 .2024

-

Руководитель

Доцент кафедры КИБЭВС, к.т.н., доцент

А.Н. Мальчуков

. .2025

Введение

Цель работы – научиться применять мультиплексоры, шифраторы и

дешифраторы.

Постановка задачи:

Из ЛР1 взять функции функций

,

,

,

,

,

,

.

.Собрать схемы на холсте .bdf согласно полученным формулам. Первая функция реализована на СКНФ, вторая функция в виде функции, третья функция на мультиплексоре и последняя на дешифраторе. Выход должен быть реализован через tri_buf.

Составить таблицу истинности для данных функций.

Промоделировать схемы в режимах «Timing» и «Functional» так, чтобы в результате каждая функция принимала значения 0 и 1.

Сделать предположение из-за чего возникает разница в результатах моделирования.

Сверить с результатами из таблицы истинности и результатом моделирования.

Повторить эти пункты, только для описания устройств вместо схем на .bdf использовать HDL VHDL (v1).

Из ЛР1 взять функции

,

,

,

,

и

.

и

.Собрать схемы на холсте .bdf согласно полученным формулам. Первая функция реализована на СКНФ, вторая функция в виде функции, третья функция на мультиплексоре и последняя на дешифраторе. Выход должен быть реализован через MUX.

Составить таблицу истинности для данных функций.

Промоделировать схемы в режимах «Timing» и «Functional» так, чтобы в результате каждая функция принимала значения 0 и 1.

Сделать предположение из-за чего возникает разница в результатах моделирования.

Сверить с результатами из таблицы истинности и результатом моделирования.

Повторить эти пункты, только для описания устройств вместо схем на .bdf использовать HDL SV.

Составить таблицу истинности для данных функций и для приоритетного шифратора 4-2. Составить формулы для каждого выхода. Согласно закону де Моргана преобразовать формулы в базис И-НЕ.

Собрать схему приоритетного шифратора на холсте .bdf в базисе И-НЕ.

Промоделировать схемы в режимах «Timing» и «Functional» так, чтобы в результате каждая функция принимала значения 0 и 1. Сделать предположение из-за чего возникает разница в результатах моделирования.

Сверить с результатами из таблицы истинности и результатом моделирования.

Повторить эти пункты, только для описания устройств вместо схем на .bdf использовать SV.

Написать выводы о проделанной работе.

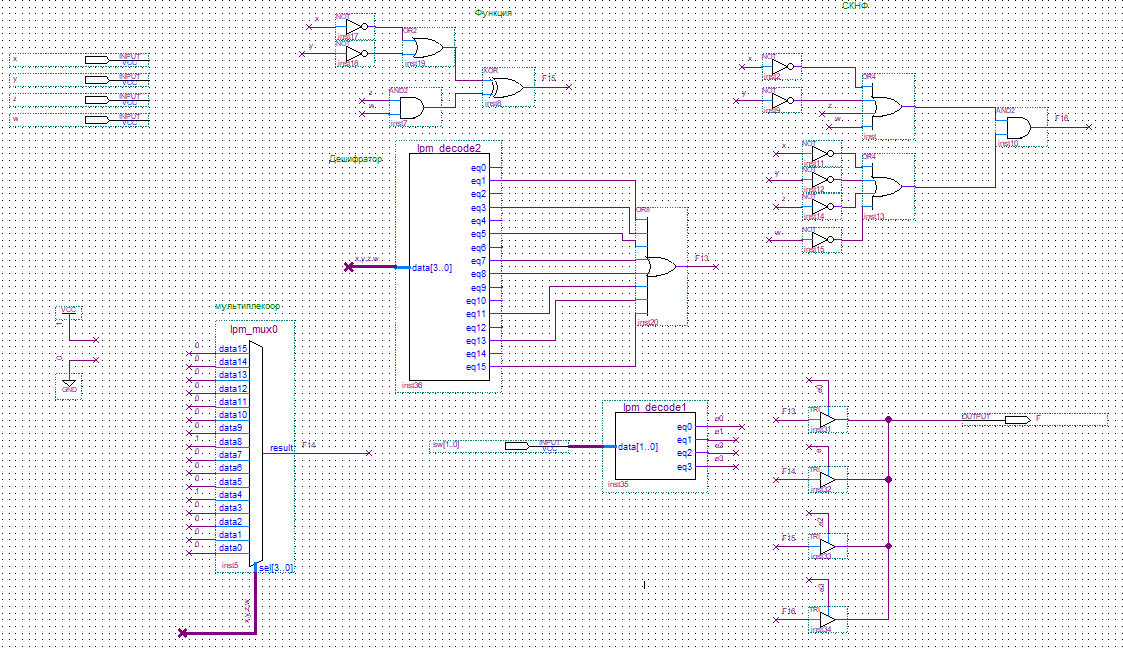

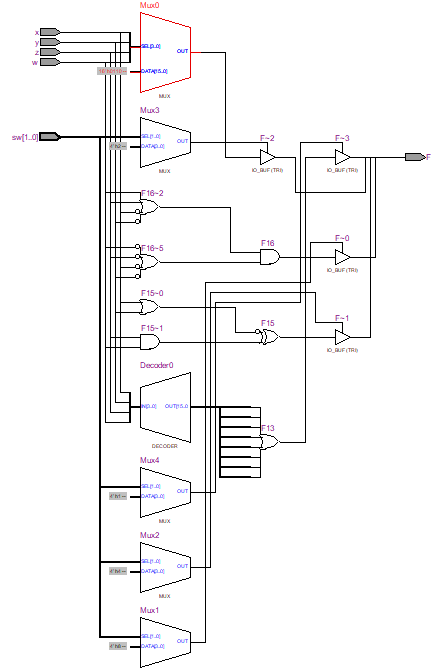

1 Реализация функций 16, 15, 14 и 13

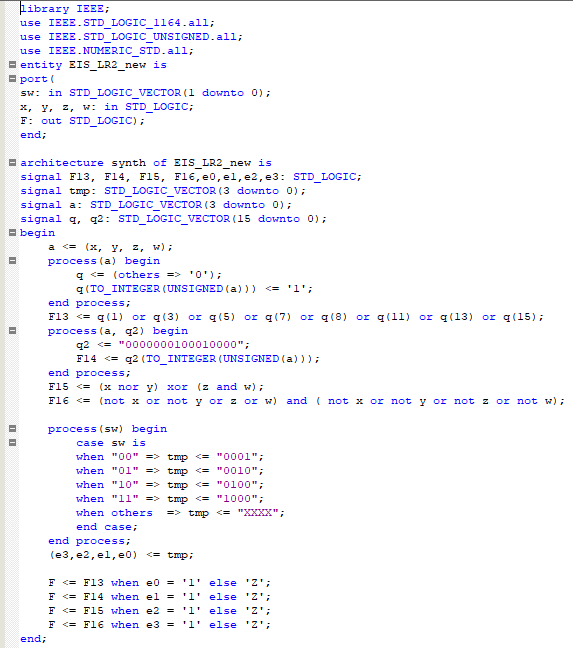

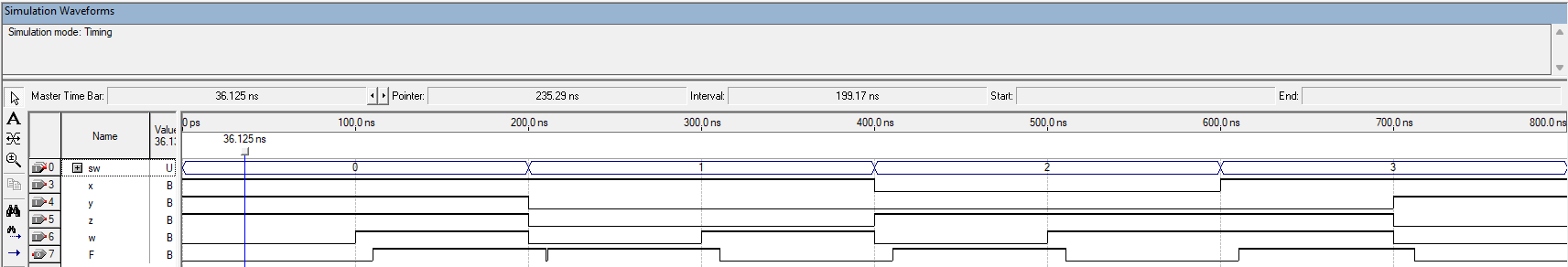

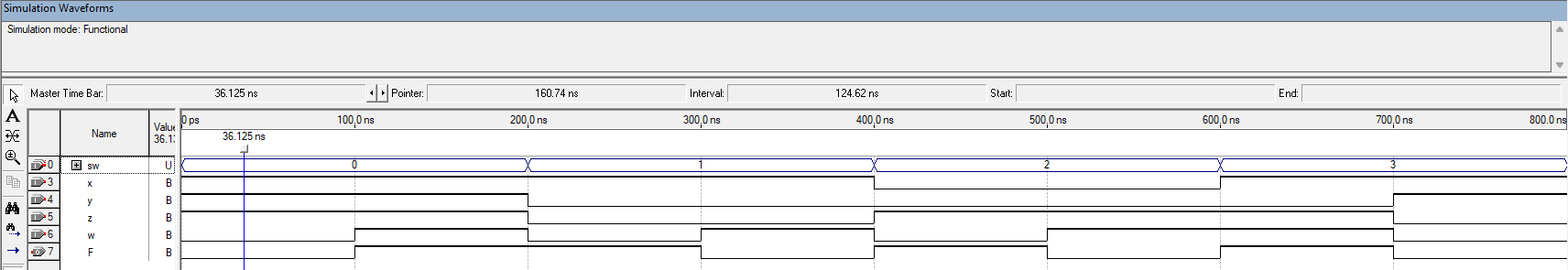

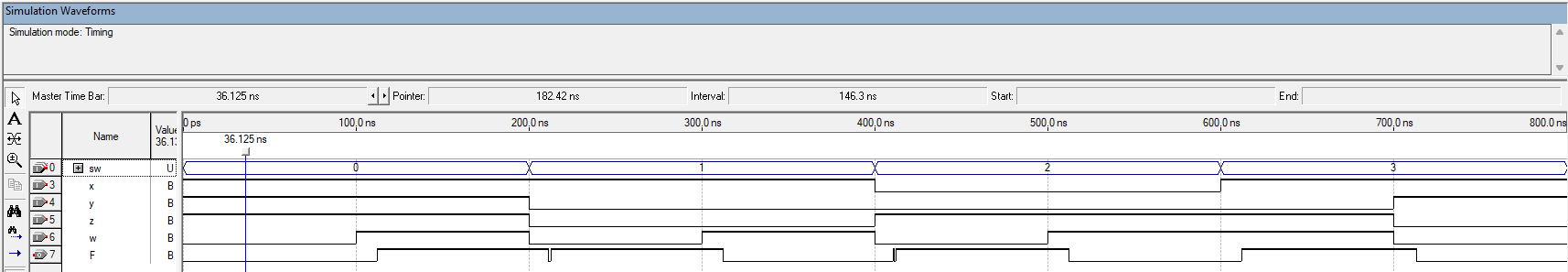

Для функций 16, 15, 14, 13 были собраны схемы на холсте .bdf (рис. 1.1) и описаны на VHDL (v1) (рис.1.2) Составлена таблица истинности. Функции были промоделированы в режимах «Timing» и «Functional» (рис. 1.3-1.6) Схема из RTL viewer для кода HDL представлена на рисунке 1.7

Выбор результата осуществлен при помощи tri_buf.

Из-за присутствующей задержки в режиме «Timing» происходят выходы

за границы интервала.

Формулы для вариантов 16, 15, 14, 13:

(1.1)

(1.2)

(1.3)

(1.4)

Р исунок

1.1 — Функции на холсте .bdf

исунок

1.1 — Функции на холсте .bdf

Рисунок 1.2 — Описание на VHDL (v1)

Р исунок

1.3 — Моделирование схемы «Timing»

исунок

1.3 — Моделирование схемы «Timing»

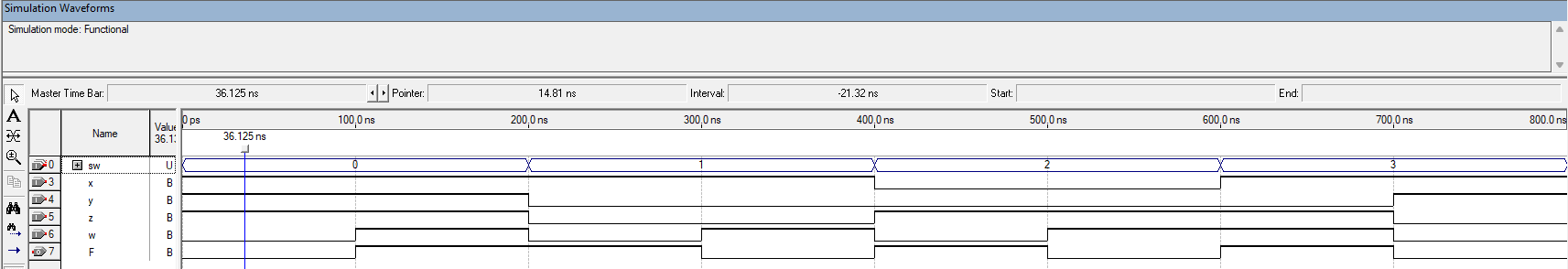

Р исунок

1.4 — Моделирование схемы «Functional»

исунок

1.4 — Моделирование схемы «Functional»

Р исунок

1.5

— Моделирование кода

«Timing»

исунок

1.5

— Моделирование кода

«Timing»

Р исунок

1.6

— Моделирование кода

«Functional»

исунок

1.6

— Моделирование кода

«Functional»

Рисунок 1.7 — Схема из RTL Viewer для кода

Таблица 1.1 — Таблица истинности

Входы |

Выходы |

||||||

x |

y |

z |

w |

F16 |

F15 |

F14 |

F13 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |