Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение

Высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра безопасности информационных систем (БИС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчёт по лабораторной работе №1

По дисциплине «Электроника и схемотехника»

Вариант №16

-

С

тудент

гр. 733-1

тудент

гр. 733-1Сметанников Д.Е

10 . 05 .2024

-

Руководитель

Доцент кафедры КИБЭВС, к.т.н., доцент

А.Н. Мальчуков

. .2025

Введение

Цель работы – изучить основные инструменты САПР QuartusII и научиться моделировать в ней работу схем на основе простых логических элементов.

Постановка задачи:

Собрать на холсте .bdf и промоделировать работу схемы 2И (AND), 2ИЛИ (OR), 2искл.ИЛИ (XOR), 2И-НЕ (NAND), 2ИЛИ-НЕ (NOR) и 2искл.ИЛИ- НЕ (XNOR).

Описать логические элементы на VHDL.

Собрать схему на отдельном холсте .bdf для выражения

Описать ее на VDHL.

Промоделировать её работу в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

Составить таблицу истинности для выражения из 16 варианта. Сверить результаты моделирования с составленной таблицей истинности.

Написать выводы о проделанной работе.

1 ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

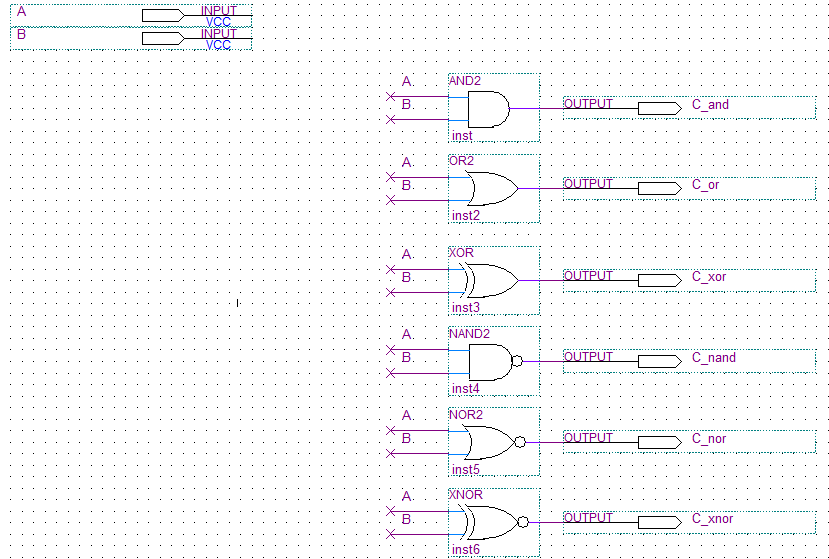

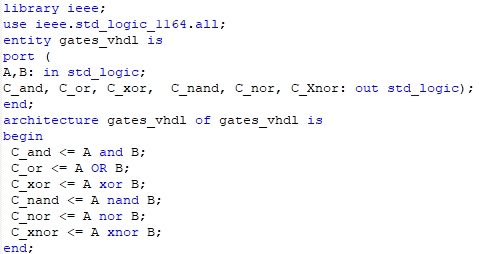

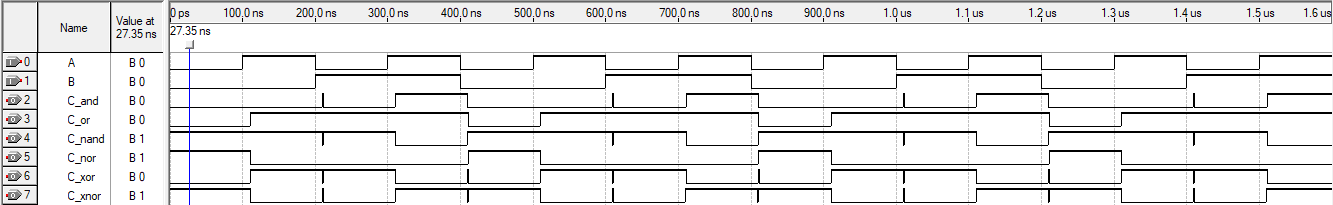

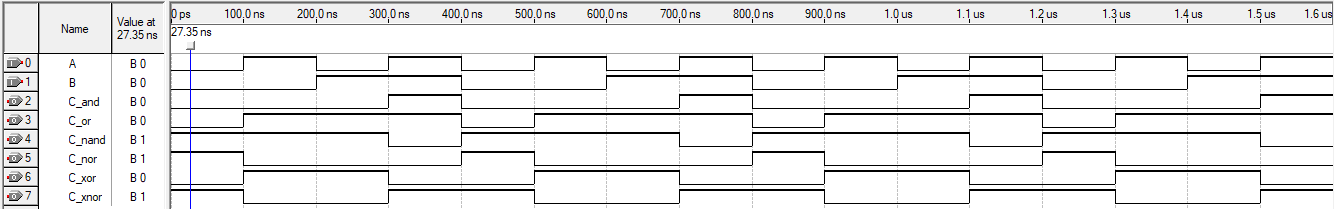

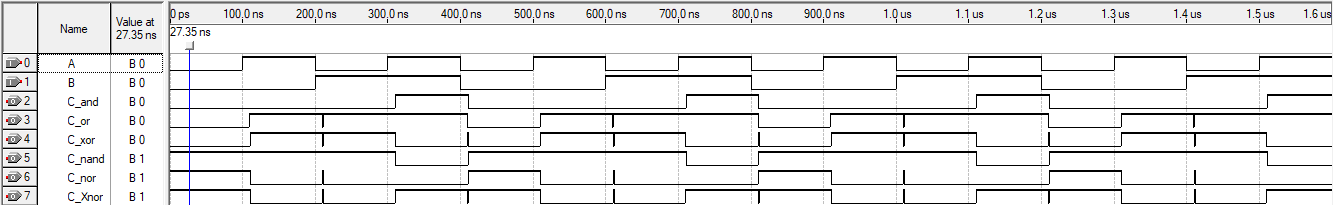

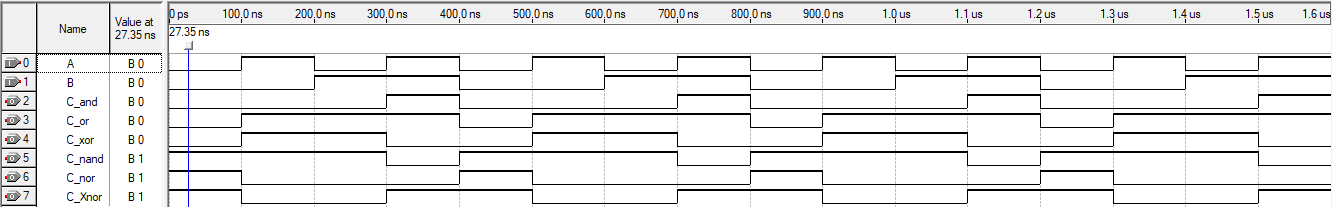

Для всех ЛЭ из задания были составлены схемы (рис. 1.1), описаны на VDHL (рис. 1.2) и промоделированы в режимах «Timing» и «Functional» (рис. 1.3-1.4). Также был промоделирован код на VHDL в режимах «Timing» и «Functional» (рис. 1.5-1.6)

Из-за присутствующей задержки в режиме «Timing» происходят выходы за границы интервала.

Р исунок

1.1 — Схемы ЛЭ

исунок

1.1 — Схемы ЛЭ

Рисунок 1.2 — Описание на VDHL

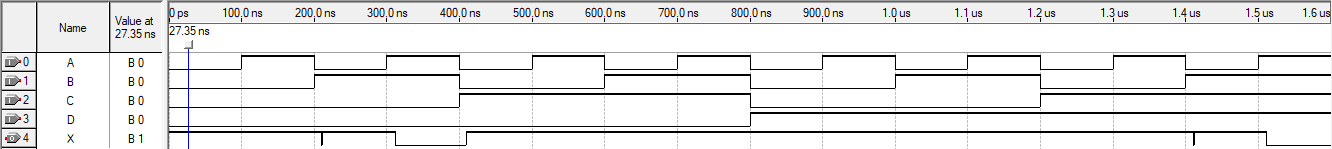

Р исунок

1.3 — Моделирование схемы «Timing»

исунок

1.3 — Моделирование схемы «Timing»

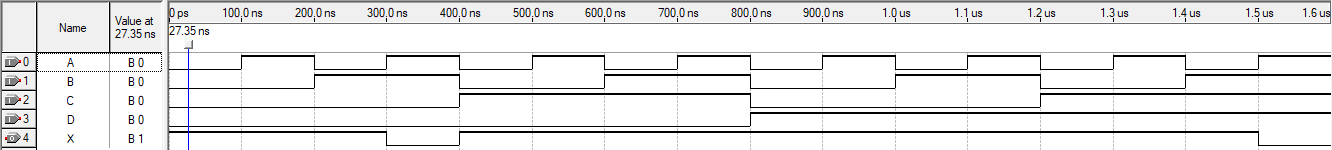

Р исунок

1.4 — Моделирование схемы «Functional»

исунок

1.4 — Моделирование схемы «Functional»

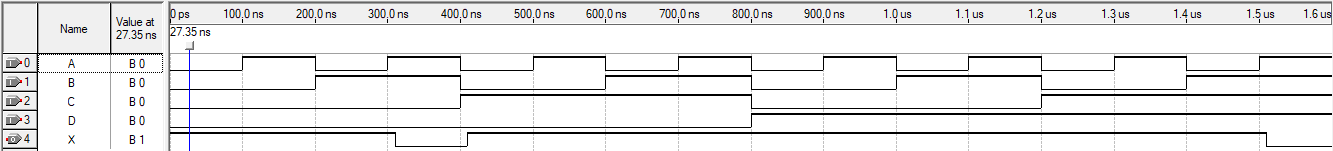

Р исунок

1.5

— Моделирование

кода «Timing»

исунок

1.5

— Моделирование

кода «Timing»

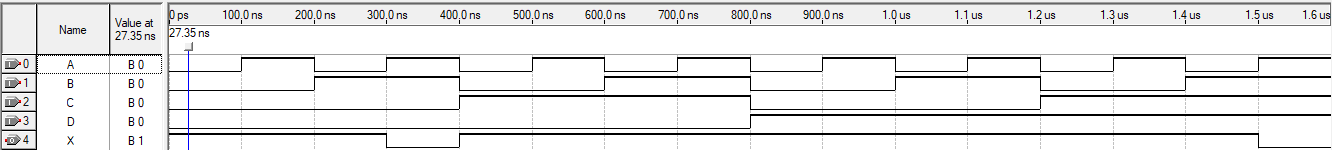

Р исунок

1.6

— Моделирование кода

«Functional»

исунок

1.6

— Моделирование кода

«Functional»

Таблица 1.1 — Таблица истинности

Входы |

Выходы |

||||||

A |

B |

AND |

NAND |

OR |

NOR |

XOR |

NXOR |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

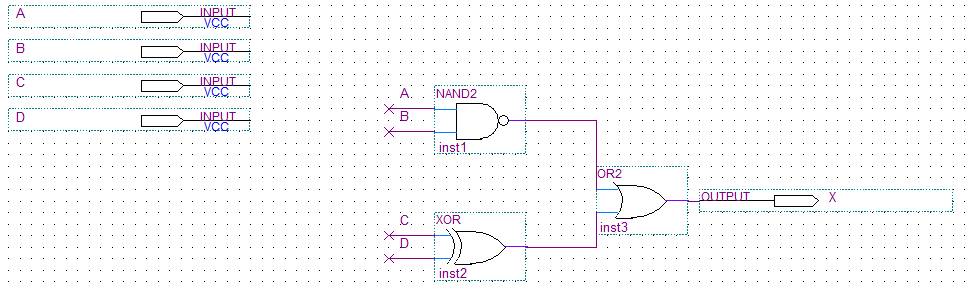

2 ФОРМУЛА СОГЛАСНО ВАРИАНТУ №16

Для формулы из варианта составлена схема (рис. 2.1), описана на VDHL (рис. 2.2), промоделирована в режимах «Timing» и «Functional» (рис. 3.3-3.4), составлена таблица истинности (рис. 3.5). Также был промоделирован код на VHDL в режимах «Timing» и «Functional» (рис. 3.6-3.7)

Из-за присутствующей задержки в режиме «Timing» происходят выходы за границы интервала.

Формула для 16 варианта:

(2.1)

Р исунок

2.1 — Схема для 16 варианта

исунок

2.1 — Схема для 16 варианта

Рисунок 2.2 — Описание на VDHL

Р исунок

2.3 — Моделирование схемы «Timing»

исунок

2.3 — Моделирование схемы «Timing»

Рисунок 2.4 — Моделирование схемы «Functional»

Р исунок

2.5 — Моделирование кода «Timing»

исунок

2.5 — Моделирование кода «Timing»

Р исунок

2.6 — Моделирование кода «Functional»

исунок

2.6 — Моделирование кода «Functional»

Таблица 2.1 — Таблица истинности

Входы |

Выход |

|||

A |

B |

C |

D |

X |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

Окончание таблицы 2.1

Входы |

Выход |

|||

A |

B |

C |

D |

X |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Заключение

В результате лабораторной работы были изучены основные инструменты САПР QuartusII, приобретены навыки моделирования работы схем.

Были собраны такие ЛЭ как: 2И (AND), 2ИЛИ (OR), 2искл.ИЛИ (XOR), 2И-НЕ (NAND), 2ИЛИ-НЕ (NOR) и 2искл.ИЛИ- НЕ (XNOR), а также смоделированы работы данных элементов. Были описаны все элементы с помощью VHLD. Составлена таблицы истинности.

Была собрана схема для выражения , смоделирована ее работа и написан код на VDHL. Была составлена таблица истинности. Значения совпали.

Из-за присутствующей задержки в режиме «Timing» происходят выходы за границы интервала.