1. Какие состояния выхода ИС Вы знаете?

Выходы интегральных схем могут быть в следующих состояниях:

Логические состояния:

1 — высокий уровень напряжения.

0 — низкий уровень напряжения.

Высокая импедансия (Hi-Z) — выход "отключен", не влияет на шину.

Короткое замыкание — выход подключён между высоким и низким уровнем.

2. Каким образом можно определить, совместимы ли ИС между собой?

Для определения совместимости ИС между собой нужно учесть:

Напряжения — ИС должны работать на одинаковых логических уровнях (например, 3,3 В или 5 В).

Типы сигналов — проверка соответствия типов входов/выходов (например, открытый коллектор vs. стандартный выход).

Частота и тайминг — синхронизация частот и временных характеристик.

Заземление — общее заземление для всех ИС.

3. На какие части условно разделяется базовый ЛЭ ТТЛ?

Входной буфер (или схема входа) — преобразует входной сигнал в формат, понятный для дальнейшей обработки, и усиливает его.

Фазорасщепляющий каскад

Выходной буфер — преобразует результат работы логической схемы в соответствующий выходной сигнал, усиливает его и обеспечивает его передачу на следующие уровни схемы.

4. Что такое соглашение положительной и отрицательной логики?

Положительная и отрицательная логика — это соглашения о том, какой уровень напряжения соответствует логическим значениям:

• Положительная логика: высокий уровень (High) = 1, низкий уровень (Low) = 0.

• Отрицательная логика: высокий уровень (High) = 0, низкий уровень (Low) = 1.

Пример:

• Положительная логика: 5 В = 1, 0 В = 0.

• Отрицательная логика: 5 В = 0, 0 В = 1.

Выбор зависит от устройства и условий эксплуатации.

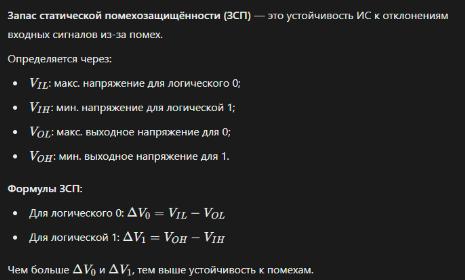

5. Что понимается под запасом статической помехозащищённости ИС? Как определить запасы статической помехозащищённости ИС?

6. В чём отличия 2С, ОК и 3С выходов ИС?

Основные отличия между 2С, ОК и 3С выходами интегральных схем (ИС):

1)2С (Двухтактный выход):

Использует два транзистора: один подключён к питанию, другой — к земле.

Обеспечивает высокий выходной ток как для логического "1", так и для логического "0".

Подходит для быстрого переключения и низкой нагрузки.

2)ОК (С открытым коллектором):

Выход транзистора соединён с коллектором, а нагрузка подключается внешне.

Требуется внешний подтягивающий резистор.

Поддерживает объединение выходов ("И"-функция) и гибкость подключения.

3)3С (Трёхсостоянный выход):

Может находиться в состояниях логической "1", "0" и высокоимпедансном (Hi-Z).

Используется для подключения нескольких устройств к одной шине данных.

Каждый тип подходит для разных задач в зависимости от требований к нагрузке, конфигурации и применению.

7. Перечислите логические функции, которые выполняют каскады базового ЛЭ ТТЛ.

НЕ (NOT) – Инверсия входного сигнала.

Выходной сигнал является инверсией входного.

И (AND) – Логическое умножение.

Выход высокий только тогда, когда все входы находятся в высоком уровне.

ИЛИ (OR) – Логическое сложение.

Выход высокий, если хотя бы один из входов находится в высоком уровне.

И-НЕ (NAND) – Инверсия логического И.

Выход низкий только тогда, когда все входы находятся в высоком уровне.

ИЛИ-НЕ (NOR) – Инверсия логического ИЛИ.

Выход высокий только тогда, когда все входы находятся в низком уровне.

Исключающее ИЛИ (XOR)

Выход высокий, если входные сигналы различны (один высокий, другой низкий).

Исключающее ИЛИ-НЕ (XNOR)

Инверсия XOR. Выход высокий, если входные сигналы одинаковы.

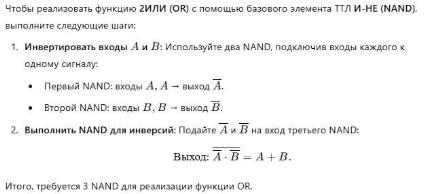

8. Расскажите, каким образом построить функцию 2ИЛИ, используя базовый ЛЭ ТТЛ.

9. Расскажите, каким образом построить функцию 2И, используя базовый ЛЭ ТТЛ.

10. Зачем в выходном каскаде базового ЛЭ ТТЛ необходим диод?

Диод в выходном каскаде ТТЛ предотвращает насыщение выходного транзистора, ускоряет переключение и стабилизирует напряжение. Это снижает время задержки и повышает скорость работы схемы.

11. Почему составной транзистор по схеме Дарлингтона может заменить связку транзистор + диод в выходном каскаде базового ЛЭ ТТЛ?

1)Дарлингтон уже имеет встроенный диодный эффект, благодаря последовательному соединению эмиттер-база двух транзисторов.

2)Увеличенное усиление: Дарлингтон обеспечивает высокий коэффициент усиления, как и связка транзистор + диод.

3)Компактность: Он упрощает схему, заменяя два отдельных элемента.

12. Чем ТТЛШ отличается от ТТЛ?

ТТЛШ (триггер транзисторно-транзисторной логики с шоттки) отличается от ТТЛ использованием шоттки-диодов, что повышает скорость работы и снижает потребление энергии. ТТЛШ быстрее и эффективнее в высокоскоростных схемах, но сложнее и дороже в производстве, в отличие от более простых и дешевых ТТЛ.