6 лаба цифра

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В. И. Ульянова (Ленина)

Кафедра РС

ОтЧЕТ

по лабораторной работе №6

по дисциплине «Цифровая электроника»

Тема: Создание регистра сдвига и дешифраторов с помощью пакета Quartus II

Санкт-Петербург

2025

Цель работы: научиться собирать схемы регистров сдвига и дешифраторов на пакете Verilog.

Выполнение работы:

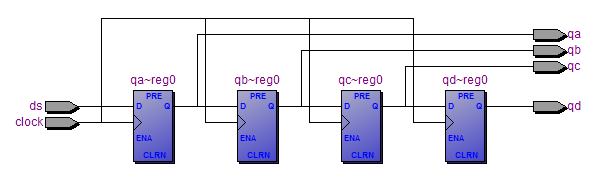

1. Четырехразрядный регистр сдвига

Рис

6.1.1 Собранная схема в редакторе Verilog

Рис

6.1.2

Схема в RTL-Viewer

Dffghdfgdfd

Рис

6.1.3 Временная диаграмма двоичного

четырехразрядного счетчика с задержками

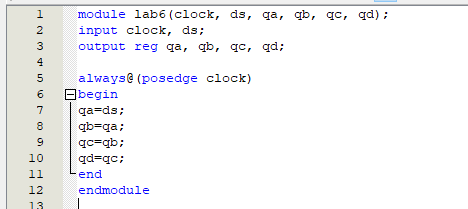

Неправильная версия регистра сдвига

Рис

6.1.4 Собранная схема в редакторе Verilog

1.5 Схема в RTL-Viewer

Рис

6.1.5

Схема в RTL-Viewer

В “неправильной версии” регистра сдвига на вход каждого триггера подается один и тот же сигнал, из-за чего отсутствуют задержки и, следовательно, смещения.

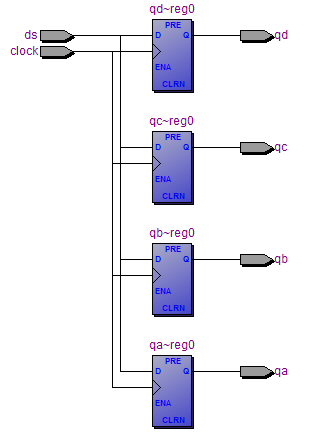

2.Дешифратор 2 х 4

2.1 Код на Verilog

Рис

6.2.1 Собранная схема в редакторе Verilog

2.2 Схема в RTL-Viewer

Рис

6.2.2

Схема в RTL-Viewer

2.3 Временная диаграмма (с задержками)

Рис

6.2.3

Временная диаграмма с задержками

Рис

6.2.4

Плата в Pin-Planner

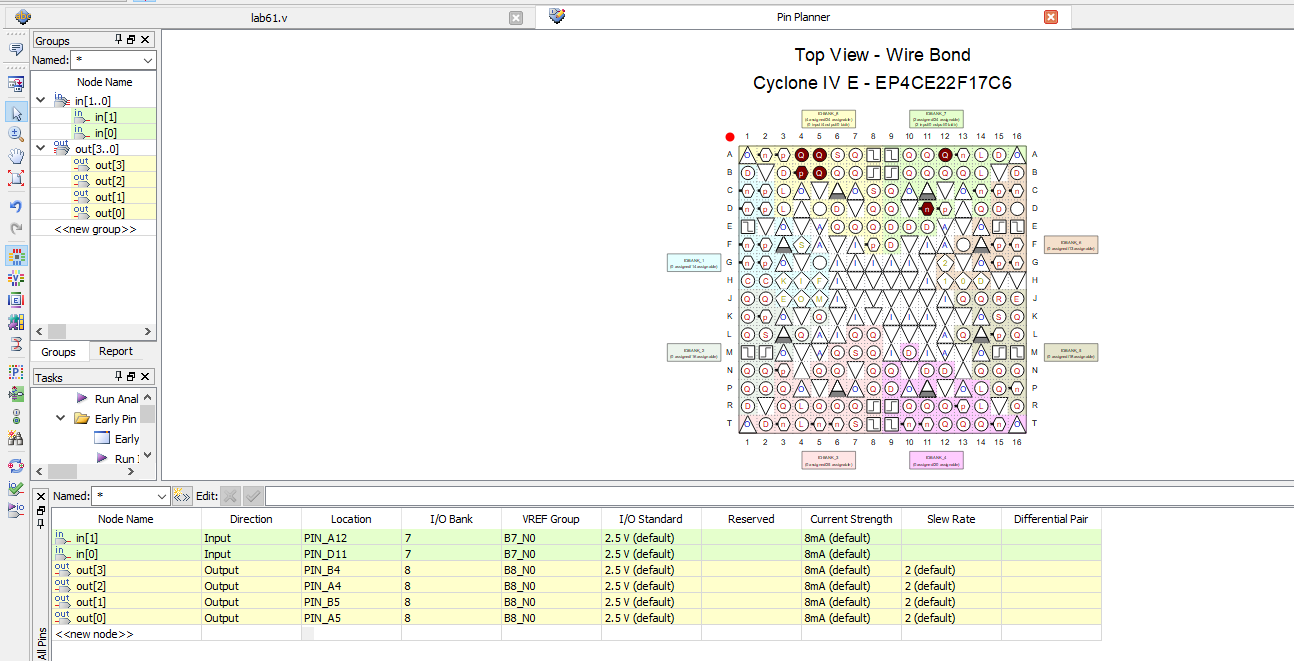

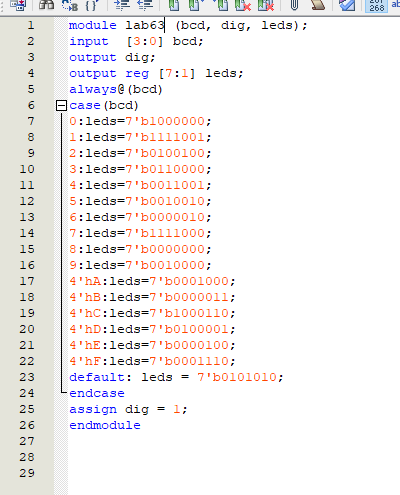

3.Дешифратор двоичного кода в код семисегментного индикатора

3.1 Код на Verilog

Рис

6.3.1 Собранная схема в редакторе Verilog

3.2 Собранная схема в компоненте RTL-Viewer.

Рис

6.3.2

Схема в RTL-Viewer

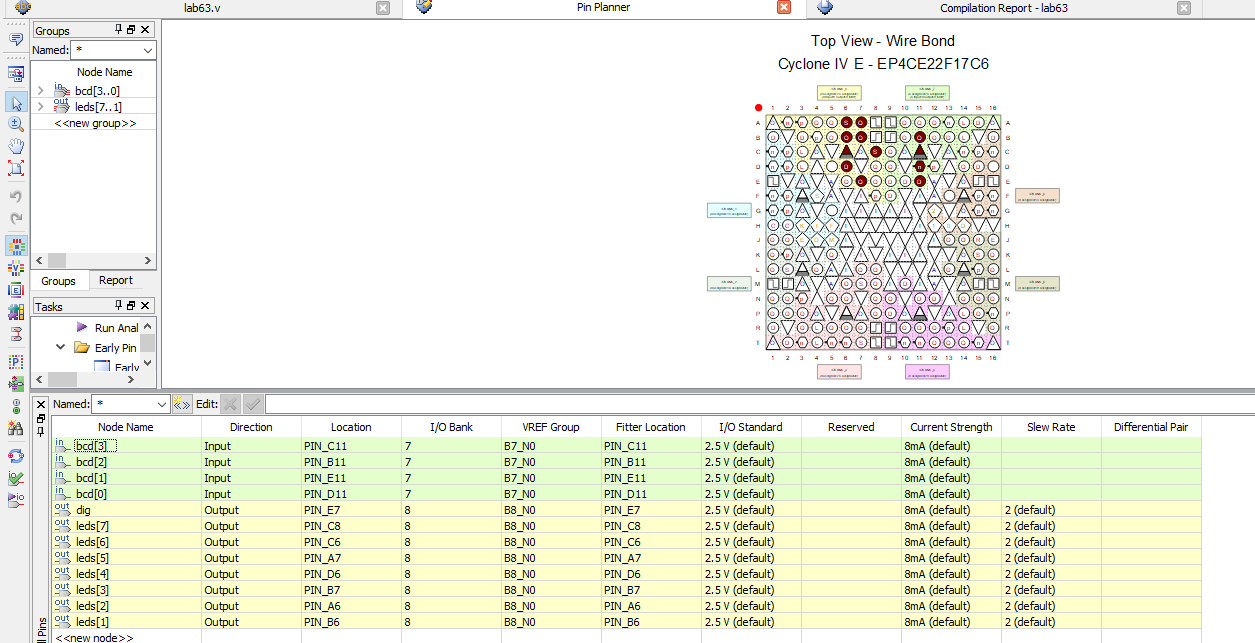

3.3 Запрограммированная плата Pin Planner

Рис

6.3.3

Плата в Pin

Planner

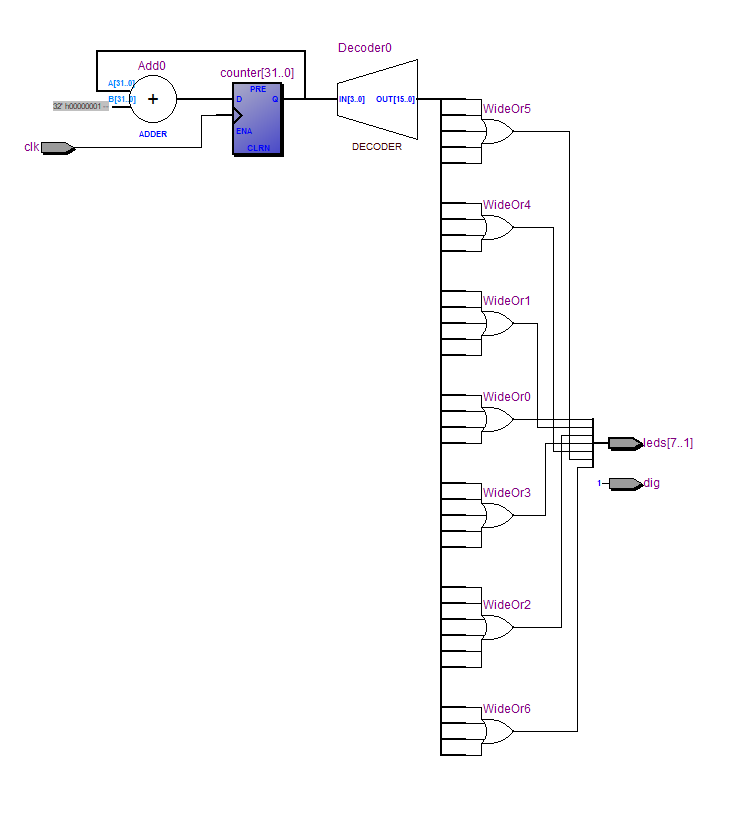

4.Дешифратор двоичного кода в код семисегментного индикатору со счетчиком

4.1. Код на Verilog

Рис

6.4.1 Собранная схема в редакторе Verilog

4.2. Схема в RTL-Viewer

Рис

6.4.2

Схема в RTL-Viewer

Рис

6.4.3

Плата в Pin

Planner

Выводы: в ходе выполнения лабораторной работы были изучены и собраны схемы четырехразрядного регистра сдвига, дешифратора 2 х 4, а также дешифратора двоичного кода в код семисегментного индикатора со счетчиком и без. Было установлено, что в регистре сдвига данные, проходя через каждый триггер, сдвигаются, за счет задержек. Дешифратор преобразует входящий двоичный сигнал в четырехразрядный унитарный. Дешифратор двоичного кода в код семисегментного индикатора преобразует двоичный код в наглядную цифру (или букву) на индикаторе, а добавление счетчика приводит к последовательному изменению отображаемой цифры от одного до 15 (E)