цифра 4 лаба готово

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В. И. Ульянова (Ленина)

Кафедра РС

ОтЧЕТ

по лабораторной работе №4

по дисциплине «Цифровая электроника»

Тема: Синхронные D- и JK- триггеры на языке Verilog

Санкт-Петербург

2025

Цель работы: научиться собирать схемы D- и JK- триггеров в текстовом редакторе Verilog, а также программировать соответствующие отладочные платы.

Выполнение работы:

D-триггер

1.1 Код на Verilog

Рис

1.1.1 Собранная схема в редакторе Verilog

Рис

1.1.2

Схема в RTL-Viewer

Dffghdfgdfd

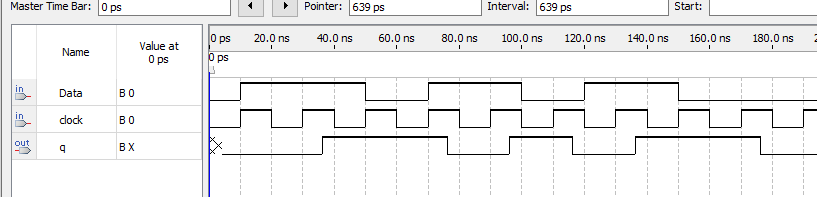

Рис

1.1.3 Временная диаграмма D-

триггера (без задержек)

Svdfsdfsdfgd

1.4 Временная диаграммы для собранной схемы (с задержками)

Рис

1.1.4 Временная диаграмма D-

триггера (с задержками)

1.5 Плата в Pin-Planner

Рис

1.1.5 Запрограммированная плата в редакторе

Pin

Planner

J-K – триггер

2.1 Код на Verilog

Рис

2.1.1 Собранная схема в редакторе Verilog

2.2 Собранная схема в компоненте RTL-Viewer

Рис

2.2.1

Схема в RTL-

Viewer

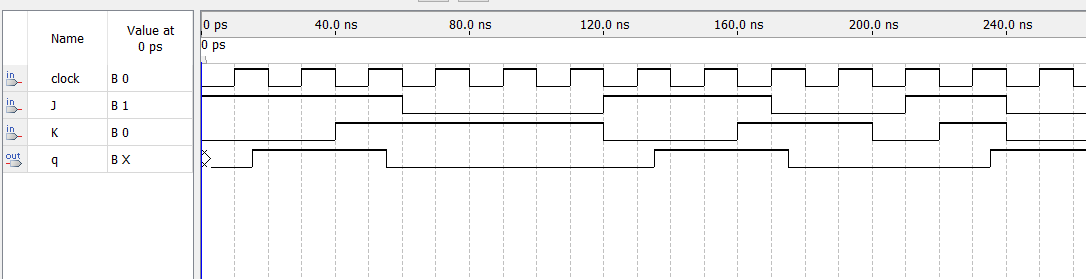

Рис

2.3.1 Временная диаграмма J-K

– триггера (без задержек)

Рис

2.4.1 Временная диаграмма J-K

– триггера (с задержками)

Рис

2.4.1 Временная диаграмма JK

– триггера (с задержками)

Рис

2.5.1 Запрограммированная плата J-K

– триггера в редакторе Pin

Planner

Устранение дребезга контактов J-K-триггера

3.1 Код на Verilog

Рис

3.1.1 Собранная схема в редакторе Verilog

3.2 Схема в RTL-Viewer

Рис

3.2.1 Схема в RTL

- Viewer

3.3 Плата в Pin – Planner

Рис

3.3.1 Запрограммированная плата J-K

– триггера с устранённым дребезгом

контактов в редакторе Pin

Planner

Вывод: в ходе выполнения лабораторной работы в текстовом редакторе Verilog были собраны схемы синхронных D- и JK- триггеров, а после были запрограммированы платы для них. D-триггер характеризуется тем¸ что значения входа D опрашиваются только в момент спада тактового сигнала. В отличие от D-триггера, JK-триггер позволяет изменять свое состояние в зависимости от комбинации входных сигналов J и K, а также сохранять предыдущее состояние или инвертировать его. В 3 пункте работы была собрана схема J-K- триггера с устранением дребезга контактов, которая приводила к двойному нажатию кнопок, и, следовательно, нарушению работы устройства.