цифра 2 лаба готово

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В. И. Ульянова (Ленина)

Кафедра РС

ОтЧЕТ

по лабораторной работе №2

по дисциплине «Цифровая электроника»

Тема: Создание простейшей схемы на Verilog в Quartus II

Санкт-Петербург

2025

Цель работы: научиться по заданной диаграмме Вейча находить МДНФ схемы, строить ее в графическом и текстовом редакторе, программировать отладочную плату для данной функции.

Задание:

Собрать схему (в графическом и текстовом редакторе), заданную диаграммой Вейча

Найти МДНФ переключательной функции

Построить таблицу истинности для заданной функции

Построить временные диаграммы при наличии и отсутствии задержек

Показать результат работы компонента RTL Viewer

Запрограммировать отладочную плату. При этом указать входные сигналы на SW5-8, выходной на LED1

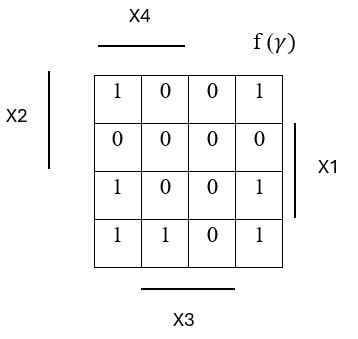

МДНФ переключательной функции

Таблица истинности для заданной функции

-

0

0

0

0

1

1

0

1

0

0

0

1

1

1

1

1

0

0

1

0

0

0

0

0

0

0

1

1

0

0

1

1

0

1

0

0

1

0

0

1

0

1

0

1

1

0

0

1

0

1

1

0

0

0

0

0

0

1

1

1

0

0

0

0

1

0

0

0

0

1

0

1

1

0

0

1

0

1

0

1

1

0

1

0

0

0

0

0

1

0

1

1

0

0

0

0

1

1

0

0

0

0

0

0

1

1

0

1

0

0

0

0

1

1

1

0

0

0

0

0

1

1

1

1

0

0

0

0

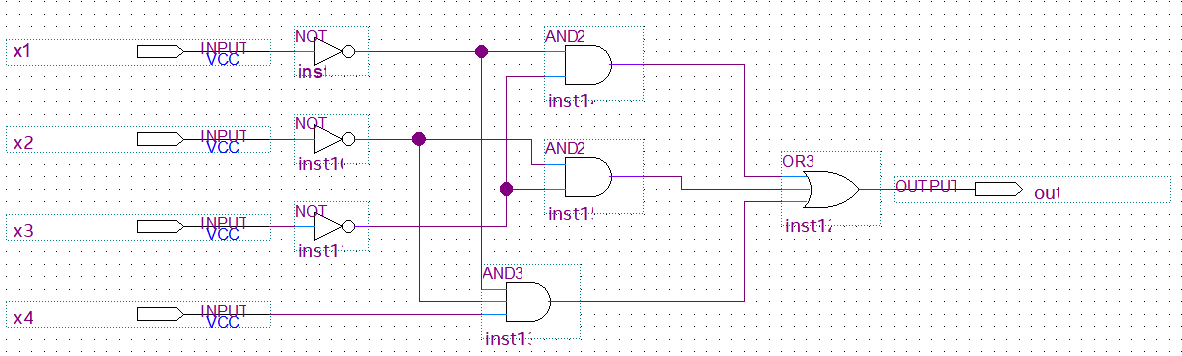

Рис

2.1. схема в графическом редакторе

Рис

2.2. схема в текстовом редакторе

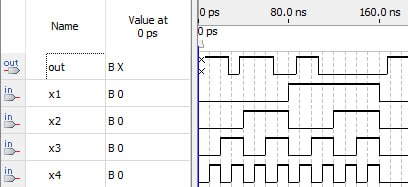

4.Временные диаграммы с задержками и без

Рис

2.3. Временная диаграмма без задержек

Рис

2.4. Временная диаграмма с задержками

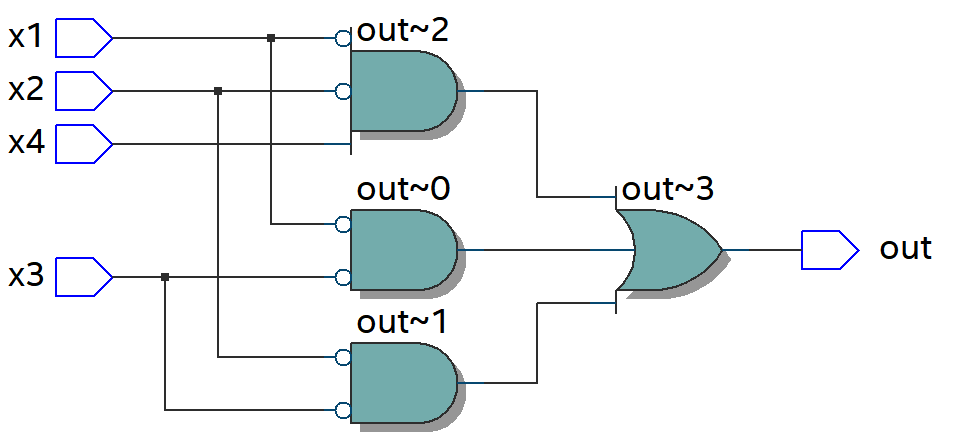

Рис

2.5. схема в RTL

Viewer

6. Программирование отладочной платы

Рис 2.6 Отладочная плата

Вывод:

в ходе выполнения лабораторной работы

была определена МДНФ некоторой функции

по схеме Вейча, построены таблица

истинности и временные диаграммы, а

также запрограммирована отладочная

плата. Получены навыки построения схемы

как в графическом редакторе, так и с

помощью текста в редакторе Verilog.

Использование текстового редактора

значительно удобнее, однако повышает

вероятность появления ошибок, связанных

с синтаксисом языка.