РГР / РГР Арифметика 4 вариант

.docxМинистерство науки и высшего образования РФ

Федеральное государственное автономное образовательное учреждение высшего образования

«Омский государственный технический университет»

Кафедра «Информатика и вычислительная техника»

ОТЧЁТ ПО РАСЧЕТНО-ГРАФИЧЕСКОЙ РАБОТЕ

по дисциплине «Арифметические и логические основы вычислительной техники»

«Разработка арифметико-логического устройства, выполняющего умножение старшими разрядами вперед в прямом коде»

студентки Бибиковой Анны Александровны ИВТ-245

Пояснительная записка

Шифр работы От-2068998-43-ИВТ-15-24 ПЗ

Направление 09.03.01

Доцент, к.т. Н Червенчук И. В.

Студентка Бибикова А.А.

Омск 2025

Реализация операции умножения старшими разрядами вперед в прямом коде

1. Множимое число А загружается в регистор RM1, множитель B загружается в регистр RM2, сумматор порядков SMP и SM обнуляются.

2. Выполняется сдвиг множителя RM2 вправо до тех пор, пока не будет достигнута последняя значащая цифра множителя RM2, то есть сдвигаем вправо до первого ненулевого бита.

3. Проверка старшего бита RM1[1]:

Теперь мы проверяем старший бит регистра RM1, который является самым значимым разрядом множимого числа A.

● Если старший бит RM1[1]=1, это означает, что текущий разряд множимого числа влияет на результат, и его нужно добавить в сумматор. В этом случае: добавляем RM2 (множитель) к сумматору SM.

● Если старший бит RM1[1]=0, то ничего не добавляем к сумматору SM, но продолжаем сдвигать регистр RM2.

4. Теперь сдвигаем содержимое регистра RM1 влево, чтобы подготовить его для анализа следующего разряда. После сдвига младший разряд регистра RM1 заполняется значением старшего разряда сумматора SM. Это важно, так как это позволяет перемещать биты в сторону старших разрядов, что позволяет правильно обрабатывать каждый разряд множимого числа A в процессе умножения.

5. После выполнения шагов 3–4 проверяем счётчик сдвигов Ст.

● Если счётчик сдвигов Ст=0, то процесс завершён, и мы добавляем к результату SM остаточное значение 2−(n+1) где n — количество разрядов. Это корректировка результата после завершения умножения.

● Если счётчик сдвигов Ст≠0, то возвращаемся к шагу 3 и повторяем процесс для следующего разряда.

6. После того как все разряды множителя B обработаны (когда счётчик сдвигов Ст достигнет 0), результат умножения будет находиться в сумматоре SM. Это финальный результат умножения чисел A и B.

Схемы алгоритма

На рисунке 1 представлена начальная часть алгоритма, где производится инициализация каждого структурного элемента устройства

Рисунок 1 - Часть схемы алгоритма умножения чисел, инициализация и проверка на ноль

На рисунке 2 показана часть алгоритма, отвечающая за работу с порядками. Поскольку мы умножаем два числа, мы должны сложить их порядки, однако при сложении может возникнуть переполнение порядков. Возможны два случая: переполнение со знаком «-», которое можно и нужно обрабатывать как машинный нуль, и переполнение со знаком «+», которое обрабатывается либо как фатальная ошибка, либо как машинная бесконечность (в зависимости от внутреннего представления числа в разрядной сетке вычислительного устройства).

Рисунок 2 - Часть схемы алгоритма умножения чисел, работа с порядками

На рисунке 3 изображён сам алгоритм умножения старшими разрядами вперёд.

Рисунок 3 – Часть схемы алгоритма умножения чисел, умножение старшими разрядами вперёд

На рисунке 4 показана нормализация числа. Нормализация проводится в зависимости от значений первых двух разрядов сумматора.

Рисунок 4- Часть схемы алгоритма умножения чисел, нормализация

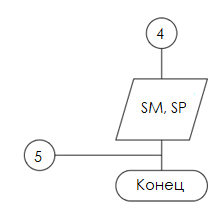

Рисунок 5 - Часть схемы алгоритма умножения чисел, вывод

Используемые обозначения

В символах схем алгоритмов применяются следующие обозначения:

Таблица 1 — Обозначения, используемые в символах схем алгоритмов

Обозначение |

Значение |

SM |

Сумматор мантисс |

SP |

Сумматор порядков |

RM |

Регистр мантисс |

RP |

Регистр порядков |

⊕ |

Операция «Исключающее ИЛИ» |

+= |

Сложение сумматора с регистром или неким заранее заданным значением |

++ |

Увеличение сумматора на 1 |

-- |

Уменьшение сумматора на 1 |

>>= n |

Сдвиг вправо на n бит |

<<= n |

Сдвиг влево на n бит |

= |

Сравнение с некоторым значением |

[n] |

Обращение к некоторому биту регистра или сумматора (индексация начинается с единицы) |

В структурных схемах не используются обозначения операций.

Пример выполнения операции

A B

B

mA=0,10111010 ; pA = 2;

mB=1,00111001; pB = 1;

SM = 0,00000000

SM=0,00000000 RM2=1,00111001

|

RM1= 0.10111010 Ст = 2 |

1) SM = 0.00000000 >RM2 = 0.10011100 |

|

|

<RM1 = 1.01110100 Ст = 1 |

2) SM = 0.00000000 + RM2 = 0.10011100 SM = 0.10011100 |

|

|

<RM1 = 0, 11101000 Cт = 0 |

3) SM = 0.10011100 >RM2 = 0.01001110 |

|

Ответ: mC =0.10011100; pC = 1

Список использованных источников

1. Потапов, В. И. Компьютерная арифметика и алгоритмическое моделирование арифметических операций [Электронный ресурс] : учеб. пособие для студентов по направлению 230100 "Информатика и вычислительная техника" / В. И. Потапов, О. П. Шафеева ; ОмГТУ. - Электрон. текстовые дан. (936 Кб). – Омск : Изд-во ОмГТУ, 2014. – 1 эл. опт. диск (CD-ROM).

2. Потапов, В. И. Компьютерная арифметика и алгоритмическое моделирование арифметических операций : учеб. пособие для вузов по направлению 230100 «Информатика и вычислительная техника» / В. И. Потапов, О. П. Шафеева. – Омск : Изд-во ОмГТУ, 2005. – 95 с.

3. Потапов, В. И. Основы компьютерной арифметики и логики : учеб. пособие для вузов по направлению 230100 «Информатика и вычислительная техника» / В. И. Потапов, О. П. Шафеева, И. В. Червенчук. – Омск : Изд-во ОмГТУ, 2004. – 172 с.

4. Червенчук И.В. метических устройств : метод. указания / Минобрнауки России, ОмГТУ ; [сост. И. В. Червенчук]. – Омск : Изд-во ОмГТУ, 2017. -33 c.