ЛР / МЭУ №5

.docxФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«Петербургский государственный университет путей сообщения

Императора Александра I»

(ФГБОУ ВО ПГУПС)

Факультет «Автоматизация и интеллектуальные технологии»

Кафедра «Автоматика и телемеханика на железных дорогах»

Специальность 23.05.05 Системы обеспечения движением поездов

Специализация Автоматика и телемеханика

Отчет по лабораторной работе

по дисциплине «Микроэлектронные устройства СЖАТ»

№5 «Исследование регистров»

Обучающийся Курс II Группа АТ-301 |

подпись, дата |

|

Преподаватель |

Отметка о зачете, подпись, дата |

доц. _____________ |

Санкт-Петербург

2025

Цель работы:

Ознакомление с основными функциями и тестирование регистров сдвига и памяти. В работе исследуется четырехразрядный, однонаправленный регистр сдвига с последовательным вводом и параллельным выводом информации. А также четырехразрядный регистр памяти с параллельным вводом и параллельным выводом информации.

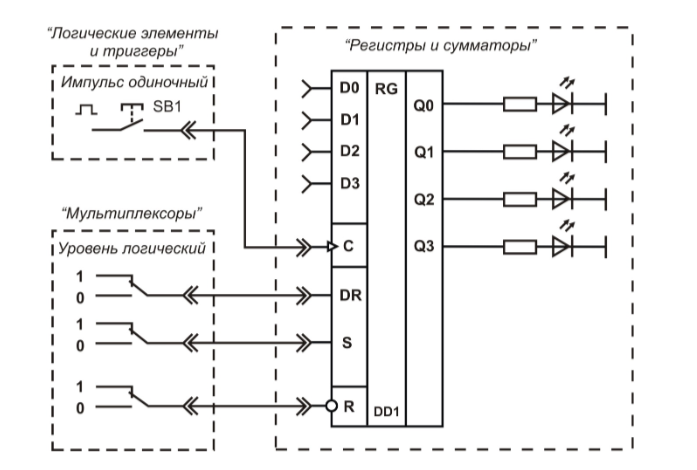

Принципиальные электрические схемы для выполнения экспериментов:

Рис. 1. Схема для исследования таблицы истинности регистра памяти.

Рис.2. Схема для исследования таблицы истинности регистра сдвига

Предварительное задание:

а) изучить тему курса «Регистры» и содержание данной работы, быть готовым ответить на все контрольные вопросы;

б) построить временные диаграммы сигналов на выходах Q1 – Q4 для заданной последовательности импульсов на входе C и напряжениях на входах S и R.

Результаты экспериментальных исследований:

Таблица 1. Таблица истинности для полного сумматора

Входы |

Выходы |

||||||||||

C |

D0 |

D1 |

D2 |

D3 |

DR |

R |

Q0 |

Q1 |

Q2 |

Q3 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

2 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

3 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

4 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

5 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

6 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

7 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

8 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

9 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

10 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

11 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

12 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

13 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

|

Таблица 2. Таблица рабочих состояний регистра сдвига.

Входы |

Выходы |

||||||

C |

S |

DR |

R |

Q0 |

Q1 |

Q2 |

Q3 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

2 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

3 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

4 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

5 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

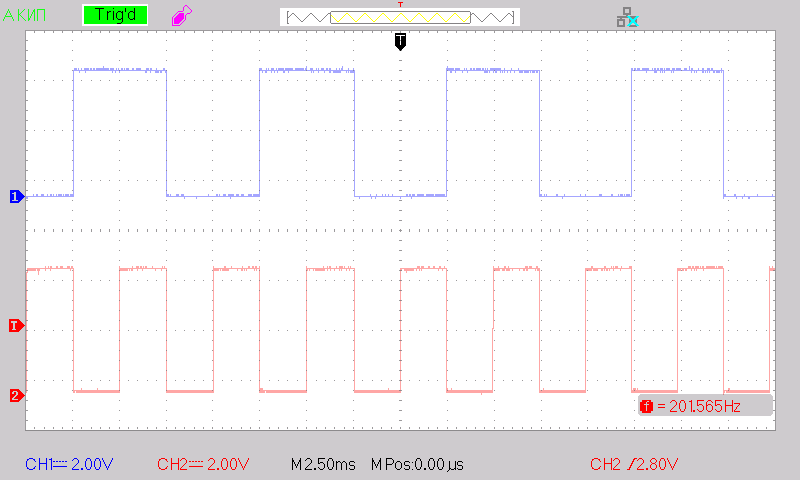

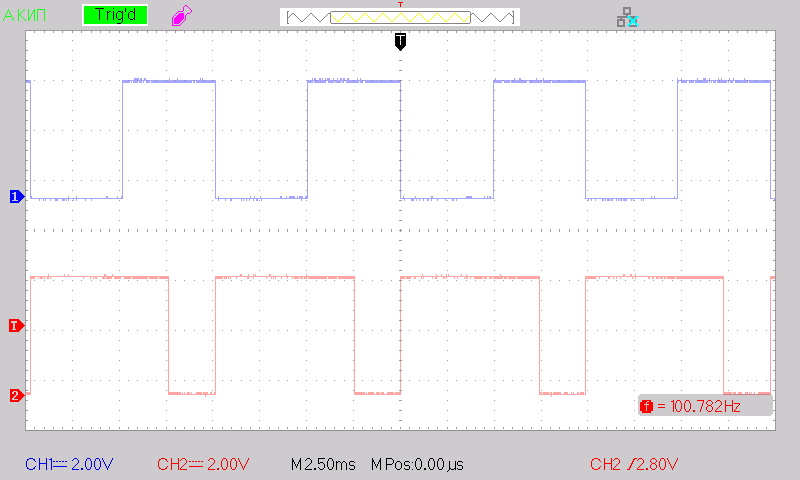

Обработанные осциллограммы:

Рис. 3. Осциллограмма ко входам R и D0

Рис. 4. Осциллограмма для выходов R и D1

Рис. 5. Осциллограмма для выходов R и D2

Рис. 6. Осциллограмма для выходов R и D3

Рис. 7. Осциллограмма для выходов R и C

Рис. 8. Осциллограмма для выходов R и C

Рис. 9. Осциллограмма для выходов R и C

Рис. 10. Осциллограмма для выходов R и C

Выводы:

В ходе лабораторной работы было проведено ознакомление с основными функциями и тестирование регистров сдвига и памяти. В работе исследуется четырехразрядный, однонаправленный регистр сдвига с последовательным вводом и параллельным выводом информации. А также четырехразрядный регистр памяти с параллельным вводом и параллельным выводом информации.

Были построены таблицы истинности и было определено, что регистр исправен.