ЛР / МЭУ №4

.docxФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«Петербургский государственный университет путей сообщения

Императора Александра I»

(ФГБОУ ВО ПГУПС)

Факультет «Автоматизация и интеллектуальные технологии»

Кафедра «Автоматика и телемеханика на железных дорогах»

Специальность 23.05.05 Системы обеспечения движением поездов

Специализация Автоматика и телемеханика

Отчет по лабораторной работе

по дисциплине «Микроэлектронные устройства СЖАТ»

№4 «Исследование сумматоров»

Обучающийся Курс II Группа АТ-301 |

подпись, дата |

|

Преподаватель |

Отметка о зачете, подпись, дата |

доц. _____________ |

Санкт-Петербург

2025

Цель работы:

Ознакомление с основными функциями и тестирование полусумматора и полного сумматора. В работе исследуется полный четырехразрядный сумматор со сквозным переносом, внутренняя структура которого построена на основе КМОП-логики.

Принципиальные электрические схемы для выполнения экспериментов:

Рис. 1. Схема соединений для тестирования сумматора.

Предварительное задание:

а) изучить тему курса «Сумматоры» и содержание данной работы, быть готовым ответить на все контрольные вопросы;

б) на рис.2 приведена комбинационная схема полусумматора на элементах И-НЕ, используя другие логические элементы, постарайтесь упростить схему. Решение нарисовать и привести в качестве доказательства таблицу истинности выходных и промежуточных сигналов. Результат должен иметь возможность реализации на рабочем поле (рис. 1). в) согласно таблице вариантов (табл.3) разработать схему заданного типа сумматора, для реализации использовать элемент DD2.

Рис. 2. Полусумматор на основе элементов И-НЕ и НЕ

Результаты экспериментальных исследований:

Таблица 1. Таблица истинности для полного сумматора

Входы |

Выходы |

|||||||||||||

A1 |

B1 |

A2 |

B2 |

A3 |

B3 |

A4 |

B4 |

Pin |

S1 |

S2 |

S3 |

S4 |

Pout |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

Входы |

Выходы |

||||||||||||

A1 |

B1 |

A2 |

B2 |

A3 |

B3 |

A4 |

B4 |

Pin |

S1 |

S2 |

S3 |

S4 |

Pout |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

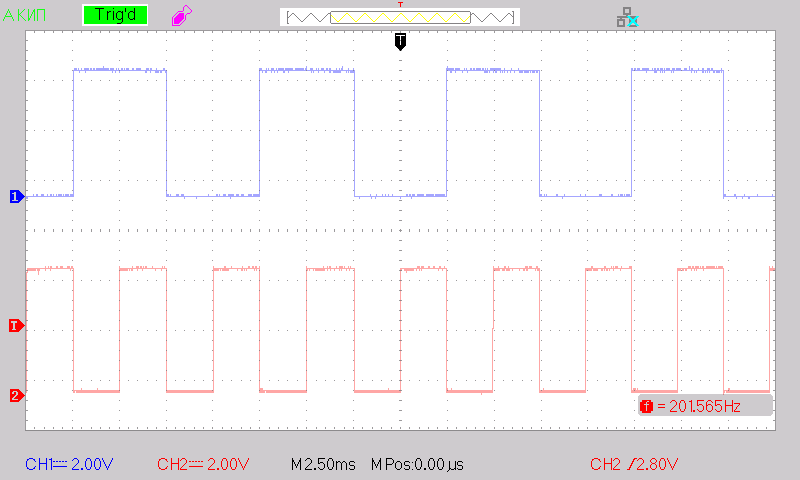

Обработанные осциллограммы:

Рис. 3. Осциллограмма ко входам A1 и B1

Рис. 4. Осциллограмма для выходов S1 и S2

Выводы:

В ходе лабораторной работы было проведено ознакомление с основными функциями сумматора и тестирование полусумматора и полного сумматора. Также был исследован полный четырехразрядный сумматор со сквозным переносом, внутренняя структура которого построена на основе КМОП-логики.

Были построены таблицы истинности и было определено, что сумматор исправен.

Осциллограмма на входах 𝐴1 и 𝐵1 показывает изменение логических уровней во времени. Судя по таблице истинности, входные сигналы должны соответствовать бинарным значениям, используемым в работе сумматора.

Осциллограмма выходов S1 и S2 должна соответствовать ожидаемым результатам суммирования, приведённым в таблице истинности. Если на осциллограммах нет искажений или аномалий (например, задержек, всплесков или дрожания уровней), можно сделать вывод, что сумматор функционирует корректно. При наличии отклонений от идеальных прямоугольных импульсов возможно влияние паразитных эффектов (например, переходных процессов в КМОП-логике).