практика

.docx

Цель работы: знакомство с особенностями работы приложения Quartus ⅠⅠ 9.0 в процессе моделирования цифровых устройств на ПЛИС.

Ход работы:

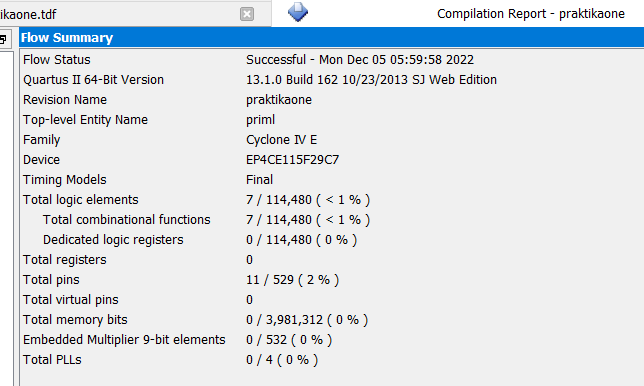

1. Был открыт созданный в первой работе файл, используемый для синтеза дешифратора семисегментного индикатора. Далее выполнена компиляция и зафиксированы назначения аппаратной реализации проекта, сделанные по умолчанию системой Quartus ⅠⅠ. Определен тип микросхемы – EP4CE115F29C7, загрузка ее макроячеек, требуемое количество ресурсов и топология размещения входных и выходных выводов.

Рисунок 1. Фиксация параметров

Рисунок 2. Назначение пинов

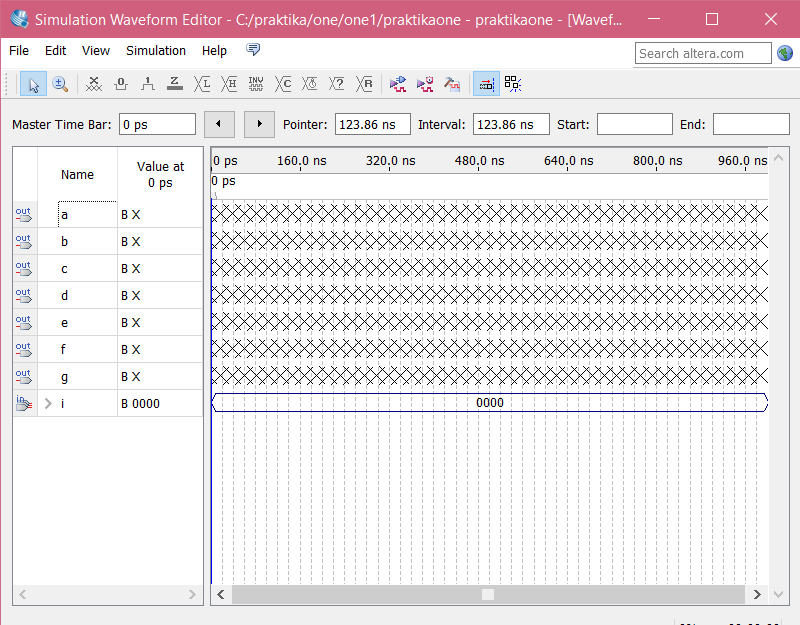

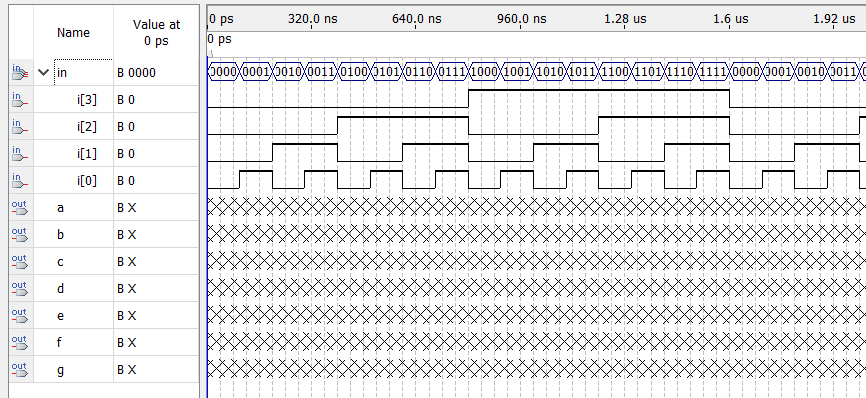

2. Подключен сигнальный редактор Waveform Editor. Сделаны назначения входных сигналов индивидуально для каждого входа, установив на них уровни логической единицы в течение следующих интервалов времени: i0 – 100 нс, i1 – 200 нс, i2 – 300 нс, i3 – 400 нс.

Рисунок 3. Node Finder

Рисунок 4. Созданный проект

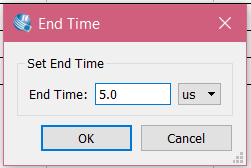

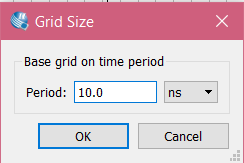

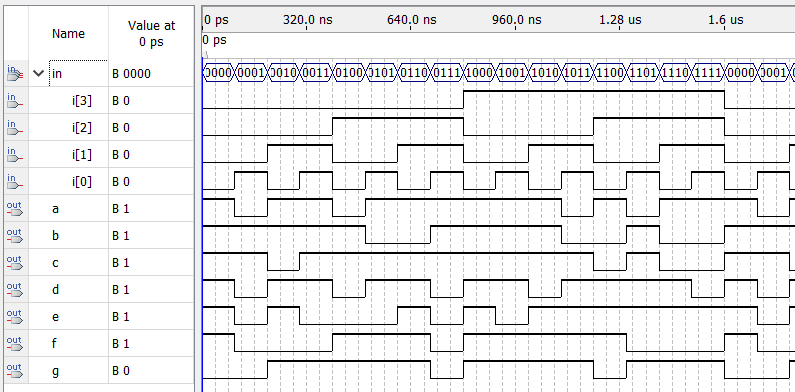

3. Изменено общее время моделирования с 1 мкс на 5 мкс. В окне редактора Waveform Editor представлены входные сигналы в составе группы. Используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 1 и временные интервалы 100 ns.

Рисунок 5. Время моделирования

Рисунок 6. Шаги изменения состояния

Рисунок 7. Модель

Рисунок 8. Моделирование

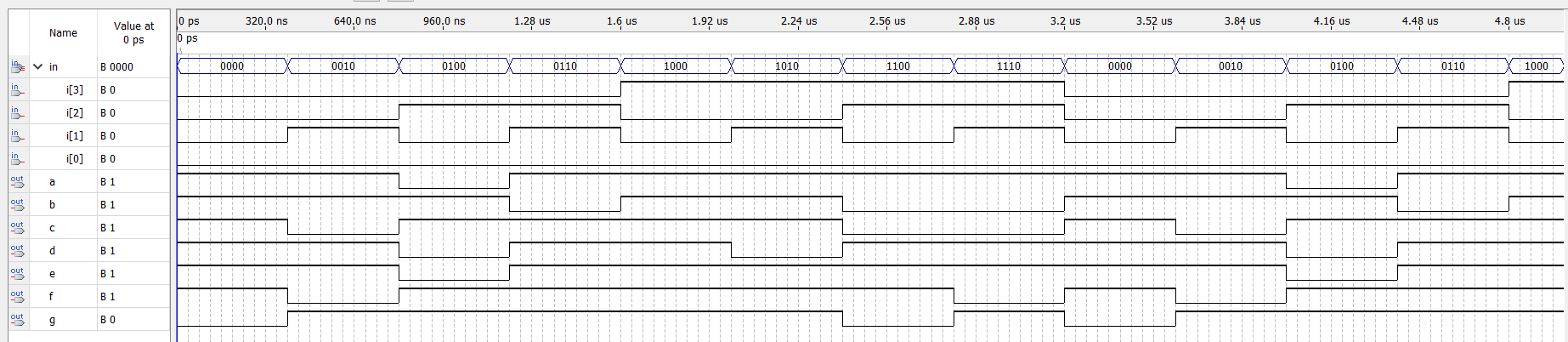

4. Используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 2 и временные интервалы 400 мкс.

Рисунок 9. Шаг инкремента

Рисунок 10. Модель

Рисунок 11. Моделирование

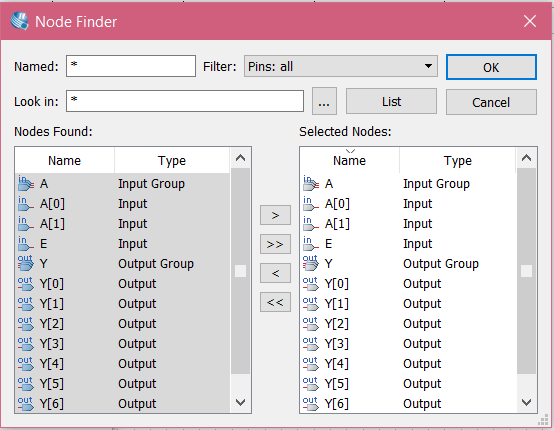

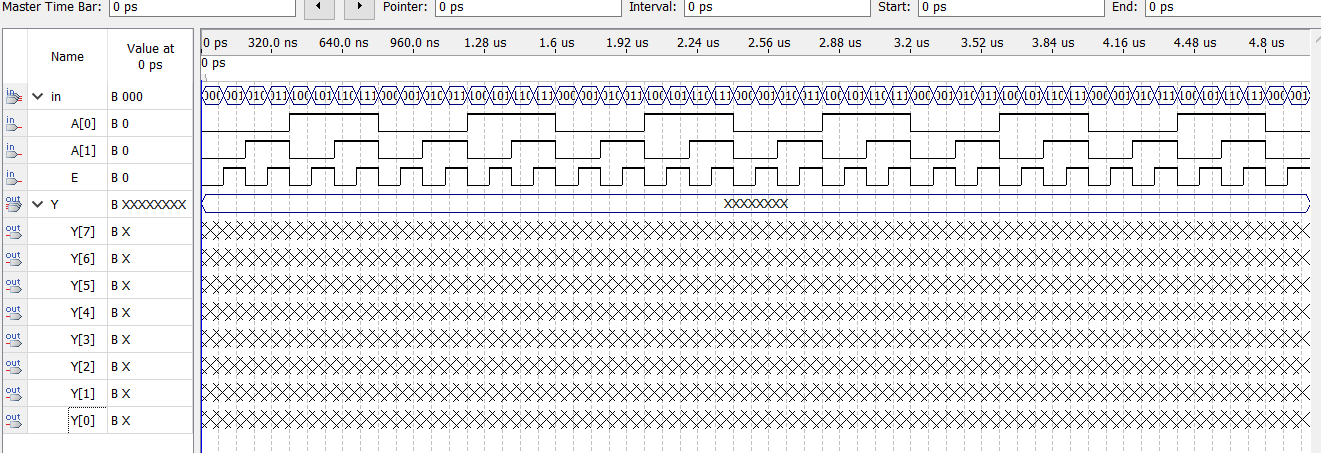

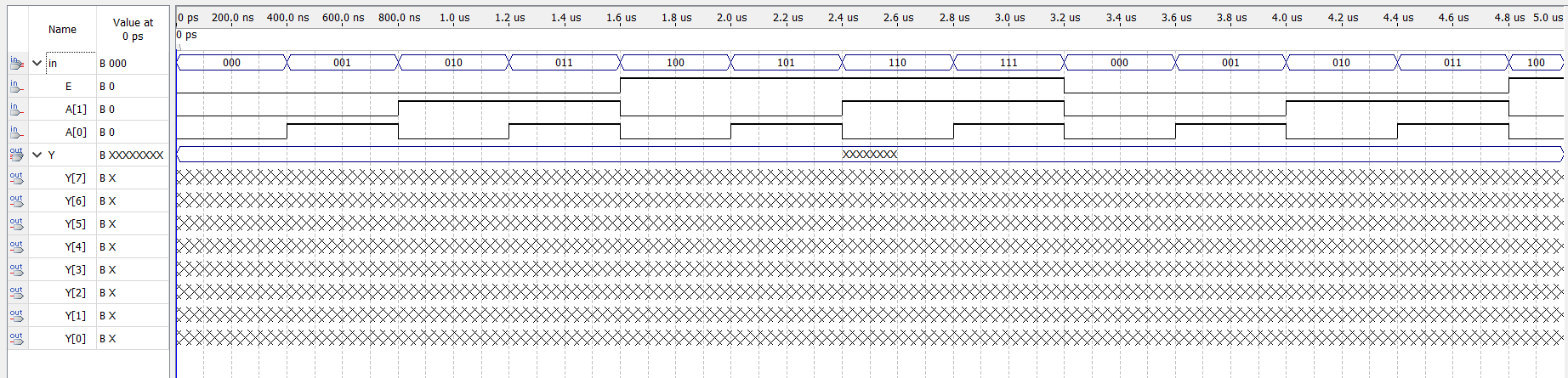

5. Аналогично выполнены шаги для схемы 1 из первой лабораторной работы. Подключен сигнальный редактор Waveform Editor для схемы 1. Выполнено назначение входных сигналов индивидуально для каждого входа, установив на них уровни логической единицы в течение следующих интервалов времени: A0 - 300 нс, A1 - 200 нс, E - 100 нс. Используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 1 и временные интервалы 100 мкс.

Рисунок 12. Схема 1, Node Finder

Рисунок 13. Модель схемы 1

Рисунок 14. Моделирование схемы 1

Далее, изменено используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 2 и временные интервалы 400 мкс.

Рисунок 15. Модель схемы 1

Рисунок 16. Моделирование схемы 1

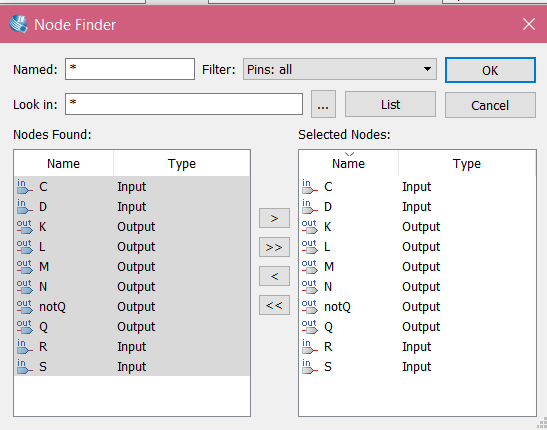

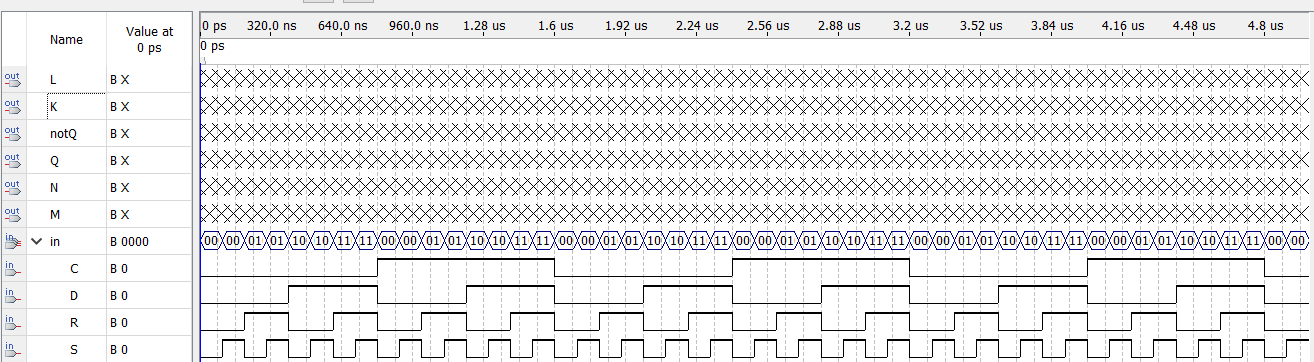

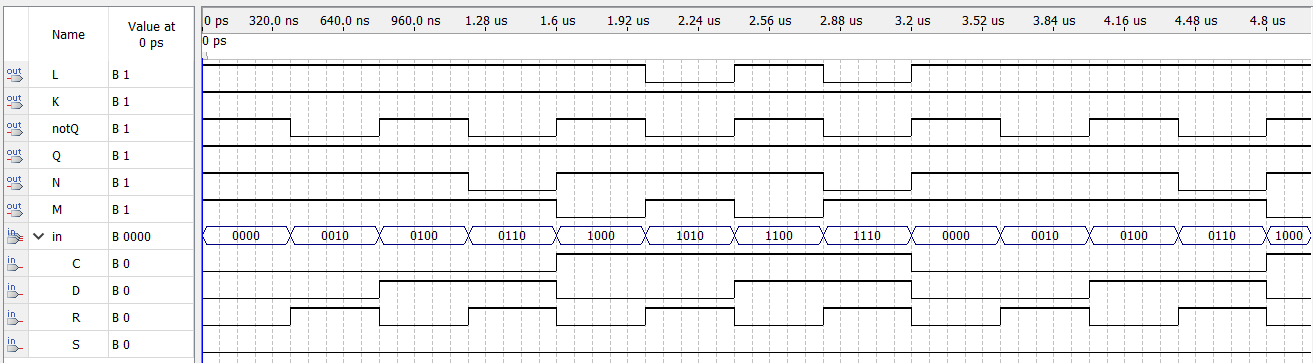

Аналогично выполнены шаги для схемы 2 из первой лабораторной работы. Подключен сигнальный редактор Waveform Editor для схемы 2. Выполнено назначение входных сигналов индивидуально для каждого входа, установив на них уровни логической единицы в течение следующих интервалов времени: : S - 100 нс, R - 200 нс, D - 300 нс, C – 400 нс. Далее, изменено общее время моделирования с 1 мкс на 5 мкс, а также шаги изменения состояния 10 ns. Используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 2 и временные интервалы 400 мкс.

Рисунок 17. Схема 2, Node Finder

Рисунок 18. Модель схемы 2

Рисунок 19. Моделирование схемы 2

Далее, изменено используя назначения счетчика генератора входных сигналов, установлен шаг изменения инкремента 2 и временные интервалы 400 мкс.

Рисунок 20. Модель схемы 2

Рисунок 21. Моделирование схемы 2

Вывод: в ходе лабораторной работы мы познакомились с особенностями работы приложения Quartus ⅠⅠ 9.0 в процессе синтеза цифровых устройств на ПЛИС.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Программируемые логические интегральные схемы (часть I): учеб. пособие / А.С. Ашихмин; Рязан. гос. радиотехн. акад. - Рязань, 2005. -88 с.

2. Антонов А.П. Язык описания цифровых устройств AlteraHDL. Практический курс. 2-е изд., стереотип. - М.: ИП РадиоСофт, 2002. - 224 с.

3. Комолов Д.А., Мяльк Р.А., Зобенко А.А., Филиппов А.С. Системы автоматизированного проектирования фирмы Altera MAX+plus II и Quartus II. Краткое описание и самоучитель. - М.: ИП РадиоСофт, 2002. - 284 с.