6 практика

.docx

МИНОБРНАУКИ РОССИИ

Федеральное государственное бюджетное образовательное учреждение высшего образования

«МИРЭА - Российский технологический университет» РТУ МИРЭА

Институт Информационных Технологий Кафедра Вычислительной Техники (ВТ)

ОТЧЁТ ПО ПРАКТИЧЕСКОЙ РАБОТЕ №6

«Делитель частоты» по дисциплине

«Архитектура вычислительных машин и систем»

Выполнил студент группы

ИВБО-XX-XX

Принял ассистент кафедры ВТ Дуксина И.И.

Практическая работа выполнена « » 2025 г.

«Зачтено» « » 2025 г.

Москва 2025

АННОТАЦИЯ

Данная работа включает в себя 2 рисунка, 3 листинга. Количество страниц в работе — 10.

СОДЕРЖАНИЕ

СОДЕРЖАНИЕ 2

1 ПОСТАНОВКА ЗАДАЧИ 5

2 ПРОЕКТИРОВАНИЕ И РЕАЛИЗАЦИЯ 6

2.1 Реализация параметрического универсального реверсивного счетчика 6

2.2 Реализация делителя частоты на 248 6

3 ВЕРИФИКАЦИЯ 8

3.1 Реализация тестового модуля 8

ЗАКЛЮЧЕНИЕ 10

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 11

Verilog HDL — это язык описания аппаратуры, используемый для описания и моделирования электронных систем. Verilog HDL наиболее часто используется в проектировании, верификации и реализации (например, в виде СБИС) аналоговых, цифровых и смешанных электронных систем на различных уровнях абстракции [1].

Под счётчиком понимается цифровой автомат, предназначенный для подсчёта входных импульсов, поступающих на специальный вход, именуемый счётным. Состояние такого цифрового автомата коррелирует с количеством поступивших импульсов.

Одним из вариантов использования счётчика является устройство делителя частоты. Суть заключается в следующем: некоторый периодический сигнал(например, сигнал синхронизации) имеет определённую частоту изменения своего уровня; некоторые устройства для участия в алгоритме решения задачи должны изменять своё состояние, например, раз в 20 единиц времени. Создавать в рамках схемы отдельный синхросигнал, не связанный с основным – плохая идея, поскольку это может привести к рассинхронизации из за физических процессов, уникальных для каждого сигнала. Решением такой проблемы будет замедление основного сигнала синхронизации в 20/10 = 2 раза. Устройство, позволяющее произвести такую манипуляцию, называется делителем частоты [1].

ПОСТАНОВКА ЗАДАЧИ

Спроектировать универсальный параметрический схемотехнический узел — счётчик — при помощи Verilog HDL. Произвести верификацию полученного устройства средствами САПР Vivado. На основе разработанного модуля счётчика создать модуль делителя частоты. Произвести верификацию полученного устройства средствами САПР Vivado. Подготовить отчёт о проделанной работе.

Индивидуальный вариант: Делитель частоты на 248.

ПРОЕКТИРОВАНИЕ И РЕАЛИЗАЦИЯ

Реализация параметрического универсального реверсивного счетчика

При помощи языка описания аппаратуры Verilog средствами САПР Vivado реализуем параметрический счетчик. Результат представлен в Листинге 2.1.

Листинг 2.1 — Модуль count.v – Реализация параметрического универсального реверсивного счетчика

`timescale 1ns / 1ps

module count#(step = 1, mod = 248)(

input dir,clk,

output reg [$clog2(mod)-1:0] out

);

initial

out = 0;

always@(posedge clk)

begin

if (dir == 0)

out = (out + step) % mod;

else

out = (out- step) % mod;

end

endmodule

Реализация делителя частоты на 248

При помощи языка описания аппаратуры Verilog средствами САПР Vivado реализуем делитель частоты на 248. Результат представлен в Листинге 2.2.

Листинг 2.2 — Модуль delitel.v – Реализация делителя частоты на 248

`timescale 1ns / 1ps

module delitel(

input clk,

output reg out

);

wire [6:0] out_count;

initial

out = 0;

count#(.mod(248)) count2(.clk(clk), .dir(0), .out(out_count) );

always@(negedge clk)

begin

if(out_count == 0)

out = ~out;

end

endmodule

ВЕРИФИКАЦИЯ

Реализация тестового модуля

Произведем верификацию модулей counter.v и delitel.v для этого создадим модуль test.v. Результат представлен в Листинге 3.1.

Листинг 3.1 — Модуль test.v – Реализация тестового модуля

`timescale 1ns / 1ps

module test();

reg clk = 0;

reg clk_ref = 0;

reg dir = 1;

wire [6:0] out;

wire clk_div;

always #1 clk = ~clk;

always #248 clk_ref = ~clk_ref;

count count1(.clk(clk), .dir(dir), .out(out));

reg clk = 0;

wire [6:0] out1;

count count2(.clk(clk), .dir(0), .out(out1));

delitel delitel1(.clk(clk), .out(clk_div));

endmodule

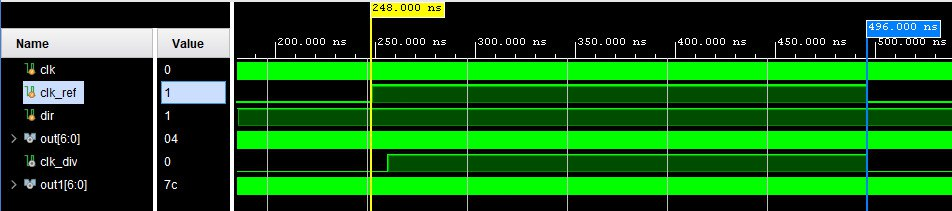

После написания тестового модуля запустим схему и произведем верификацию написанных модулей. Результат верификации представлен на Рисунке 3.1-3.2.

Рисунок 3.1 – Результат верификации делителя частоты

Рисунок 3.2– Результат верификации делителя частоты

ЗАКЛЮЧЕНИЕ

В результате выполнения практической работы были реализованы модули, описывающие параметрический универсальный реверсивный счётчик и делитель частоты на 248, а также проведена верификация данных модулей посредством временной диаграммы.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

Дуксин, Н. А. Архитектура вычислительных машин и систем. Основы построения вычислительной техники: Практикум : учебное пособие / Н. А. Дуксин, Д. В. Люлява, И. Е. Тарасов. — Москва : РТУ МИРЭА, 2023. —185 с.

Смирнов С.С. Информатика [Электронный ресурс]: Методические указания по выполнению практических и лабораторных работ / С.С. Смирнов — М., МИРЭА — Российский технологический университет, 2018. — 1 электрон. опт. диск (CD-ROM).

Соловьев В. В. Основы языка проектирования цифровой аппаратуры Verilog. — М.: Горячая линия — Телеком, 2014. — 208 с.