ЦифрСхТ_ЛР3

.docxМИНОБРНАУКИ РОССИИ Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) Кафедра электронных приборов и устройств |

||||||

ОТЧЁТ по лабораторной работе № 3 по дисциплине «Цифровая схемотехника» Тема: ИССЛЕДОВАНИЕ СХЕМ ТРИГГЕРОВ: ШАБЛОН ОТЧЁТА

|

||||||

|

||||||

Санкт-Петербург 2024 |

ЦЕЛЬ: собрать и исследовать схемы простейших RS-триггеров на ЛЭ 2И-НЕ и 2ИЛИ-НЕ, ознакомиться с принципом действия и временными диаграммами работы триггера-защёлки, универсального RS-D триггера, D-триггера с разрешением и синхронного JK-триггера, реализованных на ПЛИС.

ОБРАБОТКА РЕЗУЛЬТАТОВ

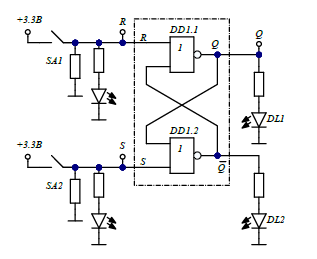

Схема RS-триггера на ЛЭ 2ИЛИ-НЕ приведена ниже.

Рис. 1. Исследованная схема RS-триггера на ЛЭ

Осциллограмма работы исследованной схемы приведена на рис. 2.

Рис. 2. Осциллограмма работы RS-триггера на ЛЭ

Как видно, подача уровня лог. «1» на вход S устанавливает триггер (события №№ 1, 3, 5, 7). Повторная подача того же уровня не приводит к изменению состояния выхода схемы (события №№ 8, 9, 10).

Подача уровня лог. «1» на вход R сбрасывает триггер (события №№ 2, 4, 6), повторная подача того же уровня не приводит к изменению состояния схемы (события №№ 11, 12, 13).

При одновременной подаче на входы триггера активных уровней наблюдаются следующие состояния выходов схемы: 𝑄=0 и 𝑄 ̅= 0 Такое состояние называется «метастабильным». При попытке одновременного снятия двух активных уровней фактически, согласно рис. 2, состояние схемы должно измениться на…

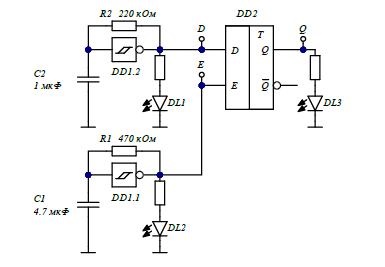

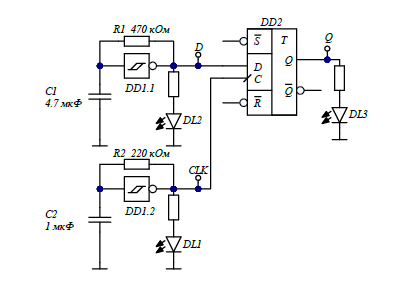

Схема, использованная для исследования триггера-защёлки, приведена ниже.

Рис. 3. Схема для исследования триггера-защёлку

Осциллограмма работы исследованной схемы приведена на рис. 4.

Рис. 4. Осциллограмма работы триггера-защёлки

Как видно, подача уровня лог. «1» на вход Е устанавливает триггер в состояние, которое в этот момент присутствует на входе D (Q=D и 𝑄 ̅= D ̅ соответственно) (события №№ 1, 2, 3).

После подачи на вход Е уровня лог. «0», режим прозрачности выключается и триггер переходит в режим хранения, защёлкивая бит, присутствовавший на входе D непосредственно перед изменением уровня E на лог. «0» (события №№ 4, 5, 6).

Схема, использованная для исследования универсального RS-D триггера, приведена ниже.

Рис. 5. Схема для исследования универсального RS-D триггера

Рис. 6. Осциллограмма работы универсального RS-D триггера

Как видно из данных, записанных в протоколе, подача лог. «0» на вход 𝑆 ̅ в любой момент времени устанавливает триггер в состояние Q = 1, 𝑄 ̅ = 0. Удержание 𝑆 ̅ = 0 обеспечивает Q = 1, 𝑄 ̅ = 0 вне зависимости от уровней и переключений D и С.

Подача лог. «0» на вход 𝑅 ̅ в любой момент времени устанавливает триггер в состояние Q = 0, 𝑄 ̅ = 1. Удержание 𝑅 ̅ = 0 обеспечивает Q = 0, 𝑄 ̅ = 1 вне зависимости от уровней и переключений D и С.

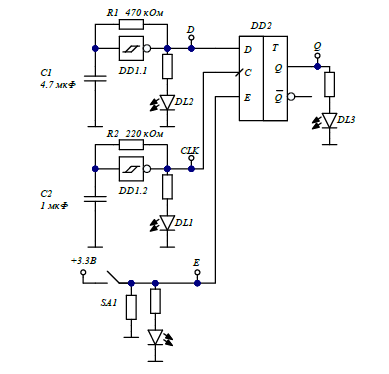

Схема, использованная для исследования универсального D-триггера с разрешением, приведена ниже.

Рис. 7. Схема для исследования D-триггера с разрешением

Рис. 8. Осциллограмма работы универсального RS-D триггера

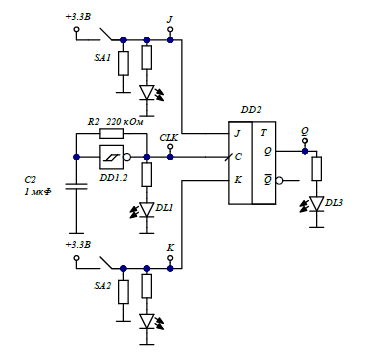

Рис. 9. Схема для исследования синхронного JK-триггера

Рис. 10. Осциллограмма работы синхронного JK-триггера

Изменение состояния триггера происходит по фронту тактового сигнала.

Если J = 1, K = 0 то триггер устанавливается в 𝑄𝑛+1 = 1 (события № 1, 2).

Если J = 0, K = 1, триггер сбрасывается в 𝑄𝑛+1 = 0 (события №№ 3, 4).

Если J = K = 0, триггер не меняет состояния (𝑄𝑛+1 = 𝑄𝑛) (события № 5, 6).

Если J = K = 1, триггер периодично меняет своё состояние на противоположное (𝑄𝑛+1 = 𝑄̅̅̅𝑛̅).

ВЫВОД:

Была проанализирована схема RS-триггера на ЛЭ 2ИЛИ-НЕ (рис. 1) и осциллограмма данной схемы (рис. 2). Когда на вход S триггера подаётся лог. «1», он устанавливает триггер, а когда на входе R действует лог. «1», триггер сбрасывается. При одновременной подаче активных уровней триггер находится в метастабильном состоянии.

Анализируя схему триггера-защёлки (рис. 3) и осциллограмму данной схемы (рис. 4), делаем вывод, что данный̆ триггер представляет собой̆ узел, способный̆ запоминать бит, присутствующий̆ на входе D.

Также, анализируя схему универсального RS-D триггера (рис. 5) и осциллограмму данной схемы (рис. 6), делаем вывод, что низкий̆ уровень в цепи S устанавливает триггер, низкий̆ уровень в цепи R сбрасывает его.

Анализируя схему D-триггера с разрешением (рис. 7) и осциллограммы работы данной схемы (рис. 8), делаем вывод, что при переключении SA2 в лог. «1» и нажатии кнопки D, состояние выхода Q становится равным D в момент поступления на триггер фронта тактового сигнала C (цепь CLK). В случае переключения SA2 в лог. «0», состояние выхода Q не меняется, какой̆ бы уровень в цепи D не присутствовал в момент поступления на триггер фронта тактового сигнала C (цепь CLK).

Также, анализируя схему синхронного JK-триггера (рис. 9) и осциллограммы данной схемы (рис. 10), делаем вывод, что при J=K=0 синхронный JK-триггер хранит последнее записанное в него значение, то есть Q неизменно; при J=1 и K=0 синхронный триггер устанавливается; при J=0 и K=1 триггер сбрасывается; при J=K=1 синхронный триггер переводит Q в состояние, противоположное предыдущему.