2 лр

.docxМинистерство цифрового развития, связи И массовых коммуникаций российской федерации

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования

МОСКОВСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

СВЯЗИ И ИНФОРМАТИКИ

Кафедра «Математическая кибернетика и информационные технологии»

(МКиИТ)

ОТЧЁТ к лабораторной работе №2

до дисциплине «Цифровые устройства и микропроцессоры»

Выполнил:

УБВТ2301

Васильев Артур

Москва, 2024

Задание 1. Счетчик

Вычитающий счетчик на D-триггерах

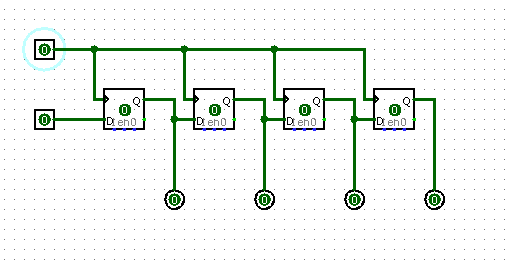

Для создания вычитающего счетчика понадобится 4 двух-шаговых D-триггера, соединенных последовательно. Двух-шаговый D-триггер используется, для синхронизации сигнала. 1 D-триггер соединен выходом Q1 с контактом младшего разряда, выход Q0 является сигналом D для следующего триггера. И так по очереди до максимального разряда. Вход Clock общий.

Задание 2. Регистр памяти на D-триггерах.

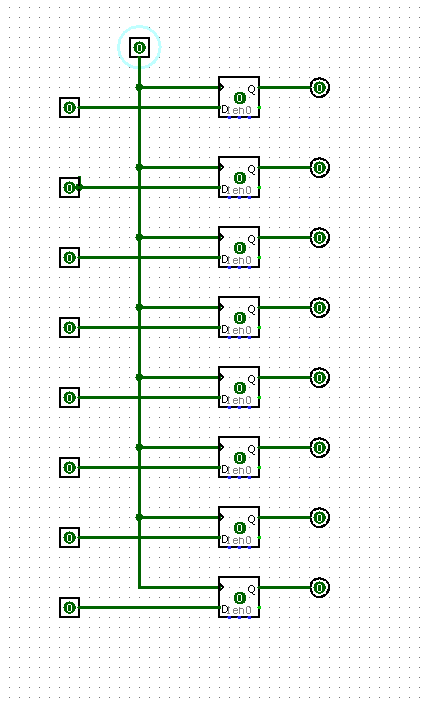

8-битный регистр памяти на D-триггерах, восемь D-триггеров соединенные между собой общим сигналом (Set/Reset), от младшего разряда к старшему (снизу вверх). Принцип работы заключается в том, что при подаче общего сигнала, D-триггеры сохраняют полученную из шины информацию в ячейки. При повторной подаче общего сигнала, информация сбрасывается.

2.1 Сдвиговый регистр на D-триггерах

Сдвиговый регистр на D-триггерах, четыре D-триггера соединенные последовательно, имеют общий сигнал Clock, который является тактом. При подаче на контакт D сигнала, первый D-триггер на выходе Q выдает один, после смены такта он передает этот сигнал на следующий D-триггер.