- •Микропроцессорны е устройства.

- •Принцип обмена с внешними устройствами.

- •Устройства ввода/вывода.

- •Структура системной шины.

- •Самым главным блоком является процессор, затем следует блок ввода-вывода, а память, это всегда

- •В 1990 году компанией Intel была разработана новая модель структуры, разделяющая шину памяти

- •Структура системной шины.

- •Начало каждого цикла отсчитывается по спаду импульса синхронизации. Максимальная частота генерируемых тактовых импульсов

- •Структура системной шины

- •В схему моста к шине памяти включается коммутатор, подключающий пары последовательных линий, сигнальной

- •Передача информации по двум проводам не требует тактового генератора. Любое подключенное устройство начинает

- •UART (Универсальный

- •Основные регистры данных: регистр приема (последовательно- параллельный) и регистр передачи (параллельно-последовательный).

- •Формат управляющего слова.

- •Структура передачи информации.

- •Интерфейс USB (Universal Serial Bus - Универсальный Последовательный Интерфейс)

- •Интерфейс (шина) USB.

- •Структура USB

- •Способ передачи данных по USB.

- •USB пакет состоит из нескольких полей.

- •Интерфейс (шина) SPI

- •Независимое подключение.

- •Каскадное подключение

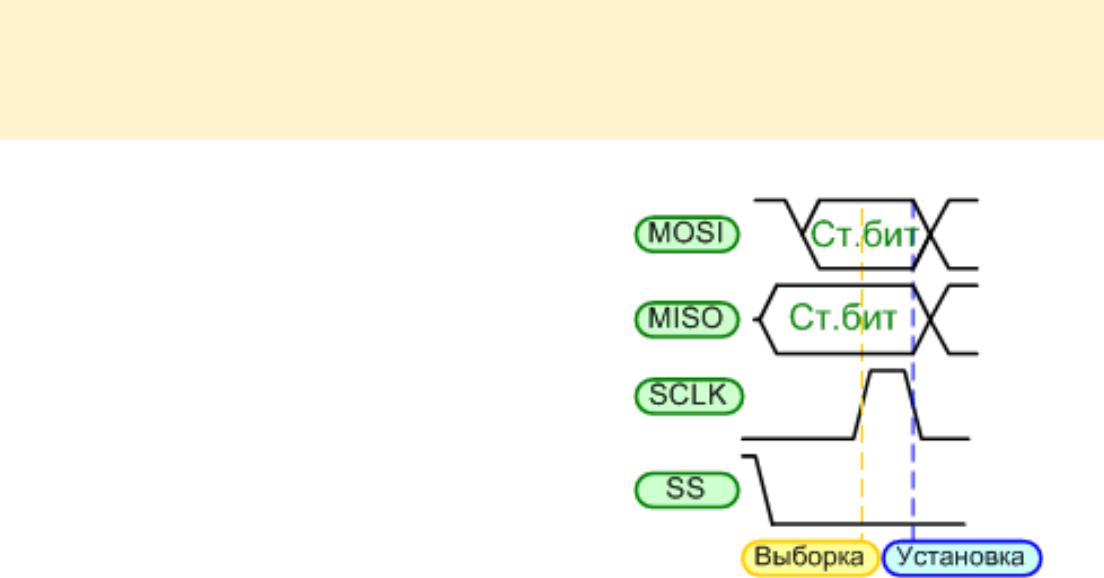

- •Режим 0

- •Режимы 1 и 2

- •Режим 3.

- •Преимущества интерфейса SPI.

- •Недостатки интерфейса SPI.

- •Интерфейс (шина I2C - Inter-integrated circuit bus)

- •Подключение устройств на шину I2C.

- •Ведущее устройство, master, первым выставившее на линию данных «0» при неактивной линии синхронизации

- •Принцип формирования пакета.

- •Формат пакета-признака.

- •Протокол JTAG

- •JTAG. Схема подключения платы к ПК.

- •TAP требует 4-х внешних контактов:

- •Структура ТАР

- •Структура ячейки граничного сканирования для тестирования.

- •Структура ячейки граничного сканирования для программирования.

- •Каждая ячейка граничного сканирования располагается во внешней части кристалла между контактной площадкой и

Интерфейс (шина) SPI

Независимое подключение.

Каскадное подключение

Режим 0

•Исходный уровень синхронизации CPOL=0

•Исходная фаза цикла обмена CPHA =0

Режимы 1 и 2

• CPOL=1; CPHA=0 |

• CPOL=0; CPHA=1 |

Режим 3.

• CPOL=1; CPHA=1

Преимущества интерфейса SPI.

•Полнодуплексная передача данных по умолчанию.

•Возможность произвольного выбора длины пакета.

•Возможность использования в системах с низкостабильной тактовой частотой.

•Адрес ведомого устройства не передается в структуре пакета.

•В отличие от параллельных интерфейсов имеет только 4 вывода.

Недостатки интерфейса SPI.

•Ведомое устройство не может управлять потоком данных.

•Нет подтверждения приема данных со стороны ведомого устройства (ведущее устройство может передавать данные «в никуда»).

•Нет определенного стандартом протокола обнаружения ошибок.

•Наличие множества вариантов реализации интерфейса.

•Отсутствие поддержки горячего подключения устройств.

•Необходимо больше выводов, чем для интерфейса I2C.

Интерфейс (шина I2C - Inter-integrated circuit bus)

•Подключение по 2-проводной схеме.

•Предельная емкость подключенных устройств 400пф.

•Режимы:

•стандартный (S) - 100Кбит/сек

•быстрый (F)– 400Кбит/сек,

•высокоскоростной режим (Hs) – до 3,4Мбит/сек