- •Вычислительная

- •Предпосылки создания ПЛИС.

- •Этапы синтеза КЦУ.

- •Типы ПЛИС.

- •Элементы структуры

- •Кристаллы, в которых каждый выход матрицы ИЛИ связан со всеми термами, называется программируемая

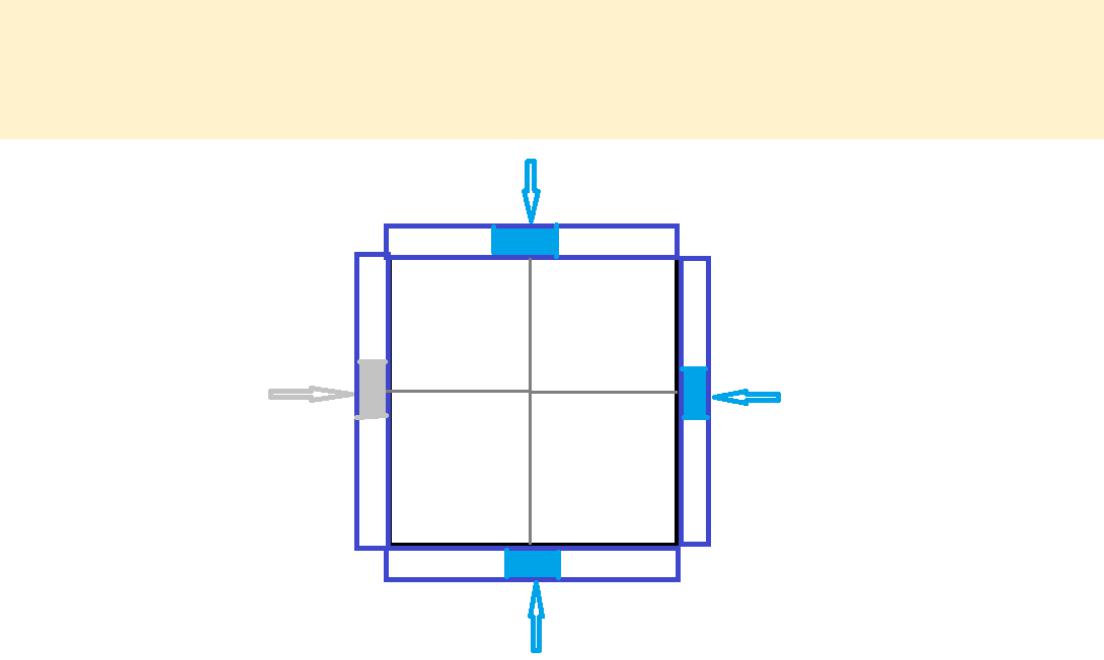

- •Структура FPGA первого поколения.

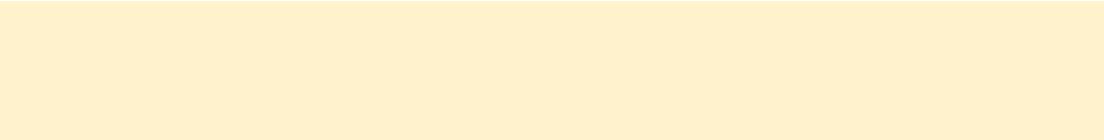

- •Структура элемента для FPGA 1 поколения.

- •Распределенная память.

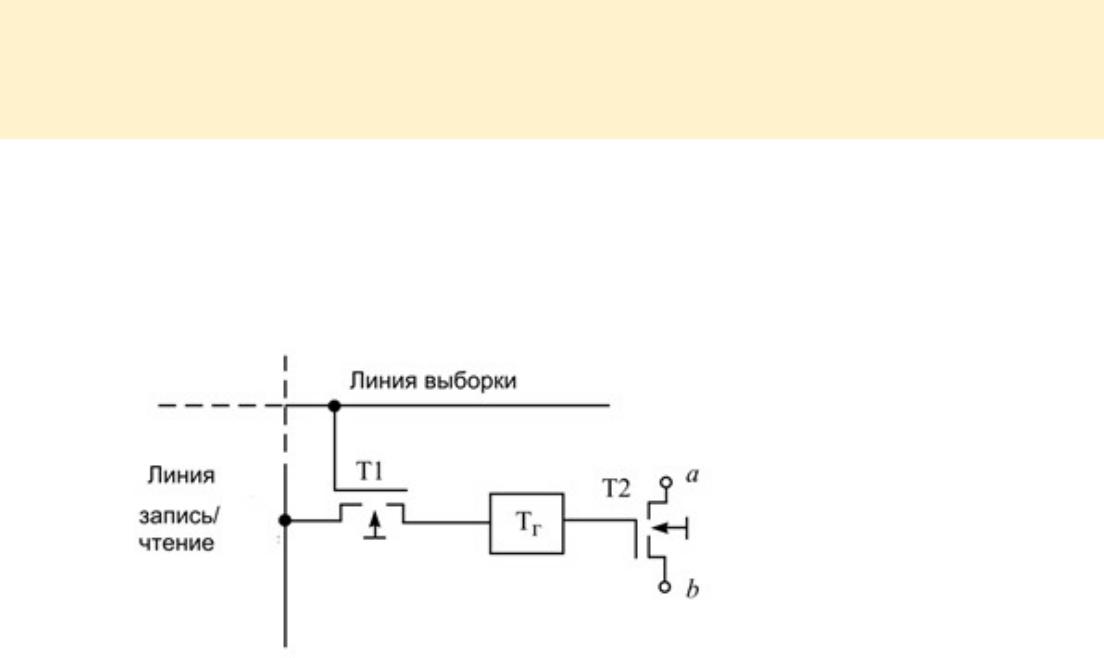

- •Структура FPGA третьего поколения.

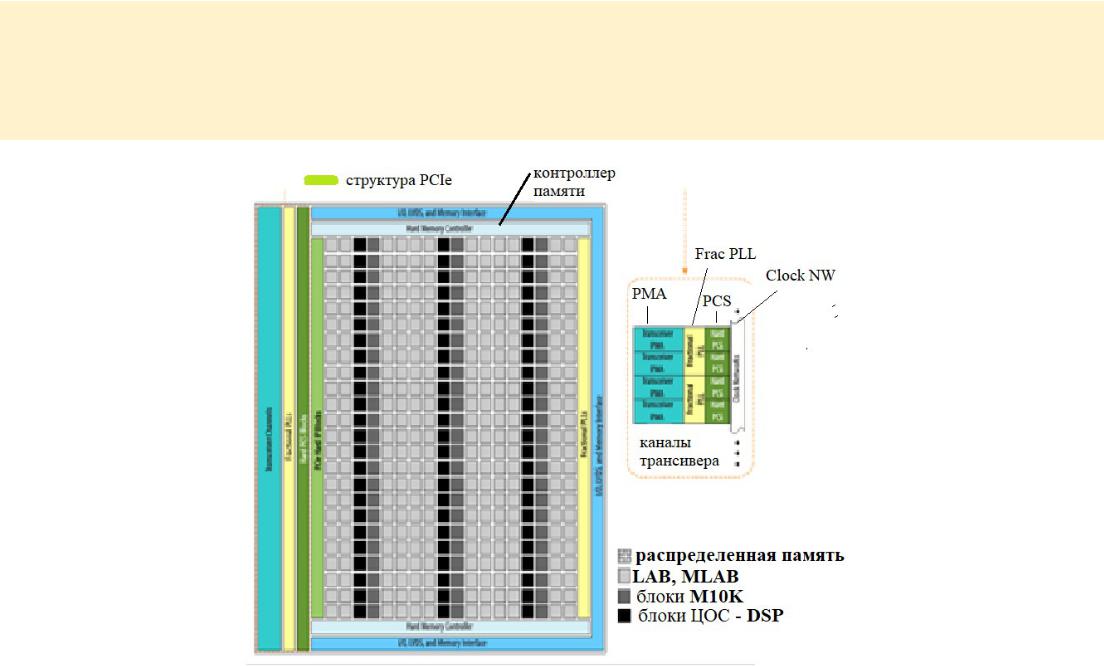

- •Внутренняя структура FPGA 5 поколения.

- •Все функциональные блоки кристалла (LAB, MLAB, M10K, DSP) располагаются во внутренней части в

- •Приемопередатчики, входящие в структуру FPGA, позволяют совершать полнодуплексные передачи данных последовательным способом через

- •5 поколение FPGA. Основная

- •Структура 2-разрядного сумматора в FPGA.

- •Фрагмент структуры блока для реализации счетчика.

- •Внешнее подключение частоты на FPGA.

- •Распределение частоты в FPGA.

- •Глобальная частотная сеть.

- •Глобальные частотные сети пересекают всю поверхность кристалла. Отклонение частоты от номинала невелико. GCLK

- •Региональная частотная сеть.

- •Региональные частотные сети. Применимы только в своей области распространения. Отклонение от номинала невелико.

- •Периферийная частотная сеть.

- •Периферийные частотные сети имеют только горизонтальное направление. Они переносят локальные сигналы частоты, сформированные

Структура элемента для FPGA 1 поколения.

• Элемент FPGA был представлен табличным запоминающим устройством на 4 входа (простая триггерная матрица), LUT. Такой элемент сохраняет отклики на все входные воздействия для функции от 4-х переменных. Отклик мог быть сохранен в триггере. Для использования функции с большим числом переменных в состав элемента входило 3 LUT. Соединения между элементами производились только через точки связей на линиях каналов.

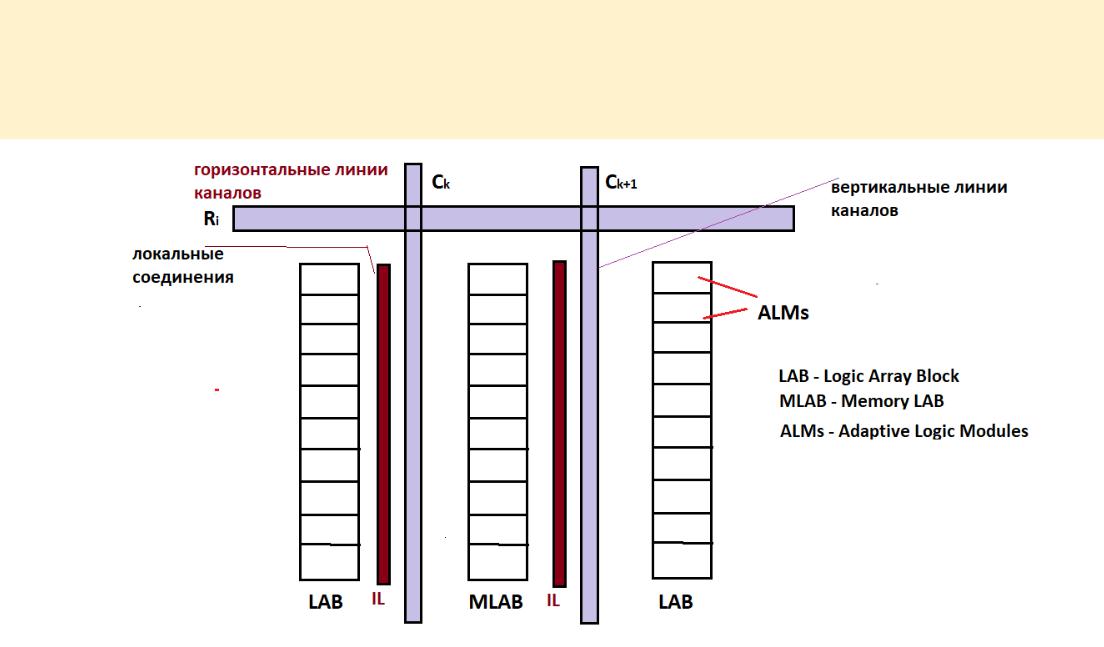

Распределенная память.

•Все блоки, входящие в структуру FPGA, разделены свободными пространствами переходов – каналами. Канальная структура препятствует перегреву кристалла. Для объединения блоков в каналах образованы точки связей – распределенная память.

Структура FPGA третьего поколения.

Внутренняя структура FPGA 5 поколения.

Все функциональные блоки кристалла (LAB, MLAB, M10K, DSP) располагаются во внутренней части в виде матрицы. Управляющие структуры, размещающиеся в слоях кристалла не входят в общую матрицу. Они поддерживают синхронность работы блоков, возможности передачи информации между основными частями вычислительной системы (процессор, память, ввод/вывод), а также преобразование и кодирование передаваемой информации.

Приемопередатчики, входящие в структуру FPGA, позволяют совершать полнодуплексные передачи данных последовательным способом через физическую среду кристалла. Слои PMA (physical medium attachment), позволяют осуществлять последовательно-параллельное преобразование данных в случае приема и параллельно-последовательное для передачи через среду. Подслой PCS (physical coding sublayer) позволяет осуществлять кодирование данных, представленных в параллельном виде для передачи, и восстановление при приеме.

5 поколение FPGA. Основная

структура для построения простых схем.

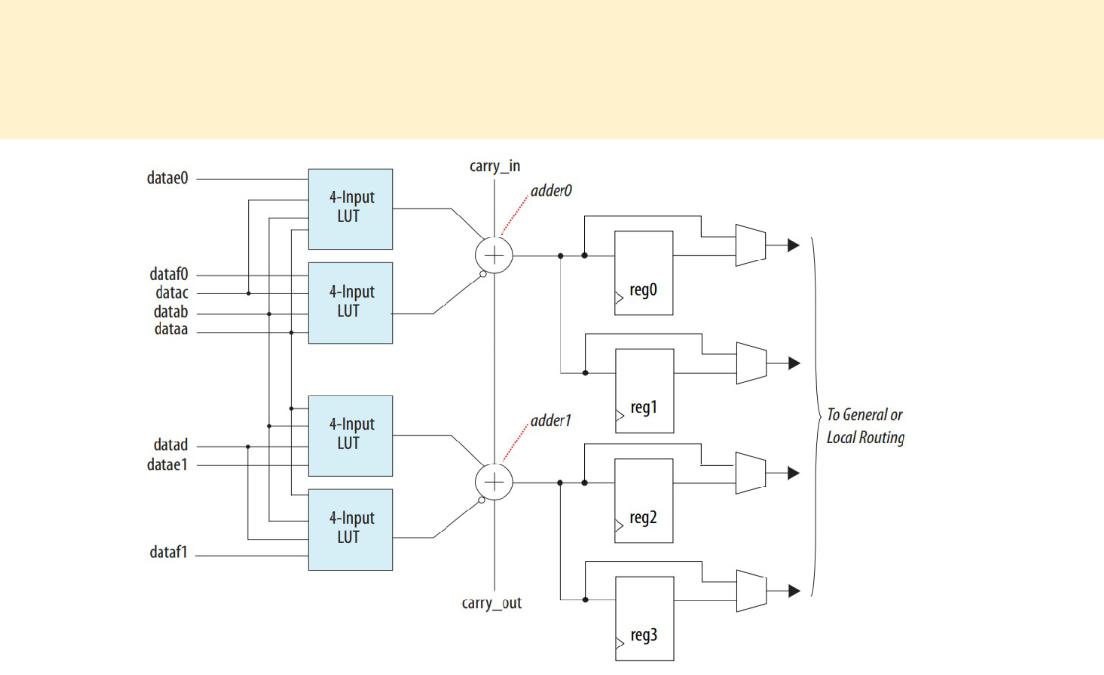

Структура 2-разрядного сумматора в FPGA.

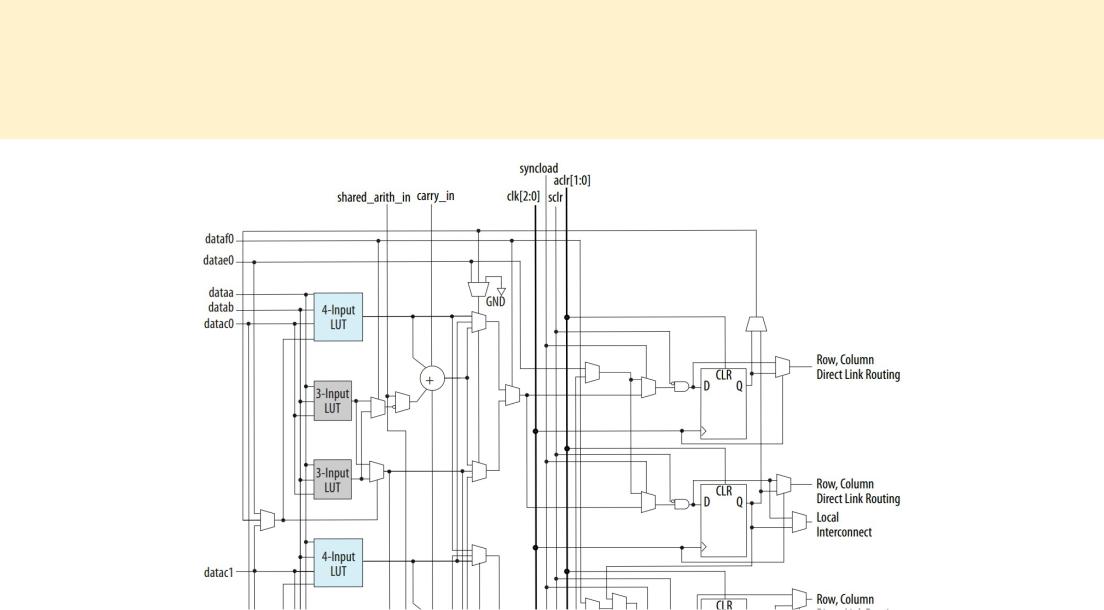

Фрагмент структуры блока для реализации счетчика.