ЛР3

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №3

по дисциплине «Цифровая схемотехника»

Тема: «Исследование схем триггеров»

Студент гр. |

|

|

Преподаватель |

|

|

Санкт-Петербург

2024

Цель - собрать и исследовать схемы простейших RS-триггеров на ЛЭ 2И-НЕ и 2ИЛИ-НЕ, ознакомиться с принципом действия и временными диаграммами работы триггера-защелки, универсального RS-D триггера, D-триггера с разрешением и синхронного JK-триггера, реализованных на ПЛИС.

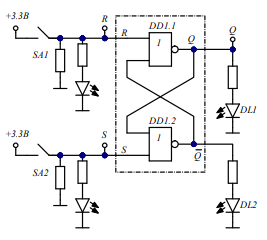

Рис. 1. Исследованная схема RS-триггера на ЛЭ

Рис. 2. Осциллограмма работы RS-триггера на ЛЭ

Если

на вход R

подать уровень лог. «1» (а на входе S

будет оставаться лог. «0»), то вне

зависимости от значения

,

согласно принципу действия ЛЭ ИЛИ-НЕ,

на выходе DD1

установится новый уровень

,

согласно принципу действия ЛЭ ИЛИ-НЕ,

на выходе DD1

установится новый уровень

=

=

,

= 0. Этот логический уровень поступает

на вход DD2,

и на его выходе формируется уровень

,

= 0. Этот логический уровень поступает

на вход DD2,

и на его выходе формируется уровень

.

Это значит, что подача уровня лог. «1»

на вход R

привела к сбросу триггера (к записи в

него нулевого значения). Т. к. лог. «0» не

меняет состояние схемы, а лог. «1»

устанавливает Q

= 0, вход R

называется входом

сброса с

активным высоким уровнем.

.

Это значит, что подача уровня лог. «1»

на вход R

привела к сбросу триггера (к записи в

него нулевого значения). Т. к. лог. «0» не

меняет состояние схемы, а лог. «1»

устанавливает Q

= 0, вход R

называется входом

сброса с

активным высоким уровнем.

Рассуждая

аналогично, подача лог. «1» на вход S

при R

= 0 и при любом

устанавливает

устанавливает

,

т. е. вход S является входом

установки

с активным высоким уровнем.

,

т. е. вход S является входом

установки

с активным высоким уровнем.

При

одновременной подаче на входы триггера

активных уровней наблюдаются следующие

состояния выходов схемы: 𝑄

= 0 и

= 0 Такое состояние называется запрещенным.

При попытке одновременного снятия двух

активных уровней фактически, согласно

рис. 2, оба светодиода не работают. Это

свидетельствует о том, что на выходе

получаем 𝑄

= 0 и

= 0

= 0 Такое состояние называется запрещенным.

При попытке одновременного снятия двух

активных уровней фактически, согласно

рис. 2, оба светодиода не работают. Это

свидетельствует о том, что на выходе

получаем 𝑄

= 0 и

= 0

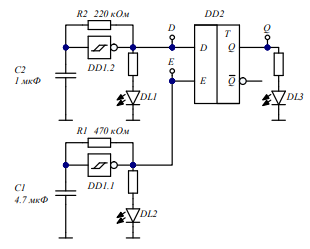

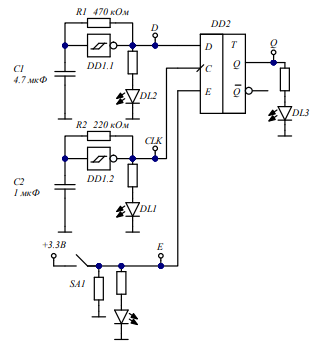

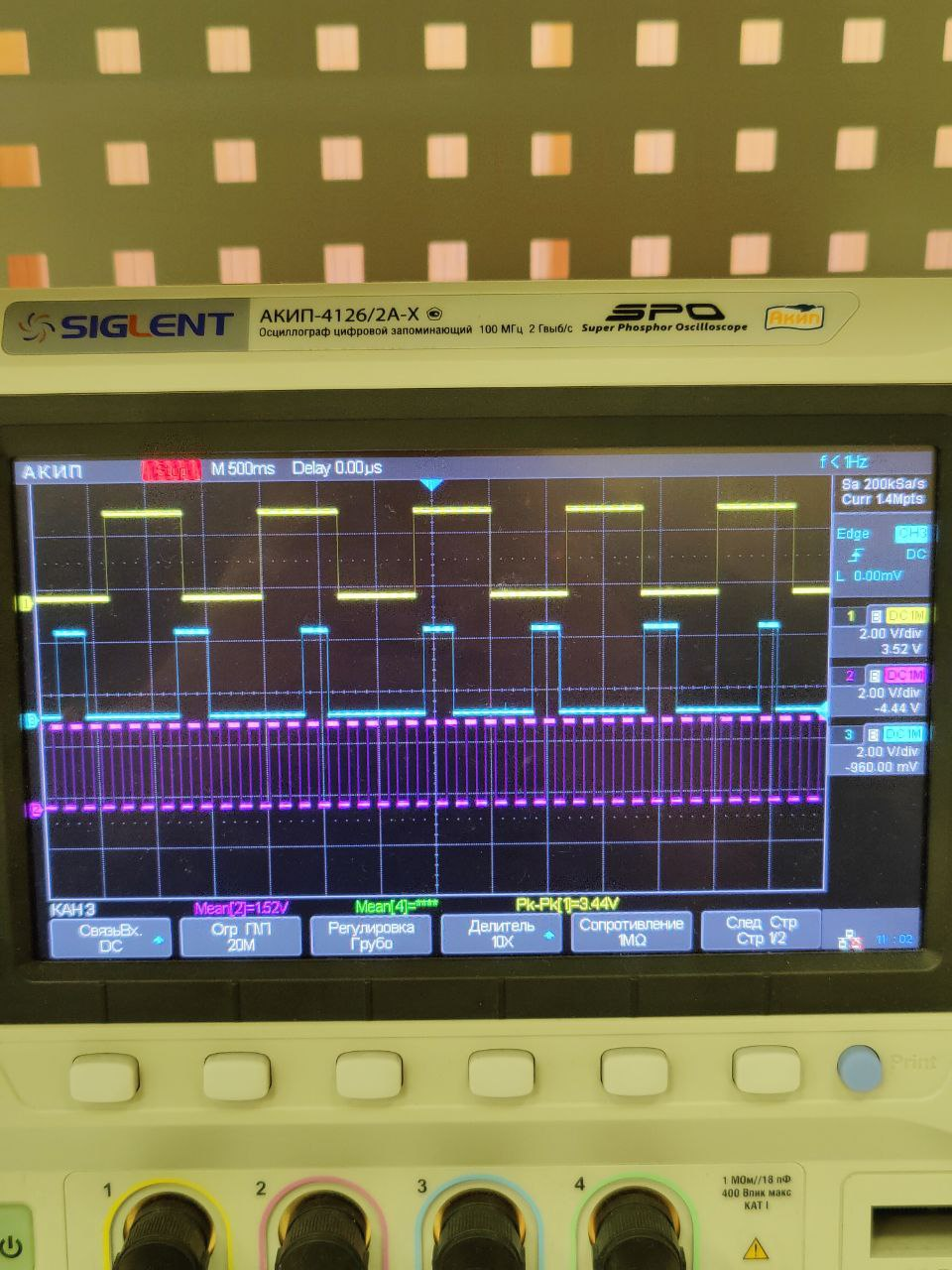

Рис. 3. Схема для исследования триггера-защелки

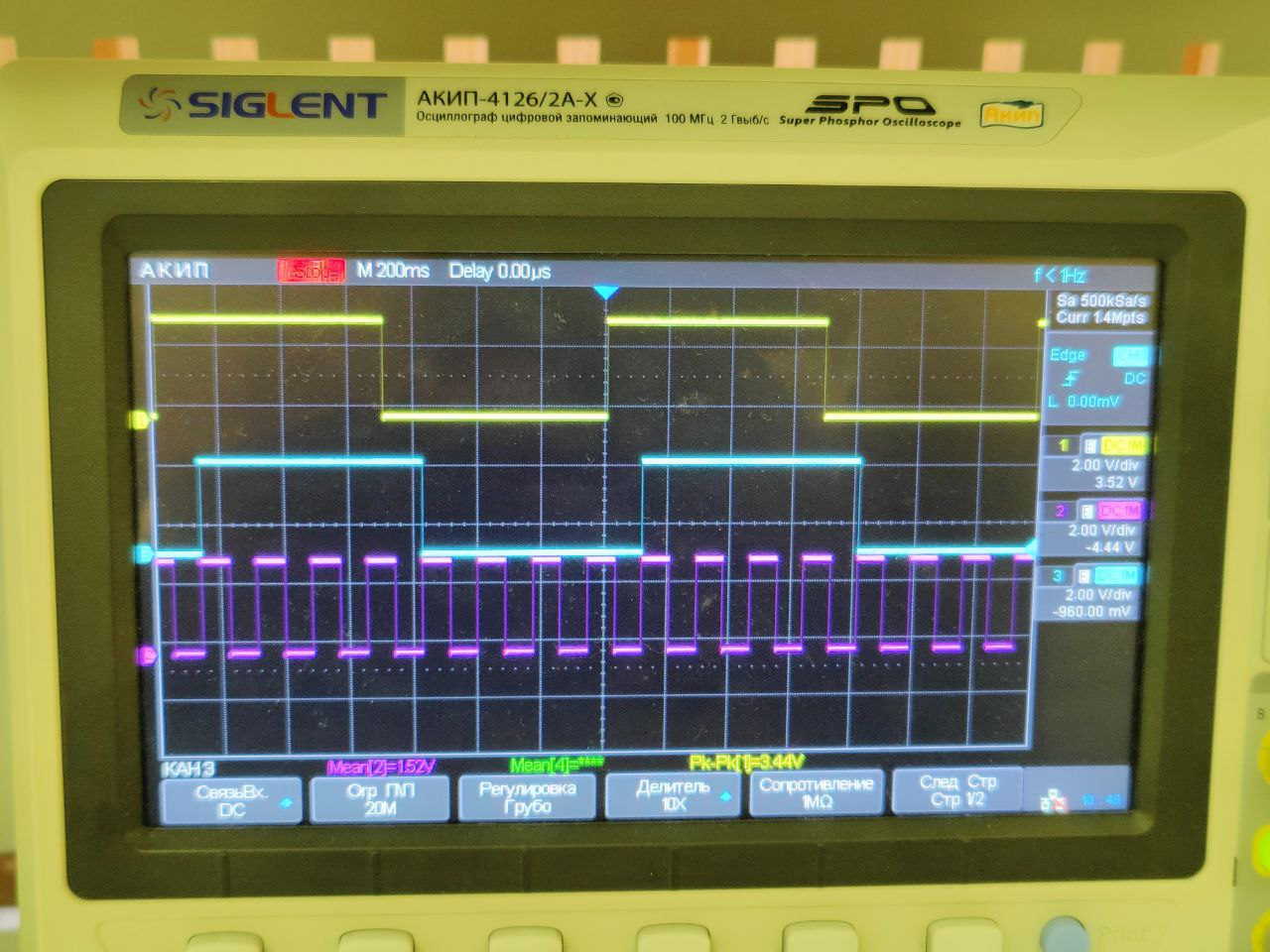

Рис. 4. Осциллограмма работы триггера-защелки

Данный

триггер представляет собой узел,

способный запоминать бит, присутствующий

на входе D.

Работает он следующим образом. Если E

= 1, то Q

= D

(и,

=

,

соответственно). Такой режим называется

режимом

прозрачности:

всякое изменение входного логического

уровня мгновенно (с задержкой, определяемой

только быстродействием компонента)

отражается на выходе триггера-защелки.

,

соответственно). Такой режим называется

режимом

прозрачности:

всякое изменение входного логического

уровня мгновенно (с задержкой, определяемой

только быстродействием компонента)

отражается на выходе триггера-защелки.

После подачи на вход Е уровня лог. «0», режим прозрачности выключается и триггер переходит в режим хранения, защелкивая бит, присутствовавший на входе D непосредственно перед изменением уровня E на лог. «0».

Рис. 5. Схема для исследования универсального RS-D триггера

Рис. 6. Осциллограмма работы универсального RS-D триггера (белые черты показывают наглядность задержки)

Изменение логического уровня на входе D отражается на выходе Q с некоторой задержкой, только в момент поступления импульса на тактовый вход С.

При

подаче на вход

триггера уровня лог. «0» его поведение

меняется следующим образом: триггер

устанавливается в состояние Q

= 0,

= 1. Подача лог. «0» на вход

триггера уровня лог. «0» его поведение

меняется следующим образом: триггер

устанавливается в состояние Q

= 0,

= 1. Подача лог. «0» на вход

приводит к тому, что триггер устанавливается

в состояние Q

= 1,

= 0.

приводит к тому, что триггер устанавливается

в состояние Q

= 1,

= 0.

Рис. 7. Схема для исследования D-триггера с разрешением

Рис. 8. Осциллограмма работы D-триггера с разрешением

Данная схема представляет собой RS-D триггер, аналогичный рассмотренному выше, но имеющий дополнительный вход – вход разрешения работы, который разрешает или запрещает триггеру запоминать бит со входа D по фронту тактового сигнала. Самым простым примером, где подобный триггер незаменим, является задача защиты от дребезга кнопок какой-то цифровой схемы, работающей на высокой тактовой частоте. Но для получения данного функционала требуется двухвходовый мультиплексор – схему, которая передает на свой выход один из двух входных сигналов. Какой из сигналов передается на выход, определяется управляющим сигналом (E).

Если управляющий сигнал 0 – состояние D-триггера изменяться по фронту тактового сигнала не будет. Если же E = 1, то на вход триггера будет приходить сигнал со входа D всей схемы, и на каждом такте сигнала С значение, хранящееся в триггере, будет обновляться.

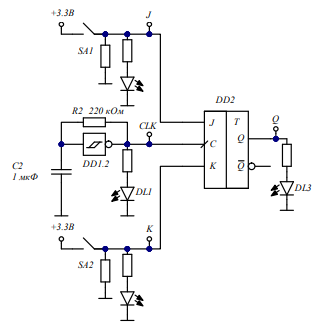

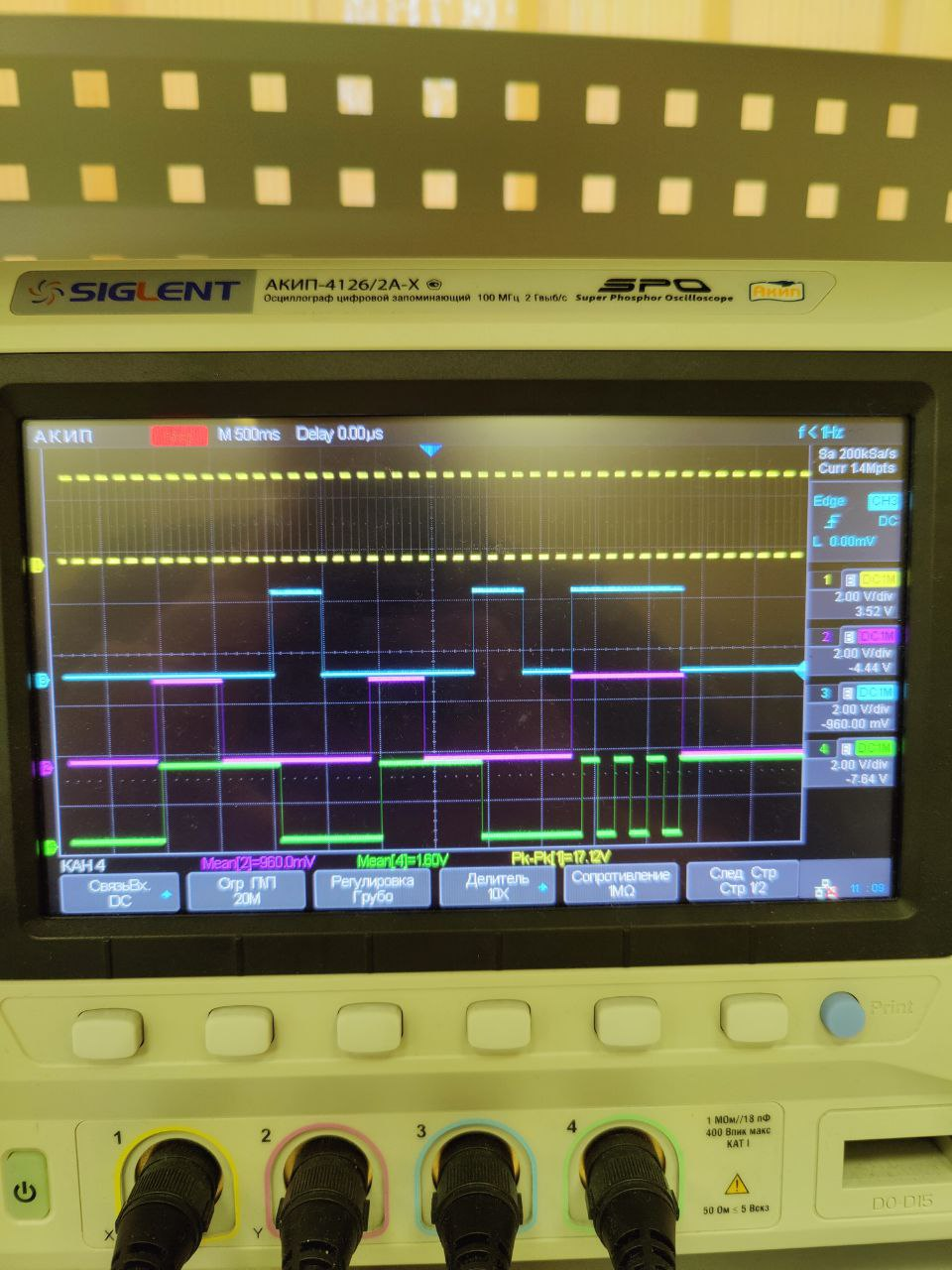

Рис. 9. Схема для исследования синхронного JK-триггера

Рис. 10. Осциллограмма работы синхронного JK-триггера

Синхронный JK-триггер, имеющий тактовый вход и два входа управления – J и K. Изменение состояния триггера происходит по фронту тактового сигнала, при этом:

если J = 1, K = 0 то триггер устанавливается в = 1;

если J = 0, K = 1, триггер сбрасывается в = 0;

если J = K = 0, то триггер не меняет состояния ( = );

если J = K = 1, то триггер меняет свое состояние на противоположное ( = ).

Вывод: В ходе лабораторной работы были изучены различные типы триггеров: RS-триггеры на логических элементах 2И-НЕ и 2ИЛИ-НЕ, триггер-защелка, универсальный RS-D триггер, D-триггер с разрешением и синхронный JK-триггер. Экспериментально исследовался RS-триггер на логических элементах, подтвердив его принцип работы с помощью осциллограммы. Анализ осциллограмм и схем позволил установить функциональность триггера-защелки (как элемента памяти), универсального RS-D триггера (управление установкой и сбросом низкими уровнями на входах S и R соответственно), и D-триггера с разрешением (запоминание бита с входа D при активном сигнале разрешения).