МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

задание к курсовому проекту «Разработка электронного устройства»

по дисциплине «ЦИФРОВАЯ СХЕМОТЕХНИКА»

Тема: Обратный таймер

Вариант 67

Студент гр. |

|

|

Преподаватель |

|

|

Санкт-Петербург

2024

Задание на курсовой проект

Обратный таймер

Разработать цифровой блок:

• Основа блока – десятичный 3-х декадный счетчик на декремент. Одна декада — это четырехразрядное число в диапазоне 0-9.

• Дискретность отсчетов времени – 1 секунда.

• Максимальное значение – 599.

• Минимальное значение – 0.

• Блок имеет 4 дискретных цифровых входа, 2 дискретных цифровых выхода, параллельный вход для отдельных декад и параллельный выход для отдельных декад.

• На параллельный вход подается начальное двоично-десятичное число в соответствии с разрядностью счетчика. Число в виде константы (например, 100) задается самостоятельно.

• Внешнее управление осуществляется импульсами с длительностью не более 100 мс. Импульс – переход из 0 в 1 и затем в 0.

• Фронт импульса на входе 1 загружает в счетчик начальное число.

• При наличии в счетчике начального числа на выходе 1 появляется лог. 0. При любых других значениях счетчика на этом выходе – лог. 1.

• Фронт импульса на входе 2 запускает счет времени счетчиком.

• Фронт импульса на входе 3 останавливает счет времени счетчиком.

• Срез импульса на входе 4 обнуляет счетчик.

• При достижении счетчиком минимального значения счет на уменьшение останавливается и на выходе 2 появляется сигнал с частотой 2 кГц. При любых других значениях счетчика на этом выходе лог. 0.

• Схема должна иметь тактовый вход (частоту выбрать). Сигнал с данного входа напрямую поступает на тактовые входы всех последовательностных узлов блока (триггеров, регистров, счетчиков и т.д.). Все последовательностные узлы блока должны иметь синхронную архитектуру.

• Схема должна иметь вход сброса. В начале работы блока на данном входе кратковременно появляется уровень лог. 0, что должно вызывать загрузку (в т.ч. асинхронную) во все последовательностные узлы блока требуемых начальных значений.

Аннотация

Данная работа представляет собой разработку и моделирование обратного таймера. В работе представлена разработка всех блоков, составляющих данную схему. Во второй части работы приведены результаты моделирования. Были рассмотрены различные сценарии программирования таймера, которые позволяют отразить выполнение технического задания.

ANNOTATION

This work presents the design and simulation of a reverse countdown timer. The design of all constituent blocks of the circuit is detailed. The second part of the work presents the simulation results. Various timer programming scenarios were considered, demonstrating fulfillment of the technical specifications.

Оглавление

АННОТАЦИЯ 3

ВВЕДЕНИЕ 5

1. Разработка схемы 6

1.1 Блок защиты от дребезга кнопки 6

1.2 Блок программируемого делителя частоты 7

1.3 Модуль предустановки 8

1.4 Модуль счётчиков 10

1.5 Общая схема таймера 12

2. Моделирование схемы 13

2.1 Демонстрация работы делителя частоты 13

2.2 Работа таймера 13

2.3 Работа сброса 13

2.4 Излучение сигнала в конце работы таймера 14

ЗАКЛЮЧЕНИЕ 15

СПИСОК ЛИТЕРАТУРЫ 16

Введение

Обратный таймер — сложное многосоставное устройство. Разработку данной схемы стоит разделить на несколько отдельных блоков. Так как в программировании таймера используются кнопки, следует добавить блок защиты от дребезга кнопки. Следующим элементом будет являться делитель частоты, чтобы таймер работал точно в секундах. Так же добавим блок управления, в котором и будет задаваться время, на которое таймер будет считать. Последним элементом будет блок счётчиков, который будет непосредственно осуществлять обратный отсчёт.

1. Разработка схемы

1.1 Блок защиты от дребезга кнопки

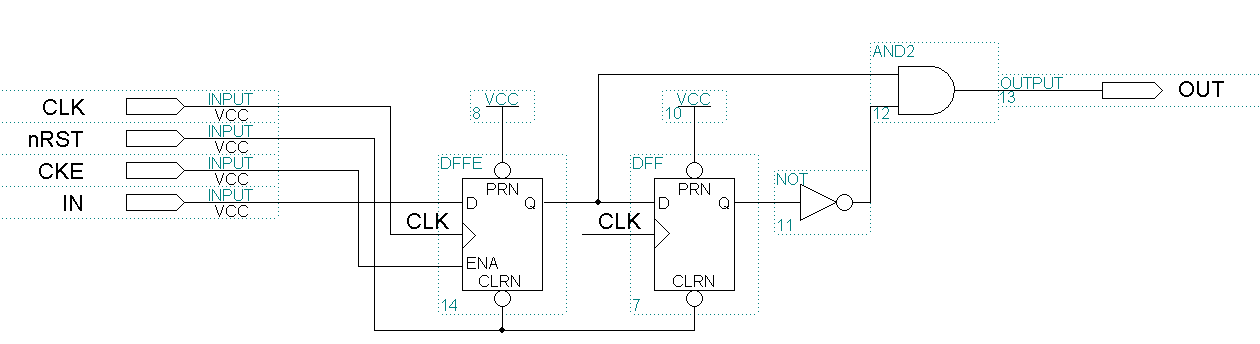

На рис.1 представим схему защиты от дребезга, а на рис.2 символ этого блока. Были использованы два D-триггера. Со входа IN логическая единица (нажатие кнопки) поступает на вход первого D-триггера, затем на вход второго триггера по следующему фронту тактового сигнала. Далее вентиль 2И сравнивает состояния выходов Q1 и NQ2 (к выходу второго триггера подключен инвертор) и выдаёт на выход OUT единицу в случае, когда текущее состояние Q1 равно единице, а предыдущее (Q2) равно нулю.

На вход поступает тактовый сигнал CLK, сигнал сброса nRST, ClockEnable и IN – нажатие кнопки. На выход блок отправляет сигнал OUT.

Рисунок 1. Схема модуля защиты от дребезга кнопки.

Рисунок 2. Символ блока защиты от дребезга кнопки.

В дальнейшем проектировании будем использовать созданный символ key_deb для упрощения вида схемы.

1.2 Блок программируемого делителя частоты

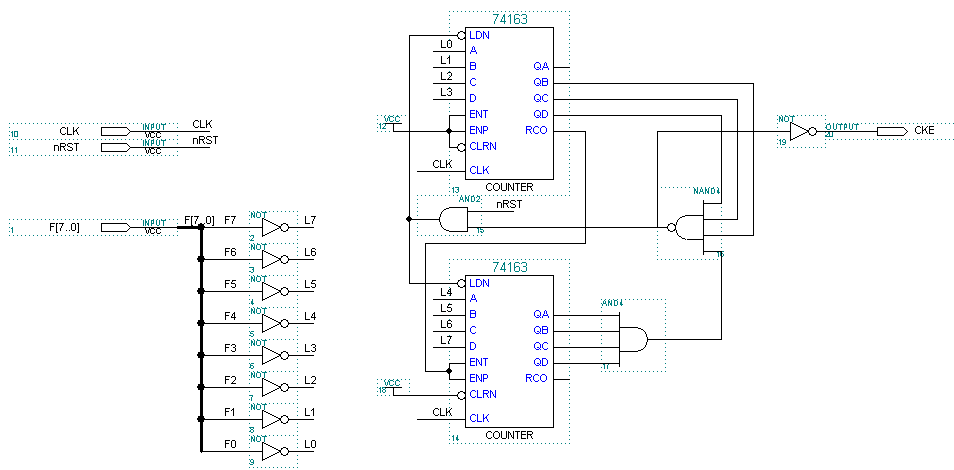

На рис.3 представим схему делителя частоты, а на рис.4 символ этого блока. Блок предназначен для генерации сигнала ClockEnable, чтобы опрос определённых элементов происходил не на каждый такт высокочастотного сигнала, а каждые n- тактов. Число n задаётся вручную, что позволяет программировать этот модуль. На схеме управление происходит через шину F. на неё подаётся число, на которое необходимо поделить частоту CLK.

При построении использовались синхронные счётчики 74163 на инкремент. Счётчики отмеряют временной интервал, через который на выход CKE будет подана лог. 1. Таким образом и происходит деление частоты.

Рисунок 3. Схема делителя частоты.

Рисунок 4. Символ блока делителя частоты.

В дальнейшем проектировании будем использовать созданный символ div_param для упрощения вида схемы.