лабы / лр1

.docx

Федеральное государственное образовательное бюджетное учреждение

высшего профессионального образования

«Санкт-Петербургский государственный университет телекоммуникаций

им. проф. М.А. Бонч-Бруевича»

Отчет по лабораторной работе №3

По дисциплине «Микропроцессорные устройства».

Ассемблер ARM (Cortex A9)

Команды прямой и обратной загрузки.

Выполнил студент

Группы РТ-11

Санкт-Петербург

2023

Цель работы:

-Научиться работать с GVim и Altera Monitor Program.

-Разобраться в процессе обмена данными между ячейками памяти.

Команды прямой и обратной загрузки.

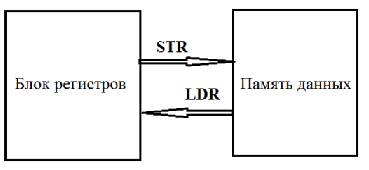

Эти команды позволяют производить обмен данными между ячейками памяти и внутренними регистрами процессора. Используемая память может содержать как массивы данных, так и быть памятью устройств, то есть быть представленной адресами внутренних портов, подключенных к простым внешним интерфейсам. Мнемоника операции прямой загрузки: LDR – Load Register, мнемоника операции обратной загрузки: STR – Store Register. Формат данных может быть: слово, полуслово или байт. Соответствующие мнемоники:

LDRB (Load Register Byte)

LDRSB (Load Register Signed Byte)

LDRH (Load Register Halfword)

LDRSH (Load Register Signed Halfword)

Отличие загрузки знакового операнда от загрузки беззнакового операнда, формат которого меньше, чем слово, в расширении (знаком или нулем).

Соответственно, для обратной загрузки

STRB (Store Register Byte)

STRH (Store Register Halfword)

Ознакомиться с текстом программы – Прогр. 1.

На рабочем столе открыть редактор GVim: Меню приложений – Инструменты – Gvim.

Создать новый файл (Файл – Новый), войти в режим вставки (Insert).

Набрать текст Прогр.1. (номера команд и комментарии не набирать!)

Сохранить файл, создав любую папку проекта в своем каталоге, присвоив ему расширение s. Например: part1_1.s

Подключить макет. Открыть Altera Monitor Program (Файловая система – opt – altera15.0 – University Program – Monitor Program – bin – altera monitor program.)

Выбрать File > New Project.

Далее выбрать имя папки, определить имя проекта в соответствии с тем, как Вы его назвали. Выбрать архитектуру ARM Cortex-A9. Клик Next.

Выбрать DE1-SoC Computer, Next.

Выбираем Assembly Program. Окно вставок не инициализируем! Next.

В следующем окне добавляем созданный файл. Next.

Specify system parameters. Убеждаемся, что подключение макета произведено (надпись в верхнем окне), если надпись отсутствует, просим помощи преподавателя. Обращаем внимание, что в строке Terminal device должно быть выбрано <none>. Next.

Диапазоны используемой памяти оставляем без изменения. Finish.

Осуществить загрузку кодов в макет, дав положительный ответ на запрос “Download System”.

Произвести компиляцию файла и загрузку (Actions> Compile&Load).

Перед началом выполнения программы просмотреть содержимое ячеек памяти, заявленных под адресом ARR, используя опцию Memory (под окном программы). Вернуться на Disassembly.

Выполнять программу пошагово, нажимая на верхнюю иконку с дугообразной желтой стрелкой. Перед выполнением команды считывания с тумблеров в каждом цикле устанавливать новое число на тумблерах макета. На каждом шаге просматривать содержимое основных регистров исполненной команды прямой загрузки (LDR). Для команд обратной загрузки (STR) - адреса и содержимое ячеек памяти. Изменение состояния регистра подсвечивается в отладчике красным цветом (режим disassembly). Перед выполнением каждой команды STR переходить к просмотру памяти (режим memory) Результаты заносить в таблицу 1.

Прогр. 1.

.text

.global _start

1._start: LDR R0, ADR1 // базовый адрес порта тумблеров в R0

2. LDR R1, =ARR // базовый адрес пространства под массив

3. MOV R2, #3 // счетчик элементов массива

4. M1: LDR R3, [R0] // считывание числа с тумблеров в R3

5. STR R3, [R1], #4 // копирование числа в массив

6. SUBS R2, #1 // уменьшение состояния счетчика массива

7. BNE M1 // продолжение считывания, счетчик не «0»

8. LDMDB R1!, {R4-R8} // копирование массива в регистры

9.stop: B stop // останов, бесконечный цикл

ADR1: .word 0xFF200040

ARR: .space 12

.end

Таблица 1.

№ команды |

Содержимое используемого регистра |

Адрес используемой ячейки памяти |

Содержимое ячейки памяти |

Состояние рс |

1 |

r0 =0xff200040 |

0x24 |

0xff200040 |

0x4 |

2 |

R1=0x28 |

0x34 |

0x28 |

0x8 |

3 |

R2=0x3 |

|

|

0xc |

4 |

R3=0x3fd |

0xff200040 |

0x3fd |

0x10 |

5 |

R3=0x3fd R1=0x2c |

0x28 |

0x3fd |

0x14 |

6 |

R2=0x2 |

|

|

0x18 |

7 |

|

|

|

0xc |

4 |

R3=0x39 |

0x ff200040 |

0x39 |

0x10 |

5 |

R3=0x39 R1=0x30 |

0x2c |

0x39 |

0x14 |

6 |

R2=0x1 |

|

|

0x18 |

7 |

|

|

|

0xc |

4 |

R3=0x239 |

0x ff200040 |

0x239 |

0x10 |

5 |

R3=0x239 R1=0x34 |

0x30 |

0x239 |

0x14 |

6 |

R2=0x0 Cpsr=0x0x6…1d3 |

|

|

0x18 |

7 |

|

|

|

0x1c |

8 |

R1=0x28 R4=0x3fd R5=0x039 R6=0x239 |

0x28 0x2c 0x30 |

0x3fd 0x39 0x239 |

0x20 |

Вывод: В ходе работы научился работать с GVim и Altera Monitor Program. Разобрался в процессе обмена данными между ячейками памяти.