lb7

.pdf

11

3.5 Схема RTL Viewer

На рисунках 3.5 представлена схема из RTL Viewer.

sync_sv:syn

C |

|

|

|

|

|

pipo_out[4..0]~reg0 |

|

||||||||||

|

C |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

PRE |

|

|

|

pipo_out[4..0] |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

R |

|

|

|

|

|

Q[4..0] |

|

|

|

|

|

|

D |

Q |

|

|

|

|

|

|

R |

|

|

|

|

|

|

ENA |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

CLR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

cnt_out[4..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 3.5 – Схема из RTL Viewer

3.6 Моделирование устройства, описанного кодом HDL

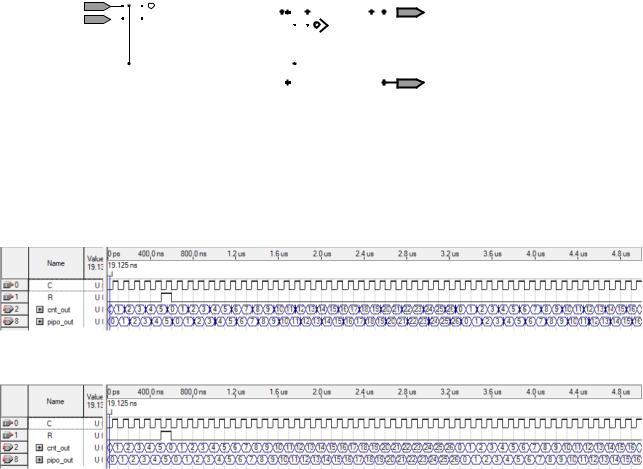

На рисунке 3.6-3.7 представлены результаты моделирования синхронного счетчика, описанного на System Verilog.

Рисунок 3.6 – Результат моделирования кода синхронного счетчика(Timing)

Рисунок 3.7 – Результат моделирования кода синхронного счетчика(Functional)

12

Заключение

В ходе выполнения данной лабораторной работе был изучен процесс применения регистров и счетчиков. Были реализованы следующие схемы: для вычислителя функций, для асинхронного счетчика и для синхронного счетчика с приемом и выдачей согласно варианту(прием убывающим фронтом последовательным кодом младшими разрядами вперед с асинхронным сбросом,

выдача нарастающим фронтом параллельным кодом с активным уровнем сигнала 0). Схемы регистров были промоделированы в двух режимах (timing и functional). С помощью System Verilog были описаны, а также промоделированы те же устройства.