lb7

.pdfМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №7 по дисциплине «Электроника и схемотехника»

Вариант №8

Студент гр. 730-2

Подойницын К.В.

Подойницын К.В.

05.06.2022г.

Руководитель

Доцент КИБЭВС

_____Мальчуков А.Н.

05.06.2022г.

Томск 2022

2

Введение

Целью данной работы научиться совместно применять регистры и счетчики.

1. Cоставить таблицы истинности согласно варианту:

̅̅̅̅̅̅̅̅̅̅̅̅

F6 = X xor Y and ( )

̅̅̅̅̅̅̅̅̅̅̅̅̅

7 = ( ) 8 = 9 = ̅̅̅̅̅̅̅̅̅̅

2.Собрать схемы на холстах .bdf согласно варианту. Организовать прием

ивыдачу данных согласно варианту (прием убывающим фронтом последовательным кодом младшими разрядами вперед с асинхронным сбросом,

выдача нарастающим фронтом параллельным кодом с активным уровнем сигнала 0).

3. Промоделировать работу всех схем в двух режимах (timing и functional). Сравнить результаты моделирования с составленными таблицами истинности.

4. Используя заданный вариантом HDL, описать те же устройства.

Вариант HDL: System Verilog.

5.Написать выводы о проделанной работе

3

1 ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ

1.1 Таблица истинности

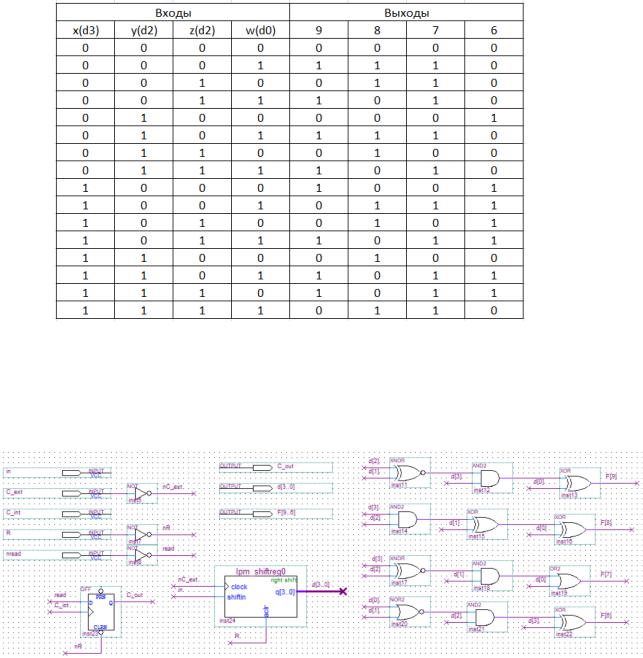

Таблица 1.1 – таблица истинности для вычислителя функций

1.2 Функциональная схема

На рисунке 1.1 представлена функциональная схема вычислителя функций.

Рисунок 1.1 – Функциональная схема вычислителя функций

4

1.3 Моделирование функциональной схемы

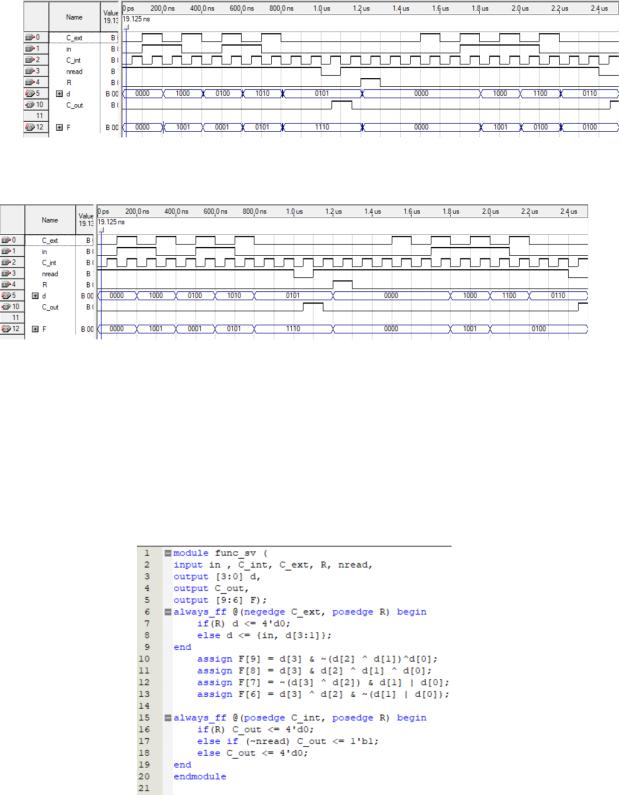

На рисунках 1.2–1.3 представлены результат моделирования вычислителя функций в двух режимах.

Рисунок 1.2 – Результат моделирования вычислителя функций (Timing)

Рисунок 1.3 – Результат моделирования вычислителя функций (Functional)

Результат моделирования совпадает с таблицей.

1.4 Код на HDL

На рисунке 1.4 представлен код описания вычислителя функций на

System Verilog.

Рисунок 1.4 – Код описания вычислителя функций на System Verilog

5

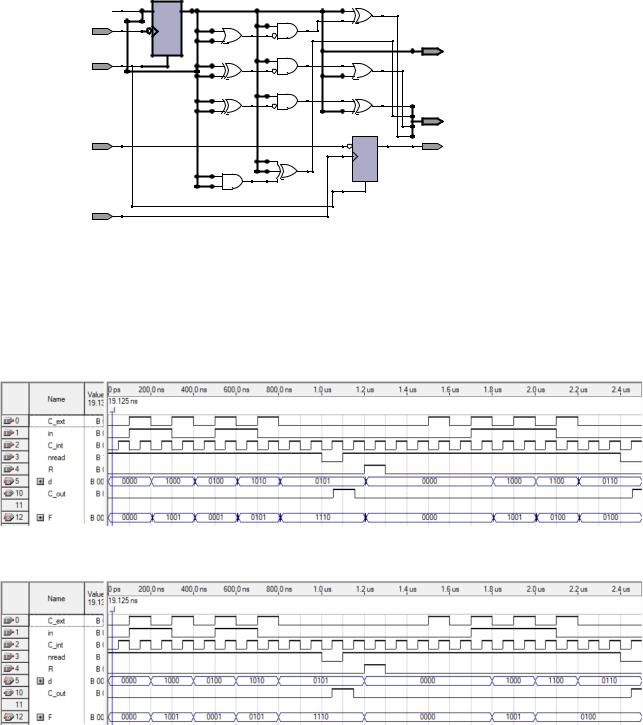

1.5 Схема RTL Viewer

На рисунке 1.5 представлена схема из RTL Viewer.

in

C_ext

R

nread

C_int

d[3..0]~reg0 |

|

|

|

PRE |

|

|

F~11 |

|

|

|

|

D |

Q |

|

|

|

F~9 |

F~10 |

|

|

|

|

|

ENA |

|

|

|

CLR |

|

F~7 |

d[3..0] |

|

F~6 |

|

F~8 |

F~0 |

F~1 |

F~2 |

|

|

|

|

|

||

|

|

|

|

F[9..6] |

|

|

C_out~reg0 |

|

|

|

|

PRE |

|

|

|

|

D |

Q |

C_out |

F~3 |

F~5 |

|

|

|

|

ENA |

|

|

|

|

|

CLR |

|

|

Рисунок 1.5 – Схема из RTL Viewer

1.6 Моделирование устройства, описанного кодом HDL

На рисунках 1.6 – 1.7 представлены результаты моделирования вычислителя функций, описанного на System Verilog.

Рисунок 1.6 – Результат моделирования кода вычислителя функций (Timing)

Рисунок 1.7 – Результат моделирования кода вычислителя функций (Functional)

Результат моделирования совпадает со значениями из таблицы,

представленной в таблице 1.1.

6

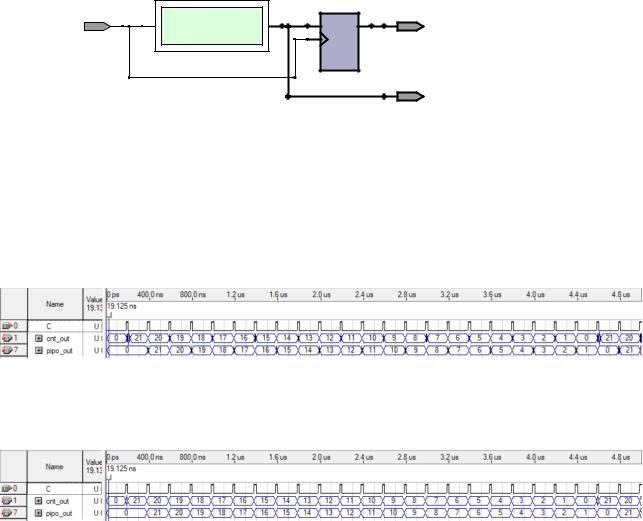

2 АСИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

2.1 Таблица истинности

Таблица 2.1 – таблица истинности асинхронного вычитающего счетчика.

2.2 Функциональная схема для синхронного счётчика.

На рисунке 2.1 представлена функциональная схема асинхронного вычитающего счетчика.

Рисунок 2.1 – Функциональная схема асинхронного вычитающего счетчика

7

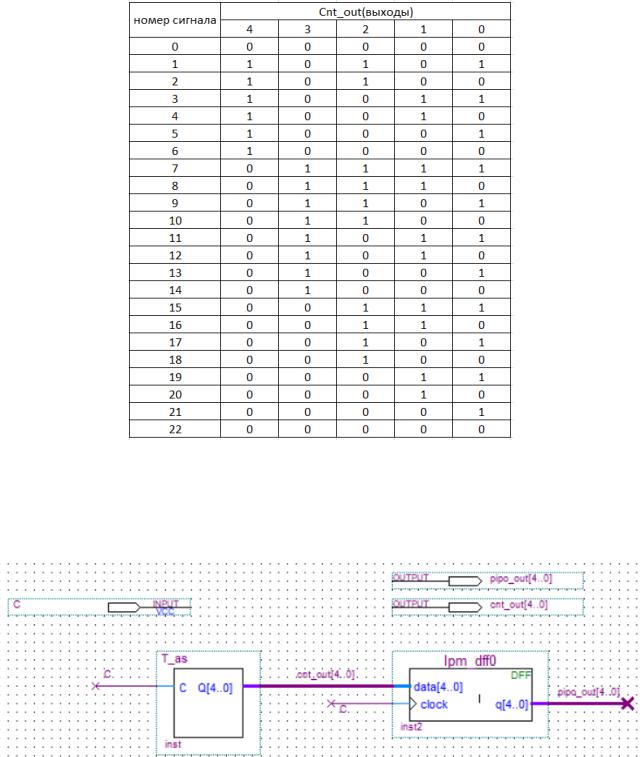

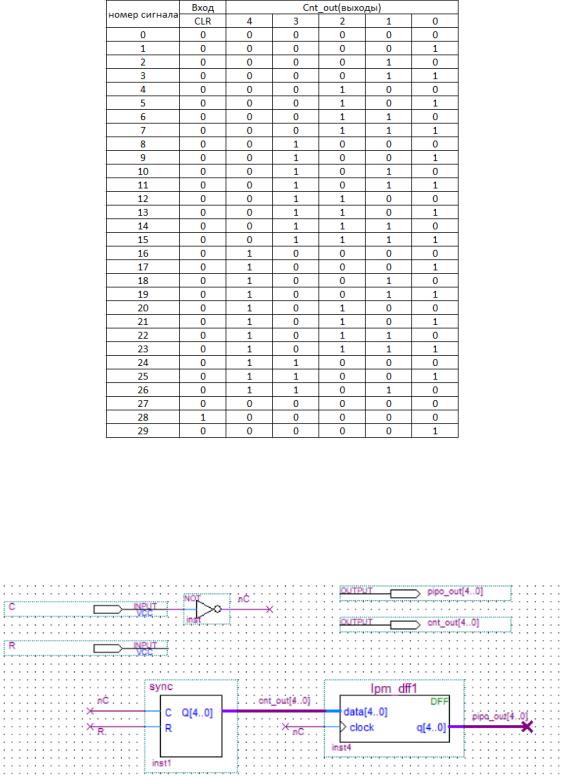

2.3 Моделирование функциональной схемы

На рисунках 2.2–2.3 представлены результат моделирования асинхронного вычитающего счетчика.

Рисунок 2.2 – Результат моделирования асинхронного вычитающего счетчика(Timing)

Рисунок 2.3 – Результат моделирования асинхронного вычитающего счетчика(Functional)

Результат моделирования совпадает с таблицей.

2.4 Код на HDL

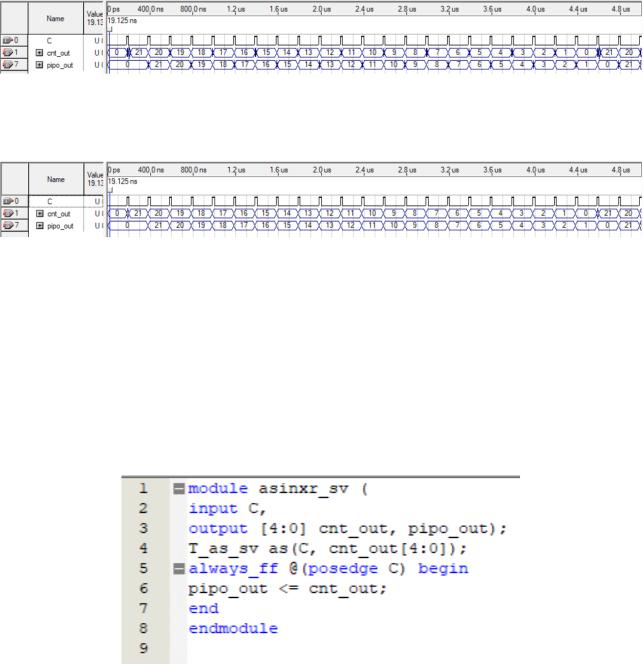

На рисунке 2.4 представлен код описания асинхронного вычитающего счетчика на System Verilog.

Рисунок 2.4 – Код описания асинхронного вычитающего счетчика на

System Verilog

8

2.5 Схема RTL Viewer

На рисунке 2.5 представлена схема из RTL Viewer.

|

|

T_as_sv:as |

|

|

|

|

|

pipo_out[4..0]~reg0 |

|

|

|

|

PRE |

|

C |

C |

Q[4..0] |

D |

Q |

|

|

|

ENA |

|

|

|

|

CLR |

|

pipo_out[4..0]

cnt_out[4..0]

Рисунок 2.5 – Схема из RTL Viewer

2.6 Моделирование устройства, описанного кодом HDL

На рисунке 2.6-2.7 представлены результаты моделирования асинхронного вычитающего счетчика, описанного на System Verilog.

Рисунок 2.6 – Результат моделирования кода асинхронного вычитающего счетчика (Timing)

Рисунок 2.7 – Результат моделирования кода асинхронного вычитающего счетчика (Functional)

Результат моделирования совпадает со значениями из таблицы,

представленной в таблице 2.1.

9

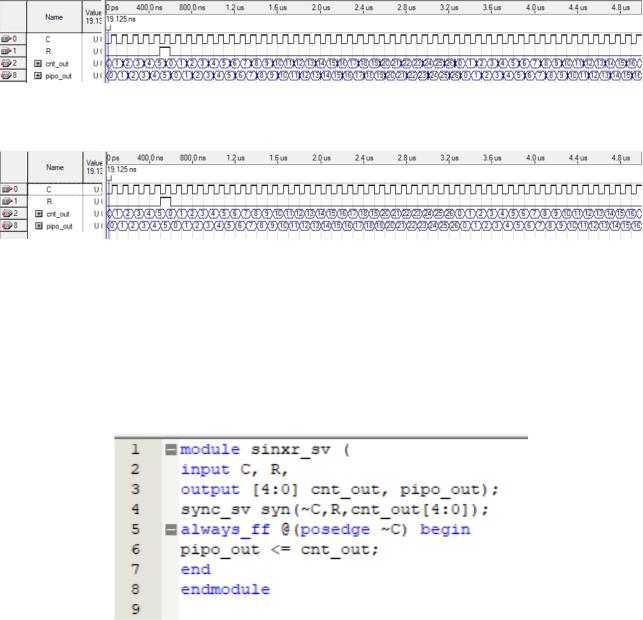

3 СИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

3.1 Таблица истинности

Таблица 3.1 – таблица истинности синхронного счетчика.

3.2 Функциональная схема

На рисунке 3.1 представлена функциональная схема синхронного счетчика.

Рисунок 3.1 – Функциональная схема синхронного счетчика

10

3.3 Моделирование функциональной схемы

На рисунках 3.2–3.3 представлены результаты моделирования синхронного счетчика в двух режимах.

Рисунок 3.2 – Результат моделирования синхронного счетчика(Timing)

Рисунок 3.3 – Результат моделирования синхронного счетчика(Functional)

3.4 Код на HDL

На рисунке 3.4 представлен код описания синхронного счетчика на

System Verilog.

Рисунок 3.4 – Код описания синхронного счетчика на System Verilog