lb2

.pdfМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ШИФРАТОРЫ И ДЕШИФРАТОРЫ

Отчет по лабораторной работе №2 по дисциплине «Электроника и схемотехника»

Вариант №8

Студент гр. 730-2

Подойницын К.В.

Подойницын К.В.

18.05.2022г.

Руководитель

Доцент КИБЭВС

_____Мальчуков А.Н.

18.05.2022г.

Томск 2022

2

Введение

Цель работы – изучить основные инструменты САПР QuartusII и

научиться моделировать в ней работу схем на основе простых логических элементов.

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1.Составить таблицы истинности для схем согласно варианту.

Написать формулы для всех выходов и привести их к требуемому базису:

|

Кол-во вх/вых. |

Базис |

Нарастить до |

|

|

|

|

|

|

CD |

6 |

вх. |

И, ИЛИ, НЕ |

- |

|

|

|

|

|

DC |

10 |

вых. |

И-НЕ |

- |

|

|

|

|

|

HPRI |

8 |

вх. |

ИЛИ-НЕ |

16 вх. |

|

|

|

|

|

2.Собрать схемы на холстах .bdf согласно полученным формулам;

3.Создать схему устройства согласно варианту большей размерности на основе созданного ранее символа.

4.Промоделировать работу всех схем в двух режимах. Сравнить результаты моделирования с составленными таблицами истинностями

5.Используя заданный вариантом HDL(VHDL) описать те же устройства.

3

1. ШИФРАТОР 6-3

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности шифратора 6-3

Таблица 1.1 – Таблица истинности CD 6-3

1.2 Формулы

Ниже представлены формулы схемы для шифратора 6-3 на базисе И,

ИЛИ, НЕ:

5 |

̅̅̅ |

∩ 4 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

= 5 |

∩ 3 |

∩ 2 |

∩ 1 |

∩ 0 |

||

4 = 5 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

|

∩ 4 |

∩ 3 |

∩ 2 |

∩ 1 |

∩ 0 |

||

3 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

∩ 2 |

̅̅̅ |

̅̅̅ |

= 5 |

∩ 4 |

∩ 3 |

∩ 1 |

∩ 0 |

||

|

̅̅̅ |

̅̅̅ |

∩ 3 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

2 = 5 |

∩ 4 |

∩ 2 |

∩ 1 |

∩ 0 |

||

1 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

∩ 1 |

̅̅̅ |

= 5 |

∩ 4 |

∩ 3 |

∩ 2 |

∩ 0 |

||

0 |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

∩ 0 |

= 5 |

∩ 4 |

∩ 3 |

∩ 2 |

∩ 1 |

||

2 = ∩ ( 5 4 )1 = ∩ ( 3 2)

0 = ∩ ( 1 2 4 )

= ∩ ( 5 4 3 2 1 0)

4

1.3 Функциональная схема

На рисунке 1.1 представлена функциональная схема шифратора 6-3.

Рисунок 1.1 – Функциональная схема CD 6-3

1.4 Моделирование функциональной схемы

На рисунках 1.2–1.3 представлены результат моделирования шифратора 6-3 в двух режимах.

Рисунок 1.2 – Результат моделирования CD 6-3 (Timing)

5

Рисунок 1.3 – Результат моделирования CD 6-3 (Functional)

Результат моделирования совпадает с таблицей истинности.

1.5 Код на VHDL

На рисунке 1.4 представлен код описания CD 6-3 на VHDL

Рисунок 1.4 – Код описания CD 6-3 на VHDL

6

1.6 Схема RTL Viewer

На рисунке 1.5 представлена схема из RTL Viewer.

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Mux2 |

|

|

|

|

a~[2..0] |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

SEL |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

x[5..0] |

|

|

|

|

|

SEL[5..0] |

|

|

3' h0 -- |

|

|

|

DATAA |

|

|

|||||||||

|

64' h0000000100000104 -- |

|

|

OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a[2..0] |

|||

|

|

|

DATA[63..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT0 |

|

|||||

|

|

|

|

|

|

|

MUX |

|

|

|

|

|

|

|

|

|

|

DATAB |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Mux1 |

|

|

|

|

|

|

|

|

|

MUX21 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

SEL[5..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

64' h0000000000000110 -- |

|

|

DATA[63..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

MUX |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

Mux0 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

SEL[5..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

64' h0000000100010000 -- |

|

|

DATA[63..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

MUX |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

Mux3 |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEL[5..0] |

0 |

|

0 |

|

|

|

|

|

G |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

64' h0000000100010116 -- |

|

|

OUT |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|||

|

|

|

DATA[63..0] |

|

|

|

|

|

|

|

|

G |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

MUX |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

Рисунок 1.5 – Схема из RTL Viewer

7

1.7 Моделирование устройства, описанного кодом VHDL

На рисунках 1.6 – 1.7 представлены результаты моделирования CD 6-3,

описанного на VHDL.

Рисунок 1.6 – Результат моделирования кода CD 6-3 (Timing)

Рисунок 1.7 – Результат моделирования кода CD 6-3 (Functional)

Результат моделирования совпадает со значениями из таблицы истинности, представленной в таблице 1.1.

8

2. ДЕШИФРАТОР 4-10

2.1Таблица истинности

Втаблице 2.1 представлена таблица истинности дешифратора 4-10

Таблица 2.1 – Таблица истинности DC 4-10

2.2 Формулы

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅

x9 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅ ̅̅̅

x8 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅

x7 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅

x6 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅

5 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅ ̅̅̅

4 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅

3 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅ ̅̅̅

2 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅ ̅̅̅

1 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̅̅̅ ̅̅̅ ̅̅̅ ̅̅̅

0 = ∩ 3 ∩ 2 ∩ 1 ∩ 0

9

2.3 Функциональная схема

На рисунке 2.1 представлена функциональная схема дешифратора 4-10

Рисунок 2.1 – Функциональная схема DC 4-10

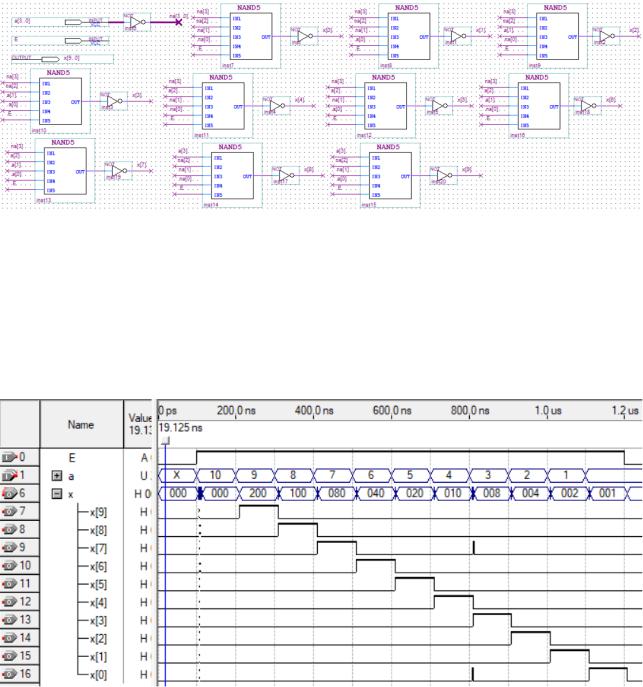

2.4 Моделирование функциональной схемы

На рисунках 2.2–2.3 представлены результат моделирования дешифратора 4-10 в двух режимах.

Рисунок 2.2 – Результат моделирования DC 4-10 (Timing)

10

Рисунок 2.3 – Результат моделирования DC 4-10 (Functional)

Результат моделирования совпадает с таблицей истинности.

2.5 Код на VHDL

На рисунке 2.4 представлен код описания DC 4-10 на VHDL.

Рисунок 2.4 – Код описания DC 4-10 на VHDL