МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра электронных приборов и устройств

КУРСОВАЯ РАБОТА

по дисциплине «Цифровая схемотехника»

Тема: «Разработка электронного устройства»

Студент гр. |

|

|

Преподаватель |

|

Ухов А.А. |

Санкт-Петербург

2024

АННОТАЦИЯ

В данной курсовой работе изложены ключевые этапы разработки и моделирования электронного десятичного счетчика с реверсивным режимом. В первом разделе приведен анализ необходимых характеристик цифрового блока и методы их реализации, представлены схемы составных частей схемы, и полная схема разработанного устройства, с описанием ее функционирования. Во втором разделе проведено моделирование работы схемы устройства и краткий анализ полученных результатов.

ANNOTATION

This term paper describes the key stages of development and modeling of an electronic decimal counter with a reversible mode. The first section provides an analysis of the necessary characteristics of the digital block and methods for their implementation, presents circuit diagrams of the circuit components, and a complete circuit diagram of the developed device, with a description of its operation. The second section simulates the operation of the device circuit and briefly analyzes the results obtained.

СОДЕРЖАНИ

АННОТАЦИЯ 3

ВВЕДЕНИЕ 5

1. РАЗРАБОТКА СХЕМЫ 6

1.1 Формирователь импульсов управления 6

1.2 Выбор 4-разрядного реверсивного счетчика 7

1.3 Основа блока (3-декадный реверсивный счетчик) 8

2. ВРЕМЕННЫЕ ДИАГРАММЫ 11

ЗАКЛЮЧЕНИЕ 13

СПИСОК ИНФОРМАЦИОННЫХ ИСТОЧНИКОВ 14

ВВЕДЕНИЕ 5

1. РАЗРАБОТКА СХЕМЫ 6

1.1 Формирователь импульсов управления 6

1.2 Выбор 4-разрядного реверсивного счетчика 7

1.3 Основа блока (3-декадный реверсивный счетчик) 8

2. ВРЕМЕННЫЕ ДИАГРАММЫ 10

ЗАКЛЮЧЕНИЕ 11

СПИСОК ИСТОЧНИКОВ ИНФОРМАЦИИ 11

ВВЕДЕНИЕ

Главной задачей является разработка цифрового блока на основе 3-х декадного реверсивного счетчика. Для реализации которого целесообразно использовать каскад 4-разрядных двоично-десятичных счетчиков. Необходимо предусмотреть дополнительную логическую электронную обвязку этих счетчиков, для возможности формирования необходимых сигналов управления, блокировки счета на заданных значениях, ограничения коэффициента пересчета. Схема должна иметь синхронную архитектуру, и иметь возможность полного сброса при каждом начале работы. Благодаря чему такое устройство можно использовать в системах подсчета людей, транспорта и т.д. Электрические принципиальные схемы и результаты моделирования оформлены в среде MAX+ Plus II.

РАЗРАБОТКА СХЕМЫ

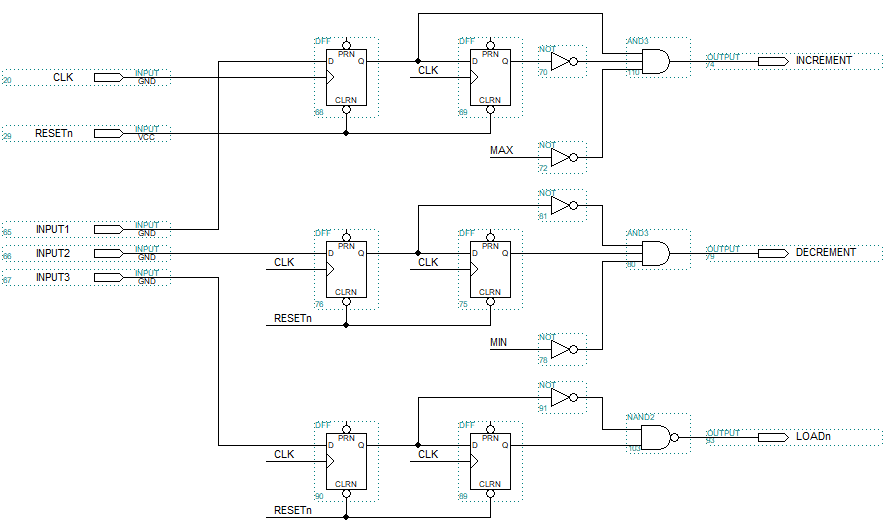

1.1 Формирователь импульсов управления

Синхронная работа схемы обеспечивается, тактовым сигналом CLK, частота которого должна быть такой, чтобы на каждый импульс управления длительностью не менее 10 мс был хотя бы 1 тактовый импульс. То есть минимальное значение частоты CLK для нормальной работы схемы – 100 Гц. Для надёжного и точного подсчёта желательно, чтобы тактовая частота была значительно выше. Поэтому, частота CLK выбирается 1 кГц, что даст 10 тактовых отсчетов на каждый импульс.

Также задается вход асинхронного сброса RESETn, с «0» активным уровнем, который является общим для всех последовательностных узлов схемы.

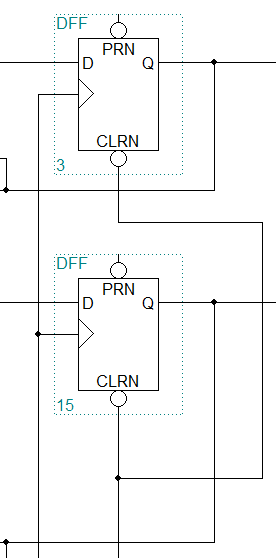

С помощью D-триггеров создаются детекторы фронта для входа INPUT1, и среза для входов INPUT2 и INPUT3.

Рисунок 1 – Блок формирования синхронных импульсов управления

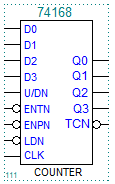

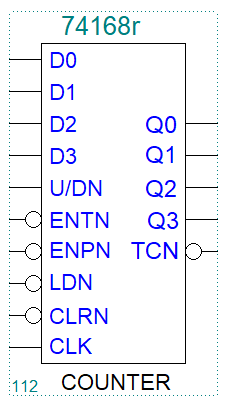

1.2 Выбор 4-разрядного реверсивного счетчика

Для создания блока подсчета импульсов была выбрана микросхема 74168, это синхронный двоично-десятичный 4-разрядный реверсивный счетчик. Данная модель имеет все необходимые входы и выходы для построения нужного устройства, но в этой модели нет асинхронного входа сброса. Поэтому внутренняя структура была доработана, соединением асинхронных входов D-триггеров, входящих в состав счетчика, к одному входу асинхронного сброса CLRN. Данный вариант подходит для реализации устройства на ПЛИС.

Рисунок 2 – Выбранный счетчик 74168 и измененный 74168r с добавленным входом асинхронного сброса

Полученный счетчик имеет 4 информационных параллельных входа и выхода D[3..0] и Q[3..0]. Вход режима счета U/DN, при лог. «1» на этом входе счетчик считает в режиме суммирования. Вход разрешения счета ENPN и вход разрешения поступления тактовых импульсов. Вход загрузки LDN, при подаче «0» на который, счетчик устанавливает состояние входов D[3..0], выход переноса счета TCN и тактовый вход CLK. Асинхронный вход сброса CLRN был добавлен вручную.

1.3 Основа блока (3-декадный реверсивный счетчик)

На счетчиках описанных ранее строится основной блок (рис. 3). Счетчики подключаются в каскад, с помощью входов разрешения и выходов переноса. Сигналы с цепей RESETn и LOADn подключатся напрямую ко входам счетчика. Сигналы с цепей управления и задания счета подключатся через элемент NOR2, обеспечивая такую логику работы, при которой счет вверх разрешен, когда работает вход INCREMENT. На каждый импульс счета, счетчику разрешается 1 счет по такту.

Для задания ограничения макс. значения и сигнала при переполнении счетчика используется лог. обвязка из элементов AND2, AND3 и NOR4. Тем самым при достижении максимума 996 формируется лог. «1» на выходе MAX, а при минимуме в 000, лог. «1» на выходе MIN. Активный уровень на этих выходах используется в цепи ФИУ для блокировки счета при переполнении.

Для задания значения 990 на предустановке, параллельные входы подключаются согласно двоичным значениям цифр в числе.

Параллельные входы с каждого счетчика объединяются в шина c1x[3..0], c10x[3..0] и c100x[3..0], которые можно подключить в дальнейшем к 7-сегментным индикаторам.

Рисунок 3 – Основной блок счета (3-х декадный реверсивный счетчик)

ВРЕМЕННЫЕ ДИАГРАММЫ

Полученные при симуляции работы схемы временные диаграммы, позволяют полностью проанализировать работу полученного счетчика. Тактовая частота CLK равна 1 кГц, на входе RESETn появляется кратковременный «0» импульс, позволяющий сбросить все узлы в начале работы. Как видно в это время «1» на выходе MIN сообщает о том, что счетчик находится в минимуме и счет вниз запрещен – схема не реагирует на импульсы со входа INPUT2 (DECREMENT). При подаче импульсов на повышение счета INPUT1 счетчик начинает счет по фронту этих импульсов и «1» с выхода MIN уходит. Срез активного уровня на входе INPUT3 загружает в счетчик значение 990, дальнейший счет приводит к переполнению счетчика на значении 996, блокируется счет на повышение, на выходе MAX появляется «1». При подаче импульсов на понижение счетчик снова начинает счет.

11

Рисунок

4 – Тактовые диаграммы работы

разработанного устройства

-

11

Рисунок 4 – Тактовые диаграммы работы разработанного устройства

ЗАКЛЮЧЕНИЕ

В результате выполнения данной курсовой работы был разработан 3-х декадный реверсивный блок счета. Позволяющий считать импульсы в прямом и обратном направлении, имеющий синхронную архитектуру и возможность загрузки заданных значений. Блок защищен от граничных случаев переполнения счета в обоих направлениях. Предусмотрен вход предварительного сброса в начале работы. Вариант разработанной схемы хорошо подходит для реализации на ПЛИС, для создания устройства на базе микросхем необходимо выбрать другие счетчики или предусмотреть другие способы сброса основного блока счета.

Разработанное устройство полностью соответствует начальным требованиям и может быть использовано в электронных цифровых системах.

СПИСОК ИНФОРМАЦИОННЫХ ИСТОЧНИКОВ

Цифровая схемотехника, методические указания по проведению лабораторных занятий, внутренняя рабочая версия каф. ЭПУ СПбГЭТУ «ЛЭТИ» – 2024

Цифровая схемотехника-2020, курсовой проект: видеолекции – URL: https://youtube.com/playlist?list=PLXyqqFIzpPd3ng1FB (дата обращения: 01.12.2024)

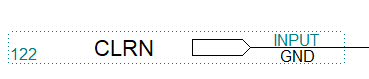

Микросхема 74168: сайт. – URL: https://www.microshemca.ru/74168/ (дата обращения: 01.12.2024)