МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра электронных приборов и устройств

КУРСОВАЯ РАБОТА

по дисциплине «Цифровая схемотехника»

Тема: «Разработка электронного устройства»

Студент гр. |

|

. |

Преподаватель |

|

Ухов А.А. |

Санкт-Петербург

2024

АННОТАЦИЯ

В данной курсовой работе изложены ключевые этапы разработки и моделирования электронного устройства (устройство для измерения частоты). Структура работы включает: 1) задания к курсовому проекту; 2) аннотации; 3) введения; 4) основные части (разделы); 5) заключение; 6) список литературы. В первом разделе описано деление цифрового блока на основные составляющие его блоки и объяснение их работы. Второй раздел посвящен изображению и объяснению полученных тактовых диаграмм. В конце данной работы приведена итоговая схема устройства.

ANNOTATION

This course work describes the key stages of development and simulation of an electronic device (frequency measuring device). The structure of the work includes: 1) task for the course project; 2) annotations; 3) introduction; 4) main parts (sections); 5) conclusion; 6) list of literature. The first section describes the division of the digital block into its main components and explains their operation. The second section is devoted to the representation and explanation of the obtained clock diagrams. At the end of this work, a final diagram of the device is shown.

СОДЕРЖАНИ

АННОТАЦИЯ 3

ВВЕДЕНИЕ 5

1. РАЗРАБОТКА СХЕМЫ 6

1.1. Блок синхронизации входного сигнала 6

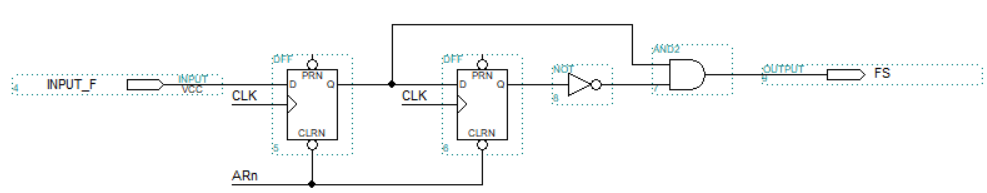

Рисунок 1 – Блок входных сигналов 6

1.2. Блок формирования импульсов c периодом 1 с и 0.1 с 7

Рисунок 2 – Блок формирования импульсов с периодом 1 с и 0.1 с 7

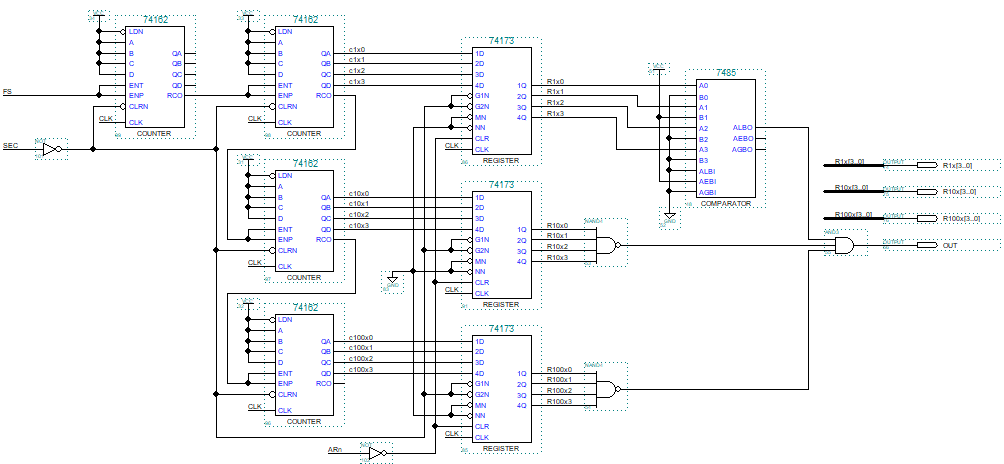

1.3. Блок подсчета, хранения и сравнения 8

2. ВРЕМЕННЫЕ ДИАГРАММЫ 11

Рисунок 4 – Временные диаграммы работы цифрового устройства для TFS = 0.15 мс (слева) и TFS = 13.2 мс (справа) 11

Рисунок 5 – Временные диаграммы работы цифрового устройства для FS менее 20 Гц 13

По временным диаграммам видно, что в начале работы до 1 секунды блок еще не зафиксировал измерения в регистрах, и показывает 000. Через 1 секунду появляется строб, и регистры записывают значения количества импульсов со счетчиков. Частота при этом показывается в формате 3-х чисел от 0 до 9, и является количеством десятков Гц в реальной частоте. Так как частоты входного сигнала не меняется, то измеренное значение повторяется в течение всей работы. 13

ЗАКЛЮЧЕНИЕ 14

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 15

ВВЕДЕНИЕ 5

1. РАЗРАБОТКА СХЕМЫ 6

1.1 Блок синхронизации входного сигнала 6

1.2 Блок формирования импульсов c периодом 1 с и 0.1 с 7

1.3 Блок подсчета, хранения и сравнения 8

2. ВРЕМЕННЫЕ ДИАГРАММЫ 9

ЗАКЛЮЧЕНИЕ 12

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 13

ВВЕДЕНИЕ

Данная курсовая работа описывает разработку цифрового блока, основа которого это 2 счетчика. Разрабатываемое устройство имеет 1 дискретный цифровой вход, 1 дискретный цифровой выход и параллельный выход для итогового числа. Также на вход блока поступают импульсы с длительностью не менее 10 мкс и периодом от 0,1 мс до 100 мс. Примеры устройств, в которых возможно использование данного блока: частотомер и расходомер. Электрические принципиальные схемы и результаты моделирования оформлены в среде MAX+ Plus 2.

РАЗРАБОТКА СХЕМЫ

Согласно заданию к курсовой работе, цифровой блок можно разбить на следующие блоки:

Блок входных сигналов;

Блок формирования импульсов для счетчика (делитель частоты) и сигнала SEC;

Блок подсчета импульсов, хранения данных и сравнения согласно условиям задачи;

1.1. Блок синхронизации входного сигнала

Что бы исключить ложные подсчеты необходимо создать линию синхронизации входного сигнала с тактовым сигналом. Линия синхронизации представляет собой детектор фронта входных импульсов, который по фронту каждого входного импульса на входе INPUT_F выдает импульс длительностью равной периоду тактового сигнала на выходе FS.

Для нормальной работы данного блока схемы необходимо, что бы тактовая частота была как минимум в 2 раза больше частоты входного сигнала.

Так как максимальная частота, которая будет подаваться на вход цифрового устройства равна 9 кГц, то оптимально будет выбрать частоту тактового сигнала CLK равной 20 кГц.

Для последовательностых элементов схемы предусмотрен вход асинхронного сброса ARn.

Рисунок 1 – Блок входных сигналов

1.2. Блок формирования импульсов c периодом 1 с и 0.1 с

Измерение частоты цифрового устройства основывается на подсчете количества импульсов за одну секунду. Для задания временного интервала для данной схемы необходимо создать блок для формирования секундных отсчетов. Для этой цели подойдет делитель частоты на счетчиках.

Делитель был создан на основе микросхемы 74160 – 4-разрядный десятичный синхронный счетчик с возможностью сброса и каскадирования. Первые 3 счетчика в каскаде делят входную тактовую частоту (20 кГц) на 1000, затем с помощью Т-триггера сигнал с 3 счетчика делится по частоте еще на 2 и на выходе 100MS мы получаем синхронизированный стробирующий сигнал с периодом 0.1 с (10 Гц), что необходимо по заданию.

4 счетчик в каскаде делит частоту еще на 10 и через Т-триггер и D-триггер на выходе SEC мы получаем необходимые ежесекундные отсчеты (синхронизированный стробирующий сигнал с периодом 1 с)

Данная часть схемы также имеет общий вход асинхронного сброса ARn.

Рисунок 2 – Блок формирования импульсов с периодом 1 с и 0.1 с

1.3. Блок подсчета, хранения и сравнения

Основная часть устройства, которая считает частоту содержит 4 счетчика 74162, 3 параллельных регистра 74173 и цифровой компаратор 7485.

Счетчики имеют функционал аналогичный модели 74160, но вход сброса является синхронным, первый счетчик в каскаде предназначен для деления и подачи синхронизированной частоты FS на следующие счетчики, обеспечивая разрешение в 10 Гц, так как импульс на выходе переноса появляется на каждый десятый импульс FS. 3 последующих счетчика образуют 3-ч декадный счетчик, считающий импульсы от 000 до 999, но так как макс. частота на входе 9 кГц, то нет необходимости защищать схему от переполнения.

Блок формирования секундных отчетов подает импульсы на входы синхронного сброса CLRN и разрешения записи регистров G1N, G2N, благодаря чему обеспечивается подсчет количества импульсов за одну секунду. Итоговая частота представляет собой 3 двоично-десятичных числа показывающих частоту в кГц – N , NN кГц, с точностью до 10 Гц.

Компаратор на выходе подключен к сравнению значения регистра младшего разряда с числом 0010, которое соответствует значению 20 Гц. Если значение в регистре меньше этого числа при условии, что и старшие регистры содержат «0», то значит частота на входе устройства меньше 20 Гц, и на цифровом выходе OUT появляется «1».

Рисунок 3 - Блок подсчета, хранения и сравнения

ВРЕМЕННЫЕ

ДИАГРАММЫ

ВРЕМЕННЫЕ

ДИАГРАММЫ

Рисунок 4 – Временные диаграммы работы цифрового устройства для TFS = 0.15 мс (слева) и TFS = 13.2 мс (справа)

Рисунок 5 – Временные диаграммы работы цифрового устройства для FS менее 20 Гц

По временным диаграммам видно, что в начале работы до 1 секунды блок еще не зафиксировал измерения в регистрах, и показывает 000. Через 1 секунду появляется строб, и регистры записывают значения количества импульсов со счетчиков. Частота при этом показывается в формате 3-х чисел от 0 до 9, и является количеством десятков Гц в реальной частоте. Так как частоты входного сигнала не меняется, то измеренное значение повторяется в течение всей работы.

Если частота входного сигнала менее 20 Гц, в 3 случает период входного сигнала составляет 60 мс (16.6 Гц), то младший регистр хранит значение первого десятка, а компаратор выдает на выход «1», сообщая о том, что частота меньше 20 Гц, при этом в 2-ух старших регистрах хранится «0» и через элемент «4И-НЕ» подается «1», для исключения случаев появления «1» при кратной 20 Гц частоте (120 Гц, 9520 Гц, 1120 Гц и тд.)

ЗАКЛЮЧЕНИЕ

В ходе выполнения курсовой работы был разработан цифровой блок для устройства измерения частоты. Построены основные части данного блока, и описан принцип их работы. Кроме этого, все эти схемы были скомпилированы в программе MAX+plus 2, чтобы проверить на наличие каких-либо ошибок и предупреждений. Далее была построена тактовая диаграмма с определенными выводами. Таким образом, промоделировав разработанное устройство, можно с уверенностью сказать, что оно работает без нареканий и выполняет требования, представленные к курсовому проекту.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

Цифровая схемотехника, методические указания по проведению лабораторных занятий, внутренняя рабочая версия каф. ЭПУ СПбГЭТУ «ЛЭТИ» – 2024

Цифровая схемотехника, вспомогательный материал для консультаций по выполнению курсового проекта каф. ЭПУ, СПбГЭТУ «ЛЭТИ» – 2020 г.

Список микросхем 7400 семейства: сайт. – URL: https://electronics.fandom.com/ru/wiki/Список_микросхем_7400_семейства (дата обращения: 19.12.2022)

Микросхема 74162: сайт. – URL: https://www.microshemca.ru/74162/

Микросхема 74173: сайт. – URL: https://www.microshemca.ru/74173/

Микросхема 7485: сайт. – URL: https://www.microshemca.ru/7485/

Электронный ресурс: Кафедра КиТ ЭВС. URL: https://kurskelectronic.ru/library/ispolzovanie-sapr-maxplus-ii-dlya-razrabotki-cifrovyx-ustrojstv-na-plis-firmy-altera/