МИНОБРНАУКИ РОССИИ Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) Кафедра электронных приборов и устройств |

||||||

отчет по лабораторной работе №3 по дисциплине «Цифровая схемотехника» Тема: «Исследование схем триггеров»

|

||||||

|

||||||

Санкт-Петербург 2024 г. |

Цели работы: – собрать и исследовать схемы простейших RS-триггеров на ЛЭ 2И-НЕ и 2ИЛИ-НЕ, ознакомиться с принципом действия и временными диаграммами работы триггера-защелки, универсального RS-D триггера, D-триггера с разрешением и синхронного JK-триггера, реализованных на ПЛИС.

Обработка результатов

Вариант №20

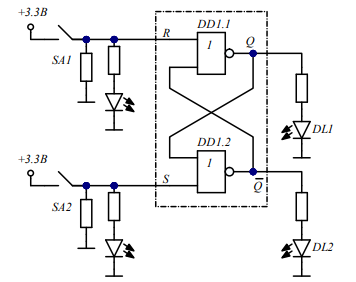

Схема RS-триггера на ЛЭ 2ИЛИ-НЕ приведена ниже.

Рисунок 1 - Исследованная схема RS-триггера на ЛЭ

1)

1)

2)

2)

Q

S

R

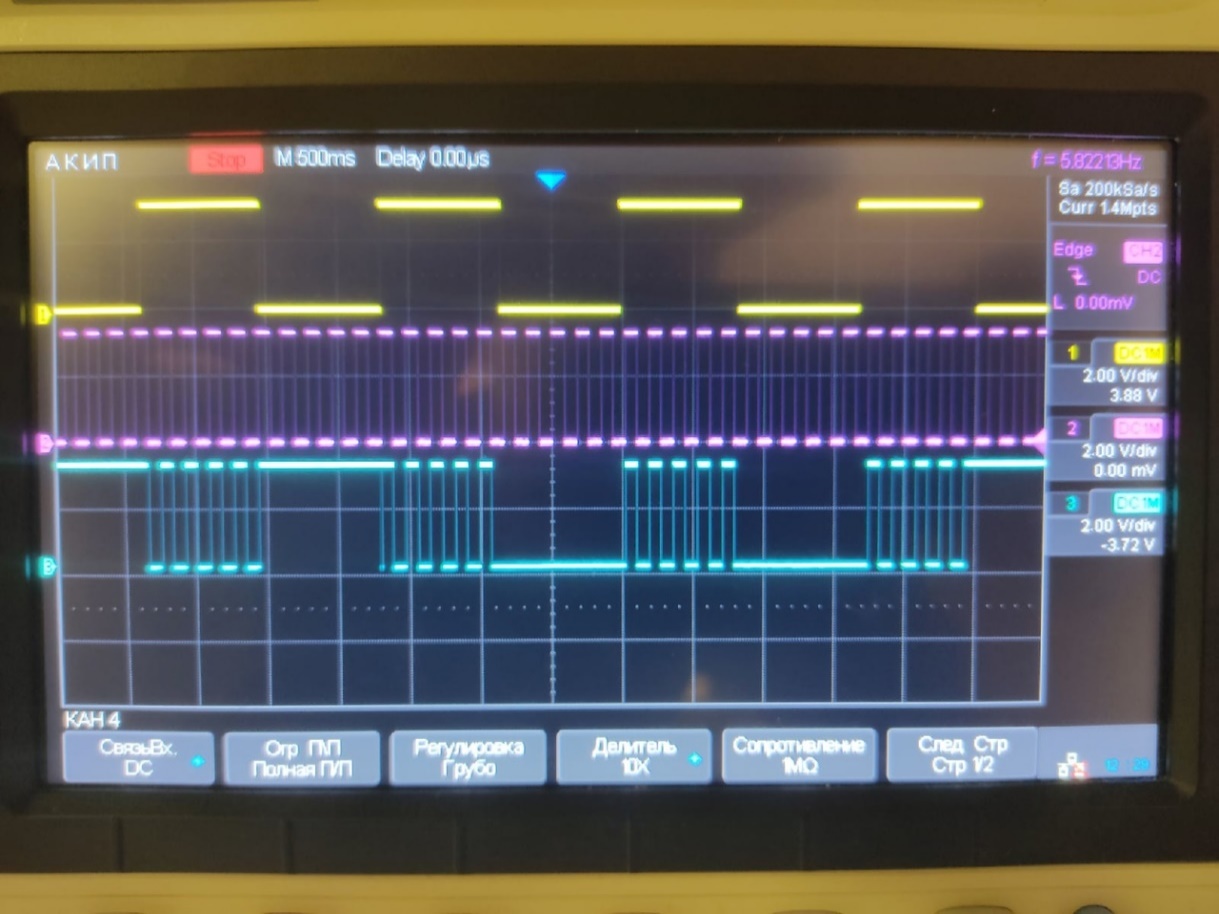

Рисунок 2 – Осциллограмма работы RS-триггера на ЛЭ

Как видно, подача уровня лог. «1» на вход R при S = 0 сбрасывает триггер 𝑄n+1=0. Повторная подача того же уровня не приводит к изменению состояния выхода схемы.

Подача уровня лог. «1» на вход S снова устанавливает триггер в состояние

,

повторная подача того же уровня на S

не приводит к изменению состояния

схемы.

,

повторная подача того же уровня на S

не приводит к изменению состояния

схемы.

При одновременной подаче уровня лог. «1» на оба входа, на обоих выходах схемы устанавливаются уровни лог. «0». Такое состояние называется метастабильным.

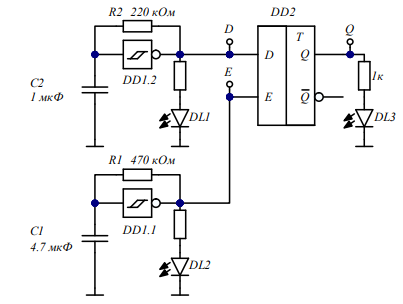

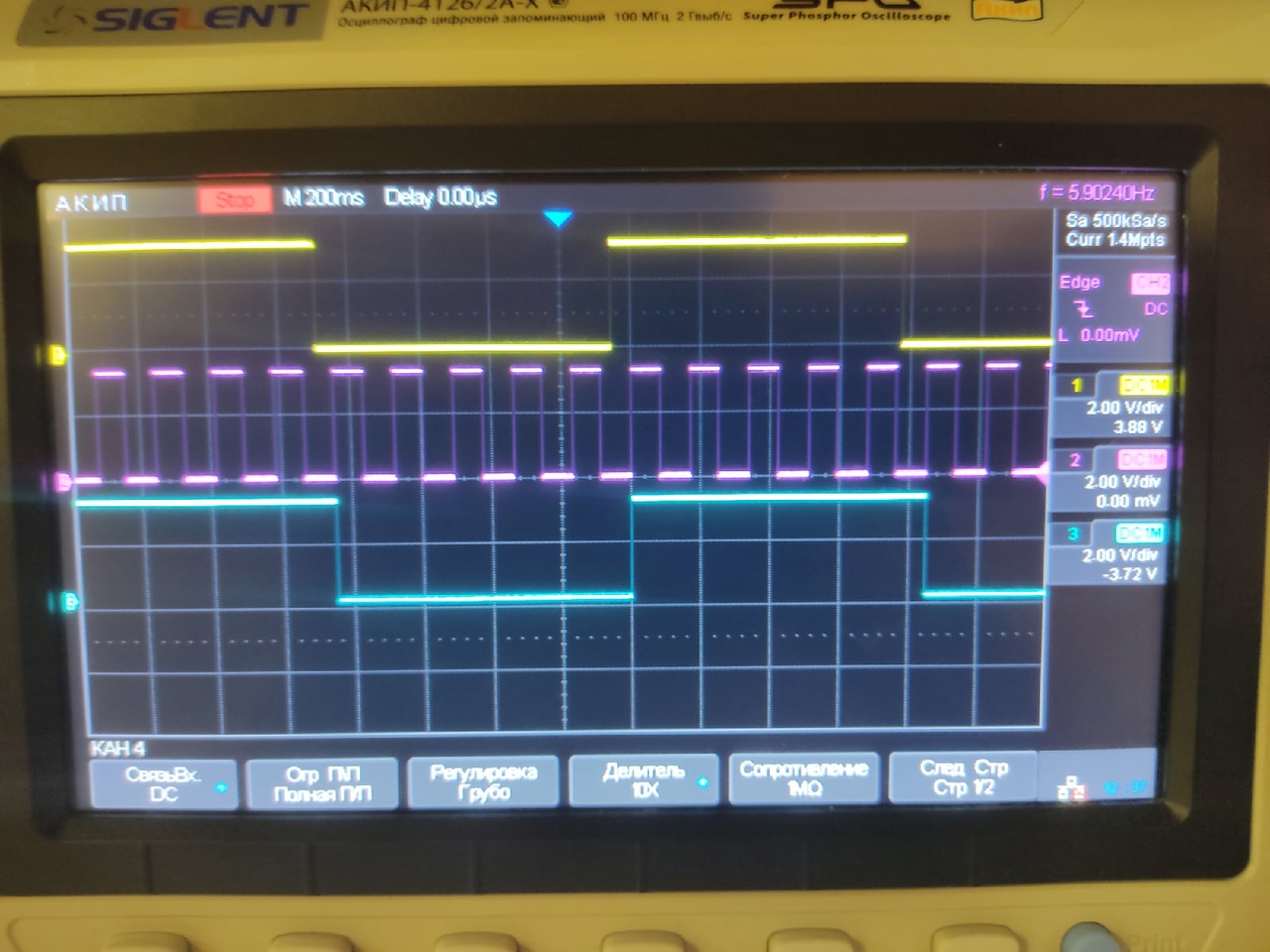

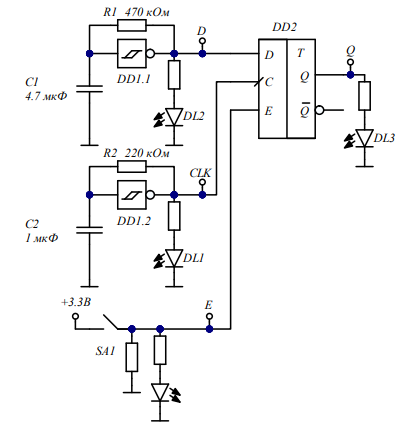

Схема, использованная для исследования триггера-защелки, приведена ниже.

Рисунок 3 - Схема для исследования триггера-защелки

1)

2)

D

Q

E

Рисунок 4 - Осциллограмма работы триггера-защелки

По работе триггера защелки видно, что установлении входа триггера Е на уровень лог. «1», триггер переходит в режим прозрачности 1) когда выходной сигнал Q полностью повторяет входной сигнал с D. При переходе разрешающего входа Е в лог. «0», триггер переходит в режим хранения 2), запоминая последнее состояние со входа D и защелкивая вход.

3 Схема, использованная для исследования универсального RS-D триггера, приведена ниже.

Рисунок 5 - Схема для исследования универсального RS-D триггера

D

С

Q

Рисунок 6 - Осциллограмма работы универсального RS-D триггера

Видно, что переключение состояния триггера задается уровнем входа D, однако непосредственно переход происходит по фронту сигнала С. То есть переключение триггера синхронизировано с тактовым сигналом С.

Входы

и

и

принудительно (независимо от D

и C)

переводят триггер в состояния характерные

для обычного RS

триггера с инверсными входами, то есть

при подаче уровня лог «0» на вход

в любой момент времени устанавливает

триггер в состояние 𝑄

= 1. Подача лог. «0» на вход

в любой момент времени устанавливает

триггер в состояние 𝑄

= 0.

принудительно (независимо от D

и C)

переводят триггер в состояния характерные

для обычного RS

триггера с инверсными входами, то есть

при подаче уровня лог «0» на вход

в любой момент времени устанавливает

триггер в состояние 𝑄

= 1. Подача лог. «0» на вход

в любой момент времени устанавливает

триггер в состояние 𝑄

= 0.

4. Схема, использованная для исследования D-триггера с разрешением, приведена ниже.

Рисунок 7 - Схема для исследования D-триггера с разрешением

1→0

Q

С

D

Рисунок 8 - Осциллограмма работы D-триггера с разрешением

Как видно по рисунку до тех пор, пока уровень Е держится на лог. «1» запись в триггер разрешена, и сигнал на выходе Q задается сигналом D по фронту от тактового генератора, то есть триггер записывает значения D, но как только разрешающий вход Е переводится в лог. «0», запись запрещается и триггер запоминает свое состояние – режим хранения данных.

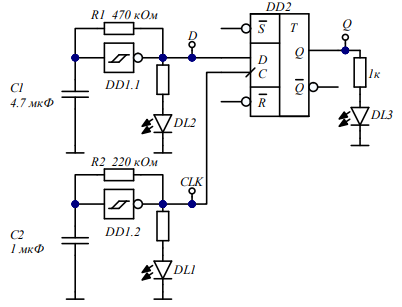

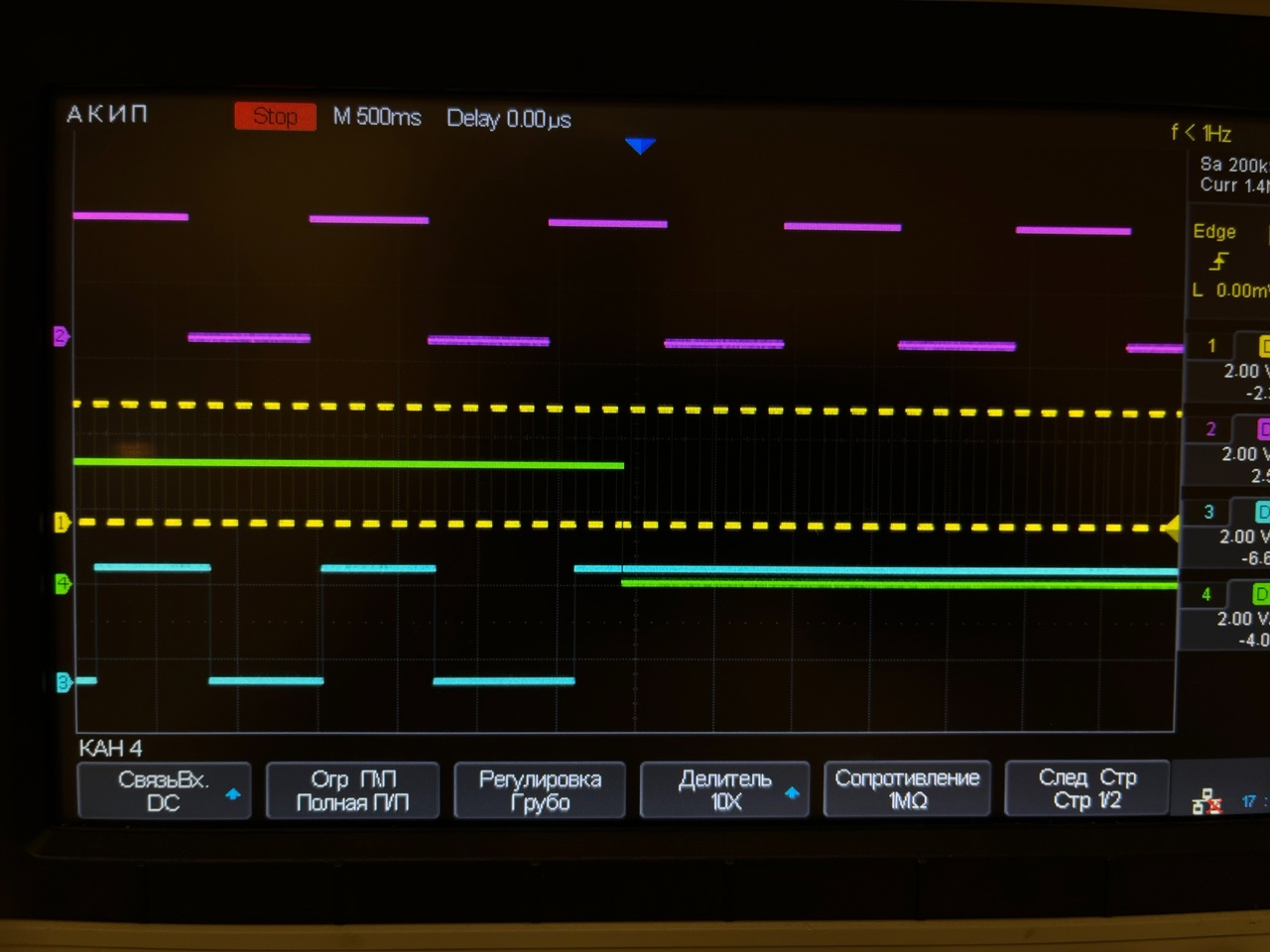

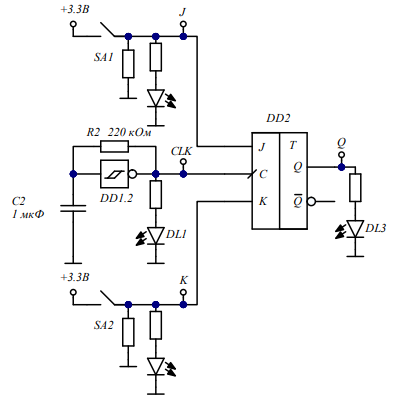

5. Схема, использованная для исследования синхронного JK-триггера приведена ниже.

Рисунок 9 - Схема для исследования синхронного JK-триггера

Q

K

J

С

Рисунок 10 - Осциллограмма работы синхронного JK-триггера

Видно, что подача импульсов на входы J и K аналогична работе синхронного RS триггера, то есть J задает уровень сигнала на выходе лог. «1» по фронту тактового сигнала, а К сбрасывает его на лог. «0» также по фронту сигнала С, однако, как только оба входа J и K принимают уровень лог. «1» выходной сигнал начинает переключаться по фронту сигнала С, причем сам факт переключения не зависит от состояния выхода Q, благодаря чему на выходе Q образуется импульсный сигнал с вдвое меньшей частотой чем тактовый сигнал, благодаря чему такой режим можно назвать делением частоты.

ВЫВОД

В ходе выполнения лабораторной работы были исследованы несколько схем триггеров: RS-триггера на ЛЭ 2ИЛИ-НЕ; триггера-защелки; универсального RS-D триггера; D-триггера с разрешением; синхронного JK-триггера. Сделаны фотографии осциллограмм для дальнейшего выполнения обработки результатов. Также подведены некоторые итоги.

Кроме этого, в ходе снятия данной работы были исследованы принципы действия схем триггеров. Благодаря теоретической части познакомились еще с несколькими схемами триггеров со своими входами управления и особенностями работы, доступных в виде готовых интегральных схем или функциональных узлов ПЛИС.