Мікропроцесорні пристрої. Питання до іспиту

1.1 |

1.2 |

1.3 |

1.4 |

1.5 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

1.6 |

1.7 |

1.8 |

1.9 |

1.10 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

1.11 |

1.12 |

1.13 |

1.14 |

1.15 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Списать с лекции |

Списать с лекции |

Списать с лекции |

|

|

|

|

|

|

|

1.16 |

1.17 |

1.18 |

1.19 |

1.20 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Списать с лекции |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

2.1 |

2.2 |

2.3 |

2.4 |

2.5 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

На половину |

Всё выполнено |

Списать с лекции |

|

|

|

|

|

|

|

2.6 |

2.7 |

2.8 |

2.9 |

2.10 |

|

|

|

|

|

|

|

Списать с лекции |

Списать с лекции |

Списать с лекции |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

2.11 |

2.12 |

2.13 |

2.14 |

2.15 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

2.16 |

2.17 |

2.18 |

2.19 |

2.20 |

|

|

|

|

|

|

|

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

Всё выполнено |

|

|

|

|

|

|

|

2.21 |

2.22 |

2.23 |

Сноска:1.1- 1 модуль 1 |

||

|

|

|

задание.Посилання до |

||

Всё выполнено |

Всё выполнено |

Всё выполнено |

|||

запитань |

|

||||

|

|

|

|

||

|

|

|

|

|

|

Модуль 1. Архітектура та програмування мікропроцесорних пристроїв.

1. Загальна структура мікропроцесора. Процесори з повною системою команд

Ответ:https://studfile.net/preview/5157863/page:10/#:~:text=%D0%9C% D0%9F%20%D0%BC%D1%96%D1%81%D1%82%D0%B8%D1%82% D1%8C%20%D1%82%D1%80%D0%B8%20%D0%BE%D1%81%D0% BD%D0%BE%D0%B2%D0%BD%D1%96%20%D0%BF%D1%80%D0% B8%D1%81%D1%82%D1%80%D0%BE%D1%97,%3A%20%D0%A8% D0%90%2C%20%D0%A8%D0%94%20%D1%96%20%D0%A8%D0%9 A.

Загальна структура мікропроцесора

5.3. Структура мікропроцесора

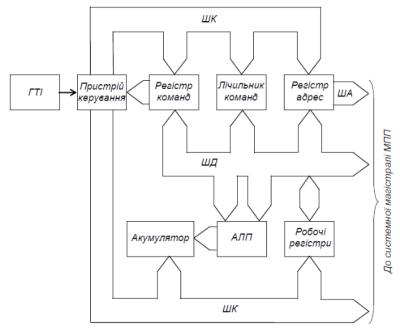

Структурну схему МП наведено на рис. 5.3.

Рисунок 5.3 – Структура мікропроцесора МП містить три основні пристрої: арифметико-логічний пристрій (АЛП),

регістри даних (РД) і пристрій керування (ПК). Ці та інші пристрої, що беруть

участь у пересиланні даних, з’єднано шинами внутрішньої магістралі: ША, ШД і ШК.

Синхронізує і задає темп роботи (швидкодію) МП генератор тактових імпульсів (ГТІ).

АЛП являє собою комбінаційний пристрій, у якому відбувається виконання арифметичних і логічних операцій над даними.

Регістри забезпечують виконання функцій МП за рахунок зберігання кодів даних, адрес, команд та ін.

Акумулятор є основним регістром МП при діях з даними. Більшість арифметичних і логічних операцій з двома словами даних здійснюється з використанням АЛП і акумулятора.

У регістрі стану (ознакабо прапорців) зберігаються ознаки результату побіжної операції АЛУ (нульовий, додатний, від’ємний та ін.). Ці ознаки використовуються при виконанні наступних команд, наприклад, для розгалуження програми.

Лічильник команд зберігає номер команди, що виконується і тієї, що буде виконуватися наступною. Перед початком виконання програми до нього заноситься адреса її першої команди.

Регістр адреси пам’яті містить адресу пам’яті, що буде використана МП у

наступному такті роботи. Його виходом є ША.

Регістр команд зберігає код поточної виконуваної команди. Робочі регістри є внутрішньою надоперативною пам’яттю МП і

застосовуються для проміжного зберігання кодів даних і адрес, забезпечуючи підвищення швидкодії.

Підключення внутрішньої магістралі МП до системної магістралі МПУ

відбувається через буферні регістри інтерфейсу і вихідні підсилювачі. Пристрій керування узгоджує роботу всіх вузлів МП.

+

Процесори з повною системою команд http://vozom.ho.ua/MP/page42.html

З погляду системи команд і способів адресації операндів процесорне ядро сучасних 8-розрядних МК реалізує один із двох принципів побудови процесорів:

●процесори з CISC-архітектурою, які реалізують так звану повну систему команд (Complicated Instruction Set Computer).

●процесори з RISC-архітектурою, що реалізують скорочену систему команд (Reduced Instruction Set Computer).

CISC-процесори виконують великий набір команд із розвитими можливостями адресації, даючи виробнику можливість вибрати найбільше придатну команду для виконання необхідної операції. У застосуванні до 8-розрядних МК процесор з CISC-архітектурою може мати однобайтний, двохбайтний і трьохбайтний (рідко чотирьохбайтний) формат команд. При цьому система команд, як правило, неортогональна, тобто не всі команди можуть використовувати кожен зі способів адресації стосовно до кожного з регістрів процесора. Вибірка команди на виконання здійснюється побайтно протягом декількох циклів роботи МК. Час виконання команди може складати від 1 до 12 циклів. ДО МК із CISC-архітектурою відносяться МК фірми Intel з ядром MCS-51, які підтримуються в даний час цілим рядом виробників, МК сімейств НС05, НС08 і НС11 фірми Motorola і ряд інших.

2. Загальна структура мікропроцесора.(Дивитись відповідь на питання №1) Процесори з скороченою системою команд

Ответ: http://vozom.ho.ua/MP/page42.html

У процесорах з RISC-архітектурою набір команд, які виконуються, скорочений до мінімуму. Для реалізації більш складних операцій приходиться комбінувати команди. При цьому всі команди мають формат фіксованої довжини (наприклад, 12, 14 або 16 біт), вибірка команди з пам'яті і її виконання здійснюється за один цикл (такт) синхронізації. Система команд RISC-процесора припускає можливість рівноправного використання всіх регістрів процесора. Це забезпечує додаткову гнучкість при виконанні ряду операцій. До МК із RISC-процесором відносяться МК AVR фірми Atmel, МК PIC16 і PIC17 фірми Microchip і інші.

На перший погляд, МК із RISC-процесором повинні мати більш високу продуктивність у порівнянні з CISC МК при одній і тій же тактовій частоті внутрішньої магістралі. Однак на практиці питання про продуктивність більш складне і неоднозначне.

3. Логічна структура мікропроцесорної системи. Архітектура фон Неймана.

Ответ:

Логічна структура мікропроцесорної системи

Мікропроцесор складається з арифметико-логічного

пристрою|устрою| (АЛП), регістрів|реєстрів|, внутрішньої шини даних, пристрою|устрою| управління.

Арифметико-логічний пристрій|устрій| призначений для виконання арифметичних і логічних операцій.

До арифметичних операцій відносяться, як правило, операції складання і віднімання.

Архітектура фон Неймана. Ответ с лекции, если загугли ть можно найти и в интернете

Існують два основні типи архітектури – фоннеймановска| і

гарвардська. На рис. 3.2 приведена фоннеймановска| архітектура, яку запропонував в 1945 р. американський математик Джо фон

Нейман. Особливість цієї архітектури полягає в тому, що програма і дані розташовуються|перебувають| в спільної |спільній| пам'яті,

доступ до якої здійснюється по одній шині даних і команд.

4. Пристрій і принцип дії МП 8080. Функціональні блоки МП.

Ответ:

Пристрій і принцип дії МП 8080 https://uk.wikipedia.org/wiki/Intel_8080

Intel 8080 — 8-бітний мікропроцесор, випущений компанією Intel в квітні 1974 року. Являє собою вдосконалену версію процесора Intel 8008. За твердженням Intel, цей процесор забезпечував десятикратний приріст продуктивності в порівнянні з мікропроцесором Intel 8008.

Опис[ред. | ред. код]

Процесор випускався по новітній тоді 6-мікронній N-МОН технології, що дозволило розмістити на кристалі 4500 транзисторів. Процесор, хоча і був збудований на архітектурі Intel 8008, але мав багато відмінностей від свого попередника, завдяки яким і отримав велику популярність. В новому процесорі була дуже розвинута система команд — 16 команд передачі даних, 31 команда для їх оброблення, 28 команд для переходу (з прямою адресацією), 5 команд керування. В мікропроцесорі Intel 8080 не було команд множення, для їх використання доводилось застосовувати співпроцесор. Процесор, завдяки присутності 16-розрядної адресної шини, міг адресувати 64 Кбайт пам'яті, яка тепер не поділялась на пам'ять команд і даних. Хоча процесор і був 8-розрядним і містив 7 8-бітних регістрів (A, B, C, D, E, H, L), він міг опрацьовувати і 16-розрядні числа, для цього об'єднувались деякі пари регістрів (BC, DE, HL). В новому процесорі використовувався стек зовнішньої пам'яті (в Intel 8008 стек був внутрішнім).

На базі мікропроцесора Intel 8080 фірмою MITS був випущений «перший у світі мінікомп'ютерний комплект, який може конкурувати з промисловими зразками» (персональний комп'ютер) Altair 8800, який користувався неймовірно великою по тому часі популярністю (MITS не встигала навіть вчасно опрацьовувати замовлення).

Функціональні блоки МП. ответ с лекций

Під архітектурою мікропроцесора розуміється перелік основних

блоків мікропроцесора, зв'язки і взаємодія між ними. Архітектура мікропроцесора містить:

|- структурну схему МП;

-програмну модель МП (опис функцій регістрів|реєстрів|);

-інформацію про організацію пам'яті (ємність|місткість| пам'яті і

способи адресації);

-опис організації процедур введення-виведення|висновку|.

5. Основні типи машинних циклів МП 8080.

Ответ:https://studfile.net/preview/5994067/

Виконання команд в МП і8080. Кожна команда у МП виконується протягом

командного циклу. Командний цикл складається із циклу вибірки команди та циклу виконання команди (рис. 2.3).

Рис. 2.3 – Приклад командного циклу 8-розрядного МП

Тривалість циклу вибірки команди залежить від формату команди (кількості байтів у машинному коді команди). Команди займають від одного до трьох байтів у програмній пам’яті. Багатобайтові команди зберігаються в сусідніх комірках пам’яті. Для вибірки однобайтової команди (наприклад, додавання акумулятора А і регістра В - ADD B) потрібне одне звернення до пам’яті, для вибірки трибайтової команди (наприклад, виклику підпрограми за адресою ADDR-CALL ADDR) – три звернення. Тривалість циклу виконання команди залежить від засобу адресації операндів. Так, при виконанні команд з регістровою адресацією не потрібне додаткове звернення до пам’яті для читання операнда, в командах з непрямою адресацією таке звернення необхідне. Тому тривалість командного циклу в МП і8080 є різною для різних команд і визначається кількістю звернень до пам’яті або до зовнішнього

пристрою.

Інтервал, протягом якого здійснюється одне звернення процесора до пам’яті чи до зовнішнього пристрою, визначається як машинний цикл М. Отже,

командний цикл процесора складається з деякої кількості машинних циклів (залежно від типу команди). У наведеному на рис.2.2. прикладі цикл вибірки складається з двох машинних циклів (М1 і М2), а цикл виконання – з одного

машинного циклу (М3). У команді може бути від одного (для однобайтових команд з регістровою адресацією) до п’яти (для трибайтових складних команд)

машинних циклів.

6. Система команд. Типи команд.

Ответ: с лекций страница 20.

Кожна команда мікроконтролера PIC16F87X складається з одного

14-розрядного слова, розділеного на код операції (OPCODE), що визначає тип команди і один або декілька операндів, що визначають

операцію команди. Команди розділені на наступні групи: байт

орієнтовані команди, битий орієнтовані команди, команди управління і операцій з константами. Опис полів команд і формат

команд наведені в таблиці на рис.6.1.

Для байт орієнтованих команд "f" є покажчиком регістра, а "d" покажчиком адресата результату. Покажчик регістра визначає, який

регістр повинен використовуватися в команді. Покажчик адресата визначає, де буде збережений результат. Якщо "d"=0, результат зберігається в регістрі W. Якщо "d"=1, результат зберігається в регістрі, який використовується в команді.

Убіт орієнтованих командах "b" визначає номер бита, що бере участь в операції, а "f" – покажчик регістра, який містить цей біт.

Укомандах управління або операціях з константами "k" представляє вісім або одинадцять біт константи або значення літералів.

Всі команди виконуються за один машинний цикл, окрім команд умови, в яких отриманий дійсний результат, і інструкцій тих, що змінюють значення лічильника команд РС. У разі виконання команди за два машинні цикли, в другому циклі виконується інструкція NOP. Один машинний цикл складається з чотирьох тактів генератора. Для тактового генератора з частотою 4 Мгц всі команди виконуються за 1 мкс, якщо умови істинно або змінюється лічильник команд РС, команда виконується за 2 мкс. Список команд наведений в рис.6.2.

7. Система команд (див. питання 6). Способи адресації, реалізовані

в МП 8080.

Ответ: http://antibotan.com/file.html?work_id=516314 відкрилось тільки з ВПНом.

1.Операнд, який розуміється. В команді не задаються явно ні адреса операнда, ні він сам. Операнд розуміється і фактично

задається кодом операції команди. найчастіше таким операндом є одиниця, що додається чи віднімається від попереднього значення

числа .

2.Неявна адресація. При цьому способі адресації адреса

одного або двох операндів неявне задається в йоді операції.

Операція може, наприклад, виконуватися вмістом акумулятора ,

який адресується кодом команди і спеціамно його вказувати не

потрібно. У МП КР580 перший операнд завжди знаходиться в акумуляторі, а другий може бути адресований прямо, непрямо або

безпосередньо.

3.Безпосередня адресація. При безпосередній адресації

оеранд є частиною виконуваної команди.

4.Пряма регістрова адресація. У полі операндів команди

задаються адреси регістрів загального призначення (РЗП) A,B,C,D,E,H,L

5.Пряма адресація. У полі операнда міститься повна 1б-6ітна адреса байта пам'яті. За допомогою прямої адресації можна звертатип до будь-якого байта адресного простору

6.Непряма регістрова адресація. В адресному полі команди казується код пари регістрів, в якій міститься адреса комірки пам'яті, де розміщені потрібні дані.

8. Програмування на мові Асемблер. Етапи розвитку програми.

Ответ: с лекций страница 29

6.2.1. Асемблер MPASM

Асемблер MPASM являє собою інтегроване програмне середовище для розробки програмних кодів PIC мікроконтролерів усіх сімейств. Випускається фірмою Microchip у двох варіантах: для роботи під DOS і для роботи під Windows 95/98/NT. Асемблер MPASM може використовуватися як самостійно, так і в складі інтегрованого середовища розробки MPLAB. Він включає кілька програм: власне MPASM, MPLINK і MPLIB, причому кожна з них має власний інтерфейс.

Програма MPASM може використовуватися для двох цілей:

·генерації виконуваного (абсолютного) коду, призначеного для запису в МК за допомогою програматора;

·генерації переміщуваного об'єктного коду, що потім буде

зв'язаний з іншими асембльованими чи компільованими модулями.

Код, який виконується, є для MPASM вихідним кодом за замовчуванням. При цьому всі змінні джерела повинні бути явно описані в тексті програми чи у файлі, що підключається за допомогою директиви INCLUDE <filename>. Якщо при асемблюванні не виявляється помилок, то генерується вихідний .hex-файл, що може бути завантажений у МК за допомогою програматора.

При використанні асемблера MPASM у режимі генерації переміщуваного об'єктного коду формуються об'єктні модулі, які можуть бути згодом об'єднані з іншими модулями за допомогою компоновника MPLINK. Програма-компоновник MPLINK перетворить переміщувані об'єктні коди в бінарний виконуваний код, прив'язаний до абсолютних адрес МК. Бібліотечна утиліта MPLIB дозволяє для зручності роботи згрупувати переміщувані об'єкти в один файл чи бібліотеку. Ці бібліотеки

можуть бути зв'язані компоновником MPLINK у файл вихідного об'єктного коду асемблера MPASM.

Програми MPASM і MPLINK доступні через оболонку MPASM, тоді як MPLIB доступна тільки з свого командного рядка.

Вихідним файлом для асемблера MPASM за замовчуванням є файл із розширенням .ASM. Текст вихідного файлу повинен відповідати вимогам синтаксису, який наведено далі.

Етапи розвитку програми З конспекта, Лекція №3, сторінка 22.

Якщо цільова функція контролера сформульована, тобто задача на розробку поставлена, то для отримання тексту початкової програми необхідно виконати ряд послідовних дій:

1)докладний опис задачі;

2)аналіз задачі;

3)інженерну інтерпретацію задачі, бажано із залученням того або

іншого апарату формалізації (граф автомата, сіті Петрі, матриці

станів і зв'язності і т.п.);

4)розробку загальної блок-схеми алгоритму (БСА) роботи

контролера;

5)розробку БСА окремих процедур, виділених на основі модульного

принципу складання програм, що деталізуються;

6)детальне опрацьовування інтерфейсу контролера і внесення виправлень в загальне і деталізується БСА;

7) розподіл робочих регістрів і пам'яті МК;

8)формування тексту початкової програми.

9. Організація пам'яті даних. Банки даних. Формування фізичної адреси при непрямій адресації.

Ответ:

Організація пам'яті даних.Банки даних. Джерело: аудио запись с лекции.

Загальний обсяг пам’яті даних складає 512 байт (це не дуже багато

в порівнянні з сучасними) Ці 512 байт, розділені на чотири банки.

Недолік такої системи в тому, що за допомогою прямої адресації ми

можемо обирати ячейки пам'яті тільки в одному банку і щоб звернутися до ще однієї ячейки в іншому банку, потрібно за допомогою бітів RB0 і RB1 перемикати ці банки. Не можна командою пересилати з робочого регистра в будь яку ячейку пам’яті, тільки в ячейку пам’яті будь якого банку

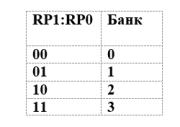

Організація пам'яті даних.Банки даних. Джерело: Лекція №6

Пам'ять даних розділяється на 4 банки, які містять регістри загального і спеціального призначення (SFR). Биті RP1 (STATUS<6>) і RP0 (STATUS<5>) призначені для управління банками. У таблиці приведений стан бітів, що управляють, при зверненні до банків пам'яті даних.

Об'єм пам'яті банків даних до 128 байт (7Fh). На початку банку розміщуються регістри спеціального призначення, потім регістри загального призначення, виконані як статичне ОЗУ. Всі реалізовані банки містять регістри спеціального призначення. Часто використовувані регістри спеціального призначення можуть відображатися і в інших банках пам'яті.

Непряма адресація, регістри INDF і FSR (Лекція №6)

Для виконання непрямої адресації необхідно звернутися до фізично не реалізованого регістра INDF. Звернення до регістра INDF фактично викличе дію з регістром, адреса якого вказана в FSR. Непряме читання регістра INDF (FSR=0) дасть результат 00h. Непрямий запис в регістр INDF не викличе ніяких дій (викликає дії на прапори АЛП в регістрі STATUS). 9-бит непрямої адреси IRP зберігається в регістрі STATUS<7>. Приклад 9-розрядної непрямої адресації показаний на рис.4.11, програми -

на рис.4.12.