Электроника и схемотехника, учебное пособие, Щ.А.С., О.А.Г

..pdf

271

смысле часто употребляют термин «нагрузочная способность» микросхемы;

коэффициент объединения по входу Коб, определяющий число входов микросхемы, по которым реализуется логическая функция;

допустимое напряжение статической помехи Uп;

средняя потребляемая мощность Рпот.ср.

Последние два параметра нуждаются в кратком пояснении.

Допустимое напряжение статической помехи характеризует статическую помехоустойчивость микросхемы, т. е. ее способность противостоять воздействию мешающего сигнала, длительность которого значительно превосходит время переключения микросхемы. Такая помеха и названа статической. Напряжение допустимой статической помехи обычно определяется как разность выходного и входного напряжений, соответствующих уровню логической единицы либо уровню логического нуля (в расчет принимается наименьшая величина).Средняя потребляемая мощность определяется как полусумма мощности, потребляемой микросхемой в состоянии логических 0 и 1.

усреднение

Общепринятое потребляемой мощности оправдано тем, что обычно во время работы в составе цифрового устройства логические микросхемы половину времени находятся в открытом состоянии, а другую половину - в закрытом.

Потребляемая мощность тесно связана с быстродействием микросхемы (ее временем переключения или рабочей частотой переключения): чем больше потребляемая мощность, тем с большей частотой может переключаться микросхема. Учитывая это, следует при расчетах реального энергопотребления цифрового устройства ориентироваться на мощность, потребляемую микросхемами в режиме переключения с заданной частотой.

Для многих типов микросхем, особенно ДТЛ и ТТЛ, характерно заметное увеличение потребляемой мощности с ростом частоты переключения.

Динамические параметры характеризуют свойства микросхемы в режиме пере-

ключения. В основном это временные параметры микросхемы:

- время перехода из состояния логического 0 в состояние логической 1 t 0,1;

- время задержки распространения сигнала при выключении микросхемы ;

-время перехода из состояния логической 1 в состояние логического 0 t 0,1;

-время задержки распространения сигнала при включении микросхемы

272

- среднее время задержки распространения сигнала tзд,р,ср.

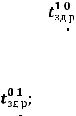

Динамические параметры определяются сравнением сигналов на входе и выходе логического элемента. На рис. 7.1 приведены временные диаграммы входного и выходного сигналов и показаны уровни отсчета, относительно которых определяются динамические параметры.

Рис. 7.1

Среднее время задержки служит усредненным параметром быстродействия н опреде-

ляется как полусумма задержек и tзд,р,ср. Этот параметр часто является основным при расчете рабочей частоты сложных логических устройств.

Среднее время задержки зависит от многих факторов: принципа построения логических элементов, наличия или отсутствия режима насыщения у входящих в схему транзисторов, величины переключающих токов и т. д. Кроме того, на среднее время задержки оказывают существенное влияние и условия работы микросхемы: температура окружающей среды, изменения питающих напряжений, емкость нагрузки и т. д. Стремление повысить надежность аппаратуры заставляет принимать в расчет те значения параметров логических элементов, в том числе и среднего времени задержки, которые соответствуют наихудшим условиям их работы. При использовании в расчетах справочных данных необходимо обращать внимание, для каких условий приведены эти данные, и при необходимости перерассчитать параметры с учетом реальных условий работы микросхем. Например, расчеты, уточняющие среднее время задержки, можно провести с помощью коэффициентов,

отражающих влияние на среднее время задержки температуры ( ) и емкости нагрузки

(Кс). При этом предполагается линейная зависимость среднего времени задержки от указанных факторов.

К числу динамических параметров следует отнести также динамическую помехо-

273

устойчивость, характеризующую способность микросхемы противостоять воздействию импульсной помехи, длительность которой соизмерима со средним временем задержки передачи сигнала через микросхему.

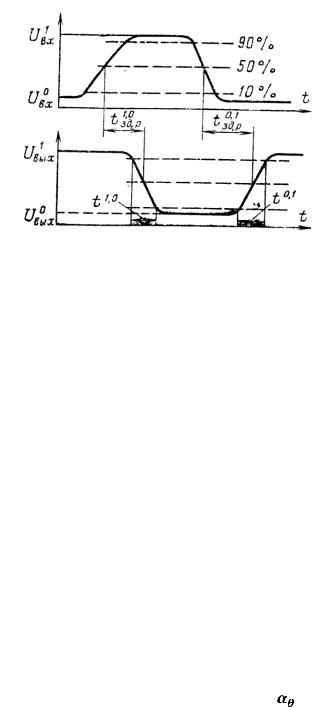

Количественно динамическая помехоустойчивость определяется амплитудой и длительностью импульса помехи, но чаще с помощью характеристики (рис. 7.1), отражающей зависимость допустимой амплитуды импульса помехи Uп от длительности этого импульса

tп.

Uп, B

tп, мкс

Рис. 7.2

На рис. 7.2 индексом I обозначена кривая зависимости Uп(tп), а индексом II – максимально допустимое напряжение статической помехи. Всѐ, что лежит выше кривой I, это область недопустимых импульсов помех. Из рисунка видно, что по мере увеличения длительности импульса помехи допустимая амплитуда помехи снижается до уровня максимально допустимого напряжения статической помехи. Заметим, что указанные пара-

метры широко используются для характеристики как микросхемы в целом, так и отдельных ее элементов: логических элементов, триггеров и т: Эксплуатационные параметры характеризуют работоспособность интегральных микросхем в условиях воздействий окружающей среды. К ним относятся: диапазон рабочих температур, допустимые механические нагрузки (вибрация, удары, линейные ускорения), границы допустимого изменение атмосферного давления, наибольшая влажность и некоторые другие.

7.2.1. . Мультиплексоры

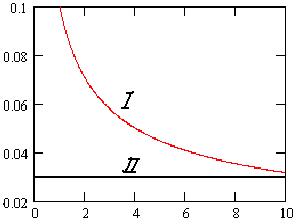

Примером комбинационных схем может служить мультиплексор - логическая схема,

274

представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на входах управления. Кроме информационных и управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и управляющих сигналов. Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На рис. 7.3 представлен мультиплексор 8x1, где информационные входы обозначены (Х1,…,Х8), код выборки устанавливается на входах (Х9, Х10, Х11), а инверсный выход обозначен как Y.

Рис. 7.3

7.2.2. Дешифраторы

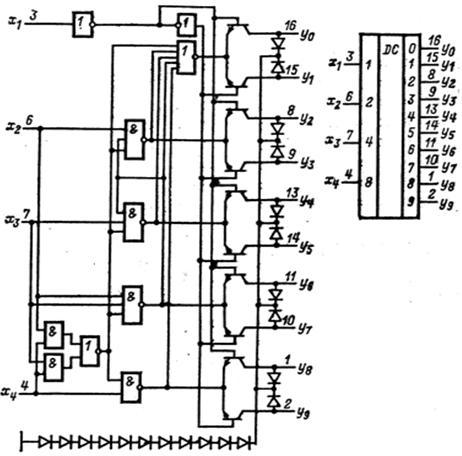

Дешифратор - логическая комбинационная схема, которая имеет n информационных входов и несколько выходов. Каждой комбинации логических уровней на входах будет

275

соответствовать активный уровень на одном из выходов. Обычно n равно 2,3 или 4.

На рис. 7.4 изображен дешифратор с n = 4, осуществляющий преобразование двоич- но-десятичного кода в десятичный. На входы (Х1,…,Х4) можно подать следующие комбинации логических уровней: 0000, 0001, 0010... 1010, всего 10 комбинаций.

Схема имеет 10 выходов, на одном из которых формируется низкий потенциал, на остальных - высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует числу М, определяемому состоянием входов (Х1,…,Х4). Например, если на входы (Х1,…,Х4) подана комбинация логических уровней 0011, то на выходе с номером Y3 установится нулевой уровень сигнала (Y3=0), а все ос-

.Y;

тальные выходы будут иметь уровень логической единицы.

Рис. 7.4

Помимо информационных входов (Х1,…,Х4) дешифраторы обычно имеют дополни-

276

тельные входы управления. Сигналы на этих входах, например, разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов.

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом - уровень логического нуля.

7.3.Cерии микросхем транзисторной логики с резистивными связями

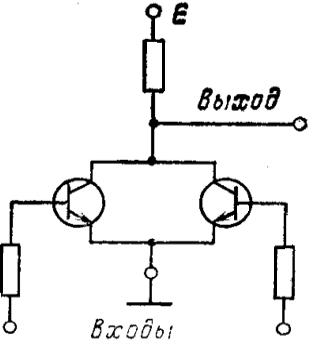

Кчислу микросхем типа РТЛ относятся серии КП3, КП4, КН5 и др. На рис.7.5 представлен базовый логический элемент указанных серий.

Элемент РТЛ выполняет логическую операцию ИЛИ—НЕ. Управление его работой осуществляется подачей сигналов в базовые цепи транзисторов: присутствие сигнала логической 1 хотя бы на одном входе приводит к отиранию соответствующего транзисторе и благодаря этому обеспечивается состояние логического 0 на выходе элемента.

Рис. 7.5

К выходу логического элемента можно подключить несколько входов таких же элементов. Для выравнивания входных токов элементов — нагрузок в базовые цепи транзисторов включены резисторы. В ряду логических элементов рассматриваемого типа есть

277

такие, которые не содержат резисторов во входных сигнальных цепях. Их обычно называют логическими элементами с непосредственными связями.

Серии К11З и К115, микросхемы которых полностью совместимы по питанию, уровням напряжений логического 0 и логической 1, конструктивному оформлению, представляют собой единый комплекс микросхем, позволяющий оптимизировать устройства в от-

ношении |

их |

экономичности: для более быстродействующих узлов выбирать микросхемы |

|

серии КП5, для менее быстродействующих - микросхемы серии К11З.

Серия К11З состоит из 8 типов полупроводниковых микросхем: шести логических, RS-триггера и полусумматора. Микросхемы К1ЛБ133 и К1ЛВ134 содержат логические элементы с повышенной нагрузочной способностью (коэффициент разветвления по выходу равен 50, помехоустойчивость 0,8 В), что достигается усложнением их принципиальной схемы и увеличением потребляемой ими мощности до 7,2 мВт. Входной ток одного элемента 82÷150 мкА.

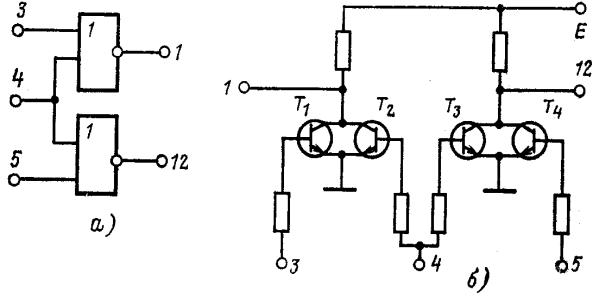

Серия К114 состоит из 11 типов полупроводниковых микросхем, каждая из которых выпускается в двух модификациях, различающихся средним временем задержки и потребляемой мощностью. В серии много микросхем, выполняющих логическую операцию НЕТ. Для примера на рис. 7.6 показан элемент, составляющий часть микросхемы К1ЛП141.

Рис. 7.6

При наличии на входе 4 сигнала с уровнем логической 1 операция инверсии (НЕ) с сигналами на входах 3 и 5 выполнена не будет. Запрет осуществляется благодаря тому,

278

что транзисторы Т2 и Т3 открыты и обеспечивают уровень логического нуля на выходах независимо от состояния транзисторов Т1 и Т4. Разряд регистра сдвига К1ИР141 представляет собой два последовательно соединѐнных одноступенчатых D-триггекра, управляемых двумя последовательно сдвинутых по времени синхронизирующих импульсов.

Серия К201 в отличнее от рассмотренных серий выполнена по гибридно-пленочной технологии. Серая имеет сравнительно ограниченный функциональный состав: 11 типов микросхем, среди них 7 микросхем содержат логические элементы НЕ, И-НЕ, одна микросхема И-ИЛИ и 3 микросхемы являются транзисторными сборками.

7.4.Серии микросхем диодно-транзисторнои логики

Кчислу серий микросхем типа ДТЛ относятся серии К104, К109, К121, КИ56, К194,

К202, К215, К217 и др..

Базовые элементы ДТЛ строятся на основе диодной логической схемы и транзисторного инвертора. В целом элемент такого вида выполняет операцию И-НЕ: для перевода элемента в состояние логического 0 на выходе необходимы сигналы логической 1 на всех входах.

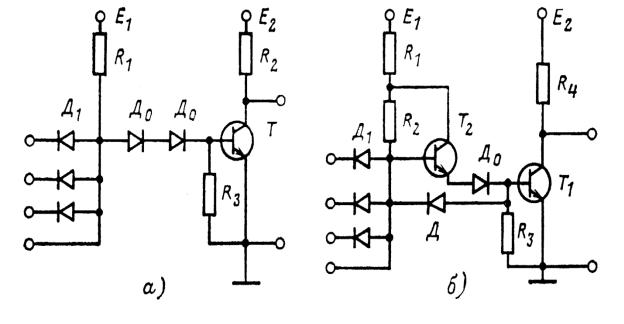

Число различных вариантов построения элементов ДТЛ велико, Мы ограничимся рассмотрением тех из них, которые получили наиболее широкое распространение. Элемент, схема которого представлена на рис. 7.7, а, является базовым для микросхем серии К217. Он содержит несколько входных диодов, которые вместе с резисторном R1 сложат для. выполнения логической операции И, и выходной инвертор.

279

Рис. 7.7

Два диода Д0 в цепи базы транзистора, часто называемых смещающими, предназначены для увеличения порога срабатывания элемента Нередко предусматривается возможность подключения ко входу дополнительной диодной сборки для расширения логических возможностей элемента по выполнению операции И.

Работает элемент следующим образом. При наличии хотя бы на одном входе сигнала логического 0 соответствующий диод открывается и ток от источника Е1 через резистор

R1 и открытый диод Д1 поступает в выходную цепь предыдущего элемента. При этом транзистор оказывается закрытым и на выходе элемента напряжение имеет высокий уровень, т. е. уровень логической 1.

Если на все входы поданы сигналы с уровнем логической 1, то входные диоды закры-

ваются и ток от источника Е1 поступает в базу транзистора. Он открывается и входит в режим насыщения, при этом выходное напряжение уменьшается до уровня логического 0.

Выключение транзистора осуществляется обратным током базы, протекающим через диоды Д0, представляющие собой некоторое время малое сопротивление обратному току, диод Д1 и выход открытого транзистора предыдущего элемента. Время восстановления диодов Д0 должно быть больше времени рассасывания накопленного в транзисторе заряда, в противном случае диоды Д0 закроются и процесс выключения транзистора существенно замедлится.

В базовом элементе для микросхем серий 109, 1121, 152, 156 и др, (рис. 7.7) вместо

одного из смещающих диодов используется транзистор Т 2 , который обеспечивает усиление тока, включающего выходной транзистор Т1. В результате использования до-

полнительного транзистора удается уменьшить напряжение Е1 до 5 В и снизить требования к усилению выходного транзистора, что способствует увеличению выхода годных схем при их изготовлении. Другой особенностью этого элемента является наличие диода между базой выходного транзистора и входными диодами. Этот диод, называемый ускоряющим, постоянно закрыт и играет роль конденсатора. Емкостью конденсатора является

емкость электронно-дырочного перехода, благодаря чему ускоряется включение выходного транзистора и его выключение, так как на этапе включения емкость способствует более быстрому пропусканию тока в базу транзистора, а на этапе выключения создаѐт дополнительный выключающий ток за счѐт накопленного ею заряда.

7.5.Серии микросхем транзисторно-транзисторной логики

Кчислу серий микросхем типа ТТЛ относятся серии К106, К180, К131, К133, К134,

К136, К155, К158, К199, К243.

280

Базовые элементы ТТЛ строятся по тому же принципу, что и элементы ДТЛ, но вместо диодной сборки применяется многоэмиттерный транзистор, называемый так потому, что у него в базе сформировано несколько (обычно от двух до восьми) эмиттерных областей. Обычно элементы ТТЛ имеют сложный инвертор.

Например, элемент на рис. 7.8 работает следующим образом. Когда на все входы мно-

гоэмиттерного транзистора Т1 поданы сигналы с высоким уровнем напряжения, все эмит-

терные переходы входного транзистора закрыты и ток от источника через резистор R1 и

открытый коллекторный переход транзистора Т1 поступает в базу транзистора Т2 и

открывает его до |

насыщения. Благодаря, падению напряжения на |

резисторе R3 |

|

|

открывается до насыщения транзистор Т4, обеспечивая низкий уровень выходно-

го напряжения. Транзистор Т3 в это время закрыт, поскольку напряжение на коллекторе

открытого транзистора Т2 мало. Диод Д служит для повышения порога отпирания

транзистора Т3.

При наличии хотя бы на одном входе сигнала с низким уровнем напряжения открывается соответствующий эмиттерный переход входного транзистора и ток от источника через резистор и открытый эмиттерный переход поступает в выходную цепь источника сиг-

нала, т. е. выходит из рассматриваемого элемента. Транзисторы Т2

транзистор Т3 открывается, обеспечивая высокий уровень напряжения на выходе.