Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОННИКИ (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ ТРИГГЕРОВ, РЕГИСТРОВ И СЧЕТЧИКОВ Отчет по лабораторной работе №3

по дисциплине «Электроника и схемотехника» Вариант №4

Студент гр. 712-2

___________ Л.С. Болтушкин

25.05.2024

Руководитель Старший преподаватель кафедры КИБЭВС

_______ __________ А.С. Семенов

25.05.2024

Томск 2024

Введение

Целью данной лабораторной работы является изучение навыков

совместного применения регистров и счетчиков

Задачи:

1.Составить таблицу истинности для всех 4-х функций и обозначить в таблице порядок разрядов (старший и младший). Порядок разрядов во всех таблицах должен совпадать (старший слева, младший – справа);

2.Для выполнения 4-х параллельных операций над полубайтом организовать прием и выдачу данных согласно варианту из таблицы. Собрать необходимую схему, используя встроенные блоки регистров (lpm_dff, lpm_shiftreg);

3.Промоделировать работу схем в двух режимах. Выбирать комбинации входных сигналов (A, B, C, D) таким образом, чтобы в результате каждая функция принимала значения на выходе и 0, и 1. Провести анализ результатов моделирования разных режимов;

4.Сверить результаты моделирования с составленными таблицами;

5.Повторить п. 2-4, только для описания устройств вместо схем на холстах .bdf, используя заданный вариантом HDL – VHDL.

2

|

|

|

|

|

|

1 Ход работы |

|

|

|

|

|

|

|||

|

|

|

|

|

1.1 Таблица истинности |

|

|

|

|

|

|||||

|

Вариант 2 – F2 = ∩ D; Вариант 3 – F3 = ∩ D; |

||||||||||||||

|

Вариант 4 – F4 = |

̅̅̅̅̅̅̅̅ |

|

|

|

|

|

|

|

̅̅̅̅̅̅̅̅ |

|||||

|

∩ D; Вариант 5 – F5 = |

∩ ∩ . |

|||||||||||||

|

В таблице 1.1 представлена таблица истинности для выбранных 4-х |

||||||||||||||

функций. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Таблица 1.1 – Таблица истинности для 4 первых функций. |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ст. |

|

|

|

|

Мл. |

|

|

|

|

|

F |

|

|

|

разряд |

|

|

|

|

разряд |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

B |

|

C |

|

D |

|

|

F2 |

F3 |

|

|

F4 |

|

F5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

0 |

|

|

0 |

0 |

|

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

1 |

|

|

1 |

0 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

|

0 |

|

|

0 |

0 |

|

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

0 |

|

|

0 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

0 |

|

|

1 |

1 |

|

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

|

0 |

|

|

1 |

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

|

0 |

|

|

1 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

|

0 |

|

|

1 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

|

0 |

|

|

1 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

|

1 |

1 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

1.2 Функциональная схема

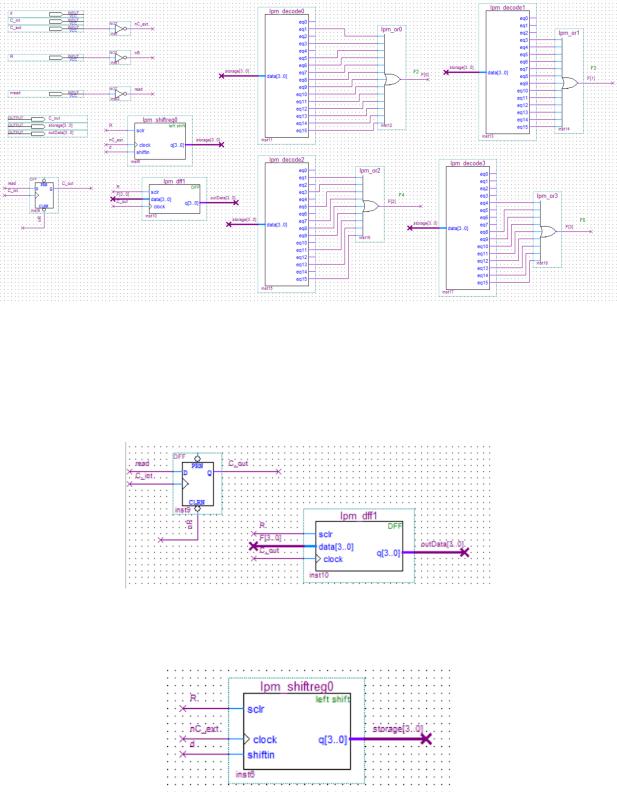

На рисунке 1.1 представлена общая функциональная схема с использованием встроенных блоков регистров и 4-х функций по вариантам.

Рисунок 1.1 – Общая bdf схема

На рисунках 1.2 – 1.3 представлены отдельно встроенные блоки регистров такие, как lpm dff и lpm_shiftreg, соответственно.

Рисунок 1.2 – lpm dff

Рисунок 1.3 – lpm_shiftreg 4

1.3 Моделирование

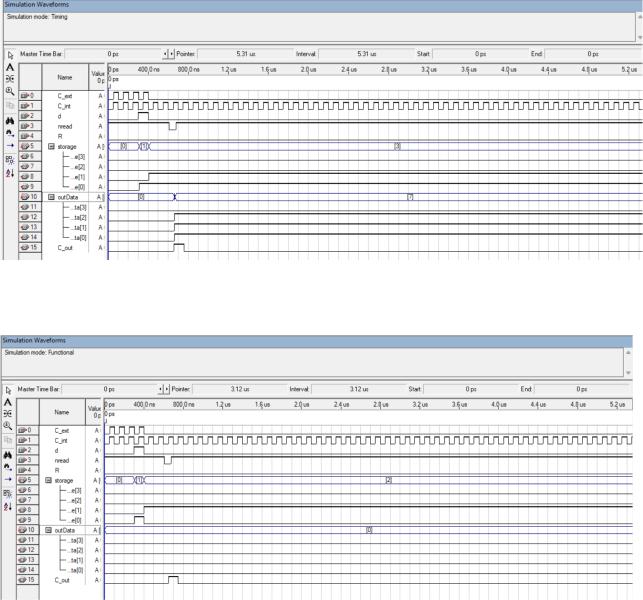

На рисунках 1.4 и 1.5 представлено моделирование схем в двух режимах.

Рисунок 1.4 – Моделирование в режиме Timing

Рисунок 1.5 – Моделирование в режиме Functional

К сожалению, результаты моделирования каждой схемы не соответствуют ее таблице истинности, где проблему не удалось найти.

Возможно данная проблема заключается не в правильном построении счетчиков, поскольку lpm_decode точно построены правильно и данные соответствуют данным из таблицы истинности для всех 4-х функций.

5

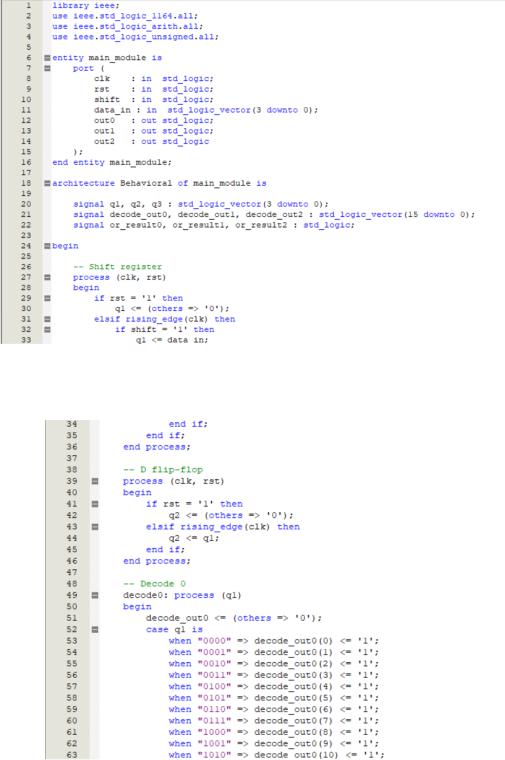

1.4Код на HDL

Спомощью VHDL были написан код, а также промоделированы те же устройства.

На рисунках 1.6 – 1.10 представлено описание устройства на VHDL.

Рисунок 1.6 – Код на VHDL, часть 1

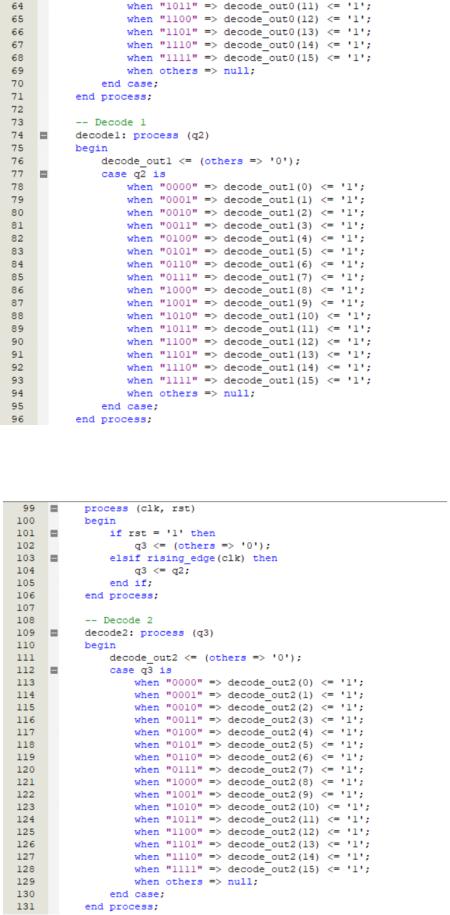

Рисунок 1.7 – Код на VHDL, часть 2

6

Рисунок 1.8 – Код на VDHL, часть 3

Рисунок 1.9 – Код на VHDL, часть 4

7

Рисунок 1.10 – Код на VHDL, часть 5

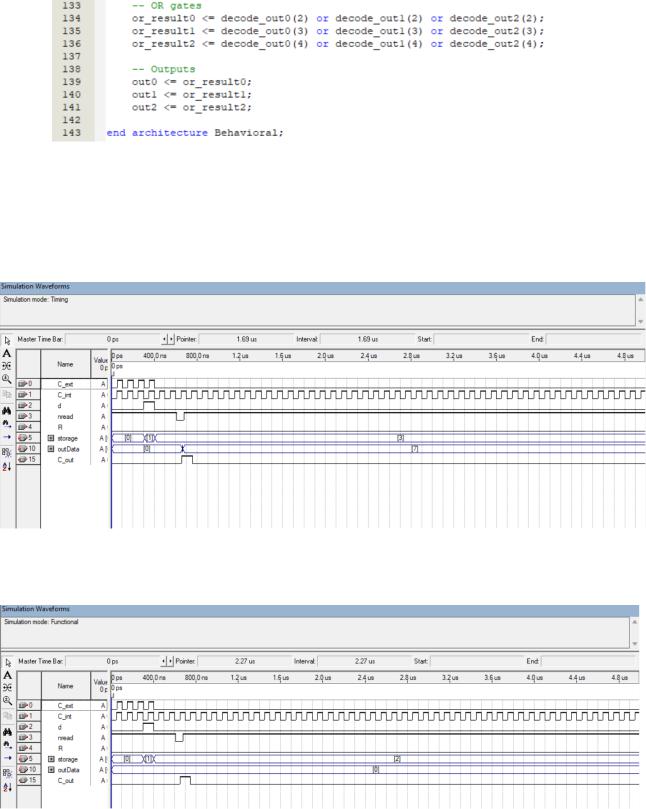

Моделирование по коду в двух режимах представлено на рисунках 1.11

и 1.12.

Рисунок 1.11 – Моделирование в режиме Timing

Рисунок 1.12 – Моделирование в режиме Functional

8

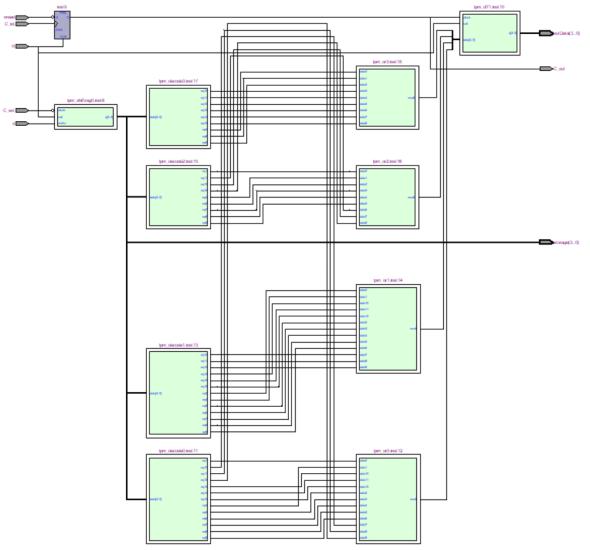

1.5 Схема из RTL Viewer

На рисунке 1.13 представлена схема RTL Viewer.

Рисунок 1.13 – RTL Viewer

9

Заключение

В ходе выполнения данной лабораторной работы были освоены навыки совместного использования регистров и счетчиков, составлены таблицы истинности для заданных устройств согласно варианту. Собраны схемы на холстах .bdf и промоделированы в двух режимах – Timing и Functional, а также написан код на VHDL.

10