- •«Санкт-петербургский государственный университет аэрокосмического приборостроения» (гуап)

- •Лабораторная работа №1

- •«Санкт-петербургский государственный университет аэрокосмического приборостроения» (гуап)

- •Лабораторная работа №2

- •«Санкт-петербургский государственный университет аэрокосмического приборостроения» (гуап)

- •Лабораторная работа №3

МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

федеральное государственное автономное образовательное учреждение высшего образования

«Санкт-петербургский государственный университет аэрокосмического приборостроения» (гуап)

КАФЕДРА ПРОБЛЕМНО-ОРИЕНТИРОВАННЫХ ВЫЧИСЛИТЕЛНЫХ КОМПЛЕКСОВ

Преподаватель

канд. техн. наук, доцент В. И. Исаков

Лабораторная работа №1

Освоение среды разработки цифровых систем Quartus II.

по дисциплине: Элементная база вычислительных систем и сетей

Отчет выполнил

студент гр.

Санкт-Петербург 2021

Цель работы:

Знакомство с особенностями работы приложения Quartus II 9.0 в процессе синтеза цифровых устройств на ПЛИС.

Ход работы:

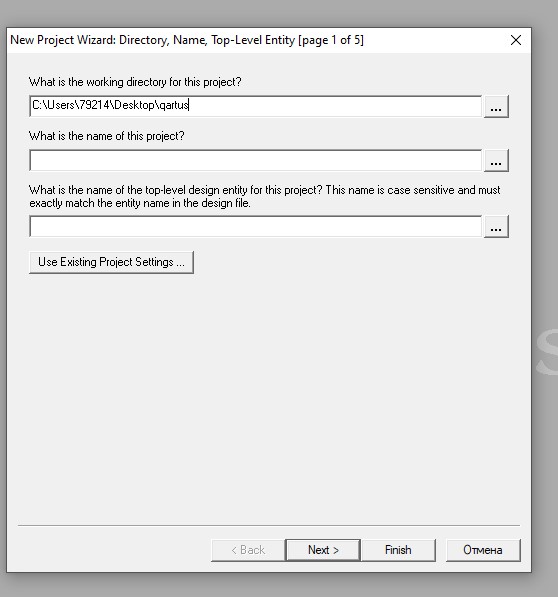

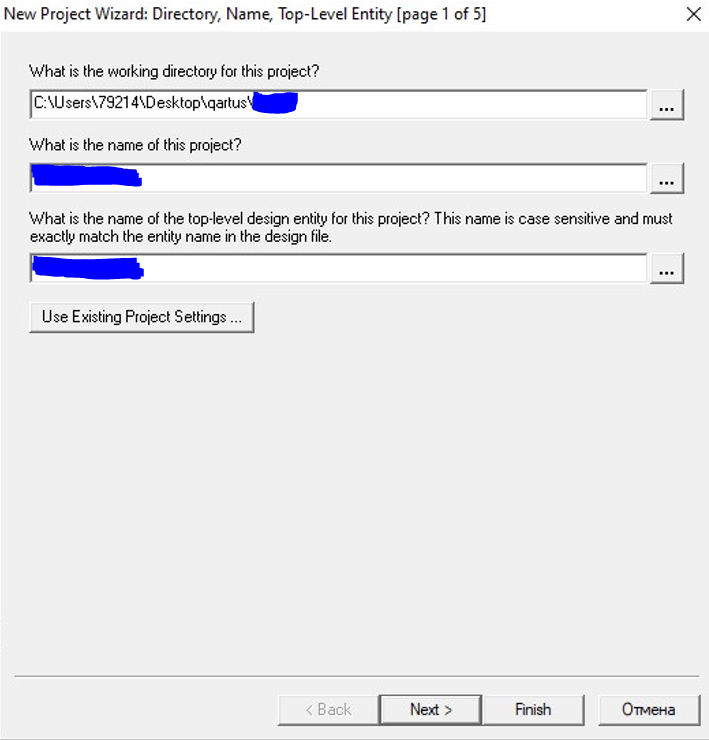

Создаем проект:

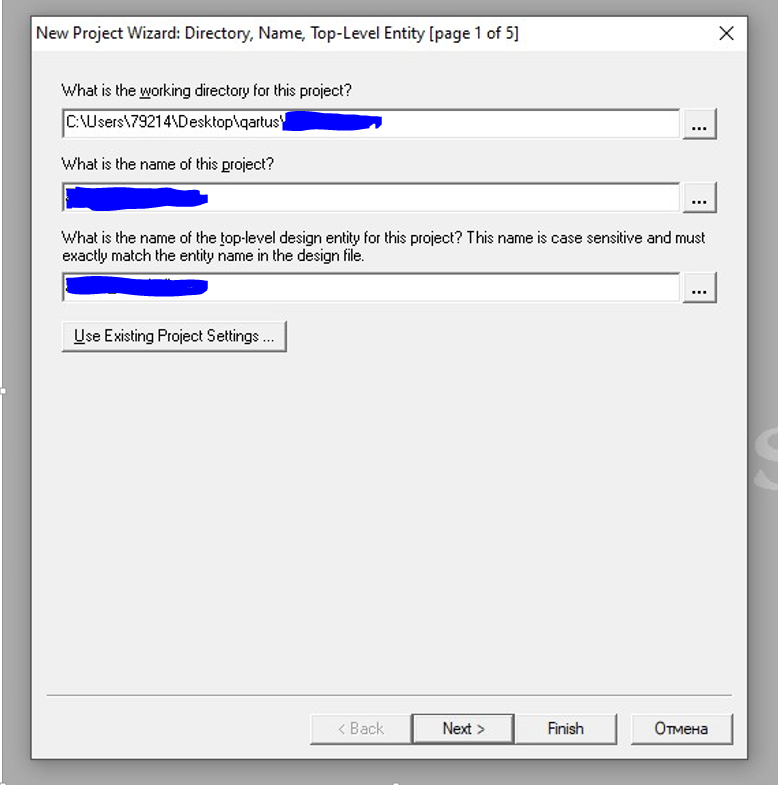

Присваиваем проекту название:

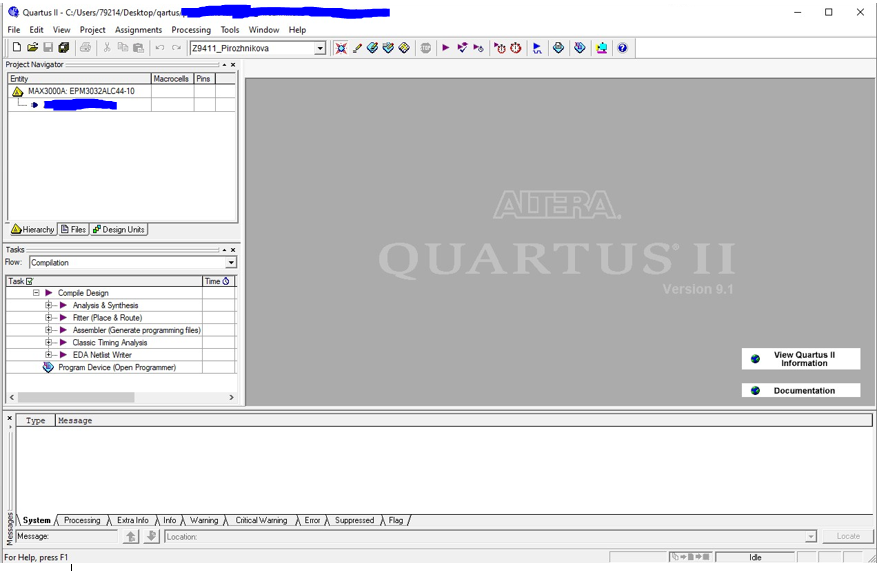

Открываем главное окно проекта:

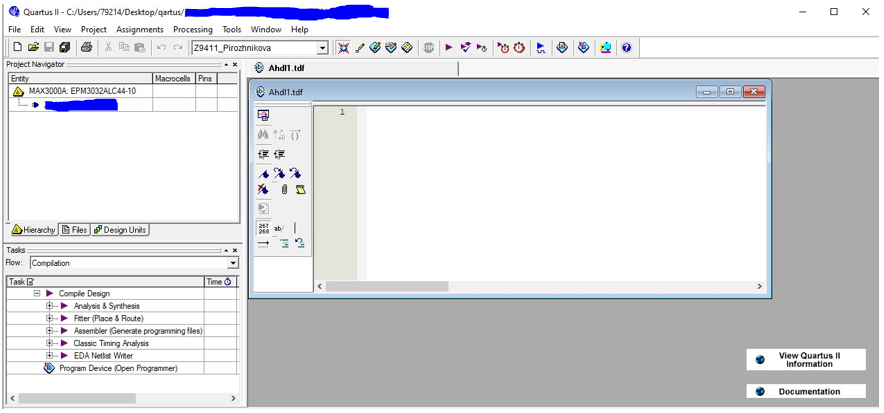

Создаём и сохраняем новый ADHL файл:

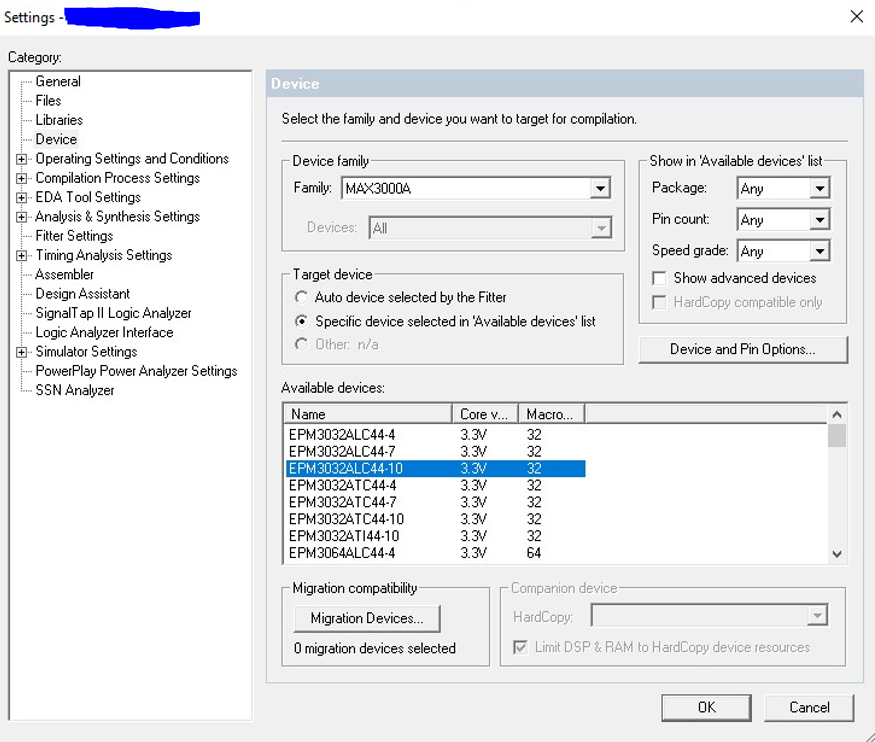

Выбираем микроконтроллер:

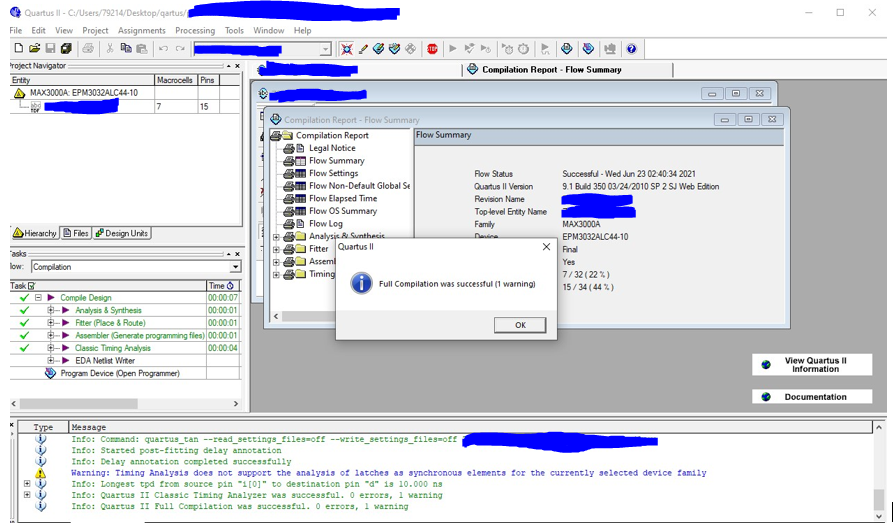

Скомпилируем проект:

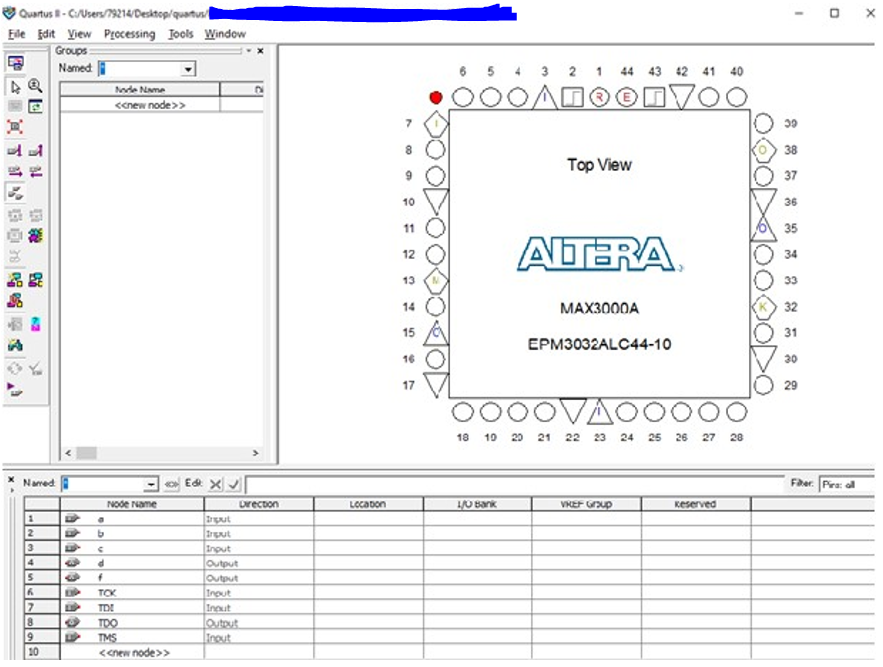

Проверим пины микроконтроллера:

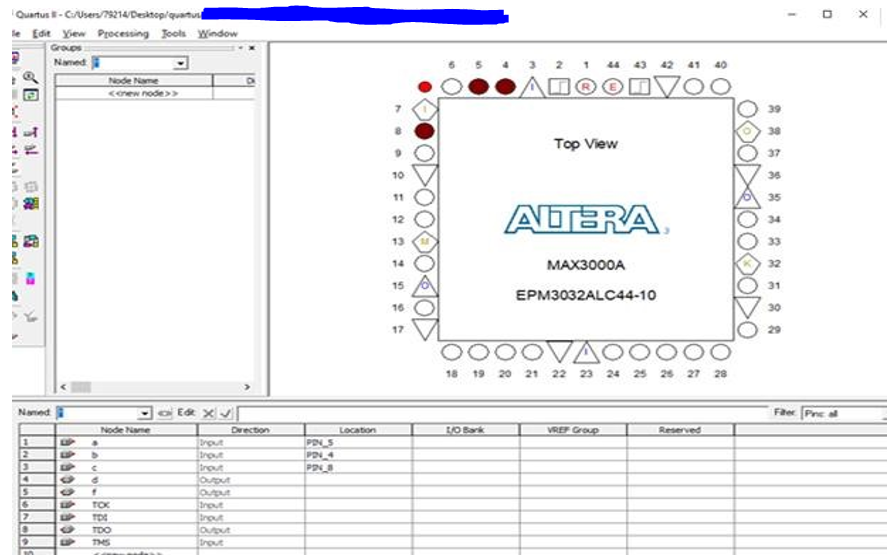

Присвоим входам и выходам микроконтроллера свои пины:

Создадим новый проект:

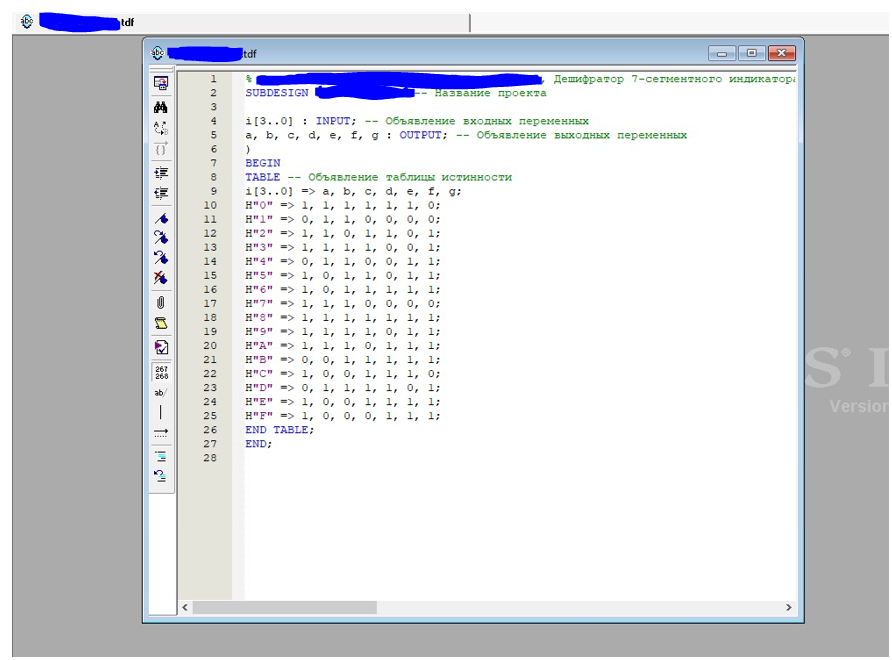

Перенесём и заполним листинг программы в ADHL файле:

Код программы:

% Фамилия Имя Отчество, гр. Z0000, Дешифратор 7-сегментного индикатора %

SUBDESIGN VashenazvanieAA-- Название проекта

i[3..0] : INPUT; -- Объявление входных переменных

a, b, c, d, e, f, g : OUTPUT; -- Объявление выходных переменных

)

BEGIN

TABLE -- Объявление таблицы истинности

i[3..0] => a, b, c, d, e, f, g; H"0" => 1, 1, 1, 1, 1, 1, 0;

H"1" => 0, 1, 1, 0, 0, 0, 0;

H"2" => 1, 1, 0, 1, 1, 0, 1;

H"3" => 1, 1, 1, 1, 0, 0, 1;

H"4" => 0, 1, 1, 0, 0, 1, 1;

H"5" => 1, 0, 1, 1, 0, 1, 1;

H"6" => 1, 0, 1, 1, 1, 1, 1;

H"7" => 1, 1, 1, 0, 0, 0, 0;

H"8" => 1, 1, 1, 1, 1, 1, 1;

H"9" => 1, 1, 1, 1, 0, 1, 1;

H"A" => 1, 1, 1, 0, 1, 1, 1;

H"B" => 0, 0, 1, 1, 1, 1, 1;

H"C" => 1, 0, 0, 1, 1, 1, 0;

H"D" => 0, 1, 1, 1, 1, 0, 1;

H"E" => 1, 0, 0, 1, 1, 1, 1;

H"F" => 1, 0, 0, 0, 1, 1, 1;

END TABLE;

END;

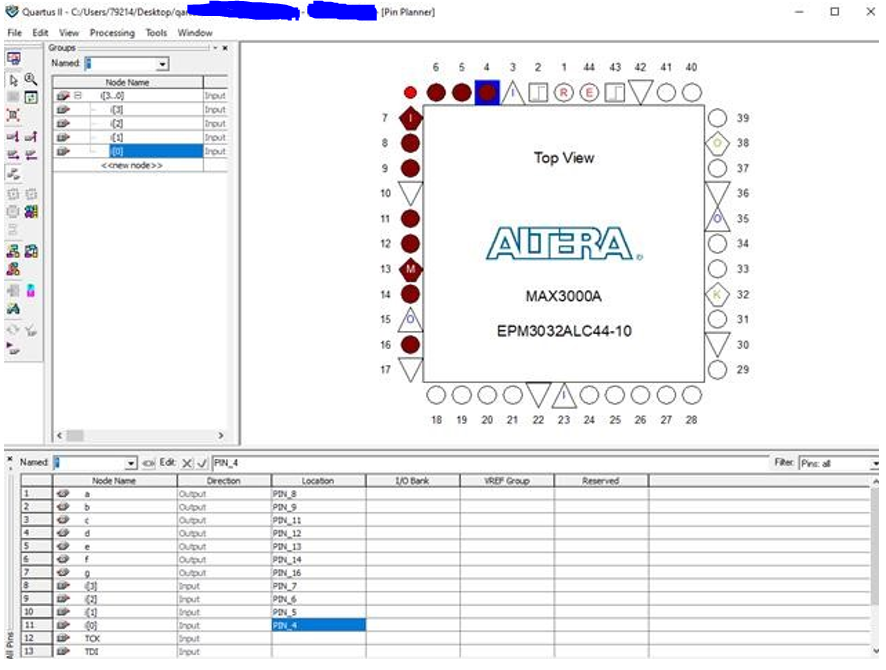

Определим пины микроконтроллера на входах и выходах:

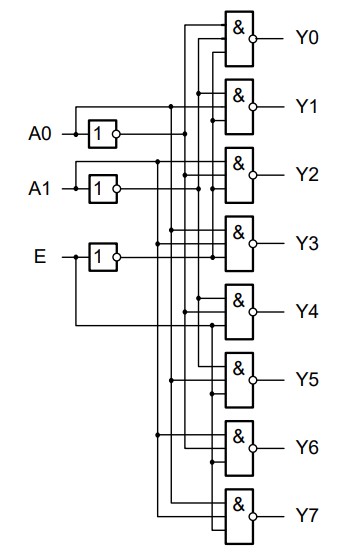

Логическая цепь дешифратора 3 на 8:

Таблица истинности дешифратора 3 на 8:

N=NOT

№ |

Е |

А1 |

А0 |

NA0 |

NA1 |

NE |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

|

|

NA0 & NA1 & NE |

NA1 & A0 & NE |

A1 & NA0 & NE |

A0 & A1 & NE |

NA1 & NA0 & E |

NA1 & A0 & E |

A1 & NA0 & E |

A0 & A1 & E |

||||

H"7" |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

H"6" |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

H"5" |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

H"4" |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

H"3" |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

H"2" |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

H"1" |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

H"0" |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

№ |

NY0 |

NY1 |

NY2 |

NY3 |

NY4 |

NY5 |

NY6 |

NY7 |

H"7" |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

H"6" |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

H"5" |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

H"4" |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

H"3" |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

H"2" |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

H"1" |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

H"0" |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

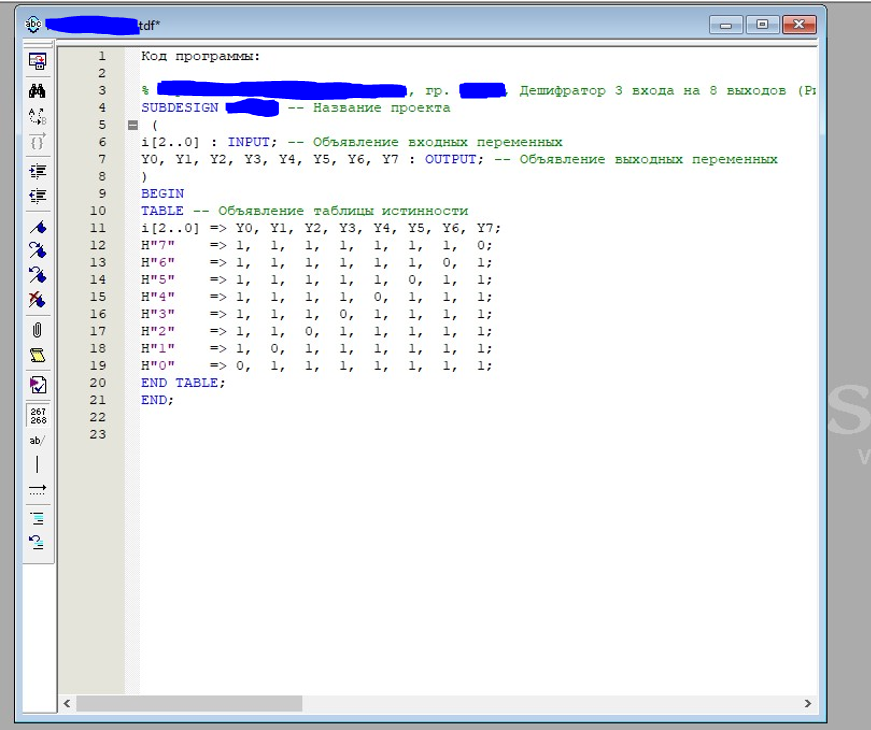

Код программы:

% Фамилия Имя Отчество, гр. Z0000, Дешифратор 3 входа на 8 выходов (Рис.

8а)%

SUBDESIGN Z94112 -- Название проекта

(

i[2..0] : INPUT; -- Объявление входных переменных

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7 : OUTPUT; -- Объявление выходных переменных

)

BEGIN

TABLE -- Объявление таблицы истинности i[2..0] => Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7;

H"7" => 1, 1, 1, 1, 1, 1, 1, 0;

H"6" => 1, 1, 1, 1, 1, 1, 0, 1;

H"5" => 1, 1, 1, 1, 1, 0, 1, 1;

H"4" => 1, 1, 1, 1, 0, 1, 1, 1;

H"3" => 1, 1, 1, 0, 1, 1, 1, 1;

H"2" => 1, 1, 0, 1, 1, 1, 1, 1;

H"1" => 1, 0, 1, 1, 1, 1, 1, 1;

H"0" => 0, 1, 1, 1, 1, 1, 1, 1;

END TABLE;

END;

Листинг программы:

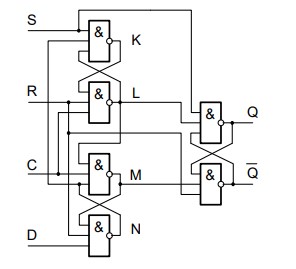

Логическая схема Д-триггера серии к155тм2:

Таблица истинности Д-триггера серии к155тм2:

|

Режим работы |

Вход |

|

|

|

Выход |

|

NS |

NR |

C |

D |

Q |

NQ |

||

I[0] |

I[1] |

I[2] |

I[3] |

||||

H"0" |

Асинхронная установка |

L |

H |

X |

X |

H |

L |

H"1" |

Асинхронный сброс |

H |

L |

X |

X |

L |

H |

H"2" |

Неопределённость |

L |

L |

X |

X |

H |

H |

H"3" |

Загрузка 1 (установка) |

H |

H |

|

H |

H |

L |

H"4" |

Загрузка 0 (сброс) |

H |

H |

|

L |

L |

H |

Код программы:

% Фамилия Имя Отчество, гр. Z0000, Дешифратор 3 входа на 8 выходов (Рис. 8а)%

SUBDESIGN VashenazvanieAA -- Название проекта

(

i[3..0] : INPUT; -- Объявление входных переменных Q, NQ : OUTPUT; -- Объявление выходных переменных

)

BEGIN

TABLE -- Объявление таблицы истинности i[3..0] => Q, NQ; H"0" => 1, 0;

H"1" => 0, 1;

H"2" => 1, 1;

H"3" => 1, 0;

H"4" => 0, 1;

END TABLE;

END;

МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

федеральное государственное автономное образовательное учреждение высшего образования