- •Сибирский государственный аэрокосмический

- •© Сибирский государственный аэрокосмический университет имени академика м. Ф. Решетнева, 2010

- •Оглавление

- •Введение

- •1. Основные параметры цифровых сигнальных процессоров

- •1.1 Классификация цифровых сигнальных процессоров по архитектуре

- •1.2 Программирование цифровых сигнальных процессоров

- •2. Основы цифровой обработки сигнальнов

- •2.1 Неймоновская и гарвардская архитектура обработки сигналов

- •Гарвардская архитектура

- •2.2 Основные характеристики tms320c10

- •2.3 Особенности проектирования цифровых сигнальных процессоров

- •3. Цифровые процессоры сигналов на основе троичных кодов

- •Библиографический список

- •Саханский Сергей Павлович

- •Цифровые процессоры сигналов

- •№ 24.04.953.П.000032.01.03. От 29.01.2003 г.

- •660014, Г. Красноярск, просп. Им. Газ. «Красноярский рабочий», 31.

2.3 Особенности проектирования цифровых сигнальных процессоров

Системы цифровой обработки сигналов, реализуемые на базе ЦПОС, относятся к классу цифровых микропроцессорных систем, функционирование которых помимо конфигурации аппаратных средств определяется также программным обеспечением. Эта особенность обуславливает следующую последовательность этапов проектирования подобных систем (рисунок 11).

Рисунок 11.

На первом этапе находится та или иная математическая модель цифровой обработки сигналов, позволяющая с заданной степенью точности удовлетворить технические требования к проектируемой системе. В качестве такой модели в общем случае выступает некоторый оператор F, связывающий однозначной функцией множество входных воздействий X и множество реакций Y. При этом компонентами множеств могут выступать как непосредственно цифровые последовательности, так и их образы. Следующим после нахождения оператора следует этап структурного синтеза алгоритма обработки. Специфика проектирования устройства на базе ЦПОС состоит в том, что его структура (состав отдельных компонентов и связь между ними) определяется, с одной стороны, применяемым элементным базисом, а с другой стороны, типом выполняемых процессором операций и числом используемых переменных, то есть алгоритмом обработки. Следовательно, этап структурного синтеза заключается в нахождении алгоритма (последовательности выполняемых процессором действий по вычислению реакции Y из входного действия X) исходя из заданного оператора F. Алгоритм характеризуется прежде всего его базисом, включающем совокупность множества переменных и множества выполняемых ЦПОС операций (действий). Для того, чтобы избежать применения нескольких ЦПОС, внешних ПЗУ и ОЗУ, в качестве критериев оптимальности процедуры проектирования можно использовать ограничения по производительности (для выбранного процессора), объемам ПЗУ и ОЗУ.

На этапе синтеза алгоритма могут быть использованы критерии синтеза, направленные на повышение быстродействия, сокращение числа используемой памяти и разрядности представления переменных. Конечной целью проектирования систем ЦОС для сигнального процессора является программа для ЦПОС. Второй этап разработки системы ЦОС – этап проектирования и изготовления ее аппаратных и программных средств. При проектировании аппаратных средств:

определяют требуемое число процессоров ЦОС, обеспечивающих требуемую производительность системы, и распределяют функции системы между ними;

рассчитывают объемы памяти для хранения массивов данных, исходя из требуемого их числа при выбранном периоде дискретизации;

определяют пропускную способность каждого канала ввода вывода, выбирают типы каналов ввода вывода;

разрабатывают протоколы обмена с внешней средой;

разрабатывают функциональную схему системы ЦОС, определяют конструктивные блоки и выполняют их схемотехническое и конструкторское проектирование.

На третьем и последнем этапе разработки системы ЦОС выполняют комплексную отладку аппаратных и программных средств системы ЦОС и ее испытания. Наиболее эффективными средством автоматизации процесса комплексной отладки являются внутрисхемные эмуляторы в комплексе с обычным измерительным оборудованием, характерным для цифровых систем.

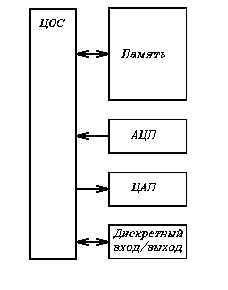

Структурная схема типичной системы обработки сигналов представлена на рисунке 12. Память необходима для хранения алгоритмов обработки и промежуточных результатов. ЦАП и АЦП преобразуют информацию, обрабатываемую ЦОС. Дискретный ввод и вывод служат для получения и выдачи дискретной информации. ЦОС (Цифровой Сигнальный Процессор) выполняет требуемую обработку. Аналоговые фильтры служат для устранения погрешностей квантования.

Рисунок 12.

Рассмотрим особенности каждого из узлов, входящих в аппаратную часть системы ЦОС, на примере ЦОС TMS32010, а также рассмотрим особенности, присущие и другим процессорам. Цифровой процессор TMS32010, рассмотренный ранее, содержит на кристалле следующие аппаратные средства: память данных; память команд; АЛУ; устройство умножения. Для реализации системы ЦОС на рассматриваемом процессоре необходимы дополнительные аппаратные средства, к числу которых относятся аналогово-цифровые и цифро-аналоговые преобразователи (АЦП, ЦАП), устройства внешней памяти и ввода вывода. Схема взаимодействия ЦОС с устройствами ЦАП/АЦП показана на рисунке 13 .

Рисунок 13.

Внутренняя память команд процессора TMC32010 имеет емкость 1.5К слов, а адресное пространство 4К слов. Когда внутренней памяти недостаточно, необходимо использовать внешнюю память, формируемую на нескольких внешних микросхемах. Выбор необходимой микросхемы производится с помощью специальной схемы. Для дешифрации микросхем памяти наиболее часто используют интегральные дешифраторы, на вход которых подаются старшие адресные выводы процессора. Для решения некоторых задач ЦОС может потребоваться память объемом более 4К слов. Поскольку ЦПОС имеет только 12 адресных линий, для использования памяти объемом более 4К слов необходима ее сегментация, при которой вся память делится на сегменты 4К слов. Сначала выбирается требуемый сегмент, а затем происходит обращение к ячейке внутри сегмента. Функциональная схема устройства, использующего внешнюю память емкостью 16Кх16бит, приведена на рисунке 14.

Рисунок 14.

Память устройства состоит из 4 микросхем памяти емкостью 8Кх8бит. Управление памятью производится с помощью регистра страницы и дешифратора страницы. Для задания страницы памяти необходимо записать номер страницы в регистр страницы. Регистр страницы располагается в адресном пространстве портов ввода вывода. Для дешифрации адреса порта может использоваться логический элемент И-НЕ или специальная схема дешифратора (рисунок 15). Временные диаграммы работы процессора с внешними устройствами представлены на рисунках 16, 17.

Рисунок 15.

Рисунок 16.

Рисунок 17.

Для устранения эффектов наложения спектр входного сигнала ограничивается полосой пропускания ФНЧ1, меньшей, чем половина частоты дискретизации АЦП. Аналоговый сигнал преобразуется в цифровой код, затем накапливается в Буфере 1, который необходим для согласования скоростей работы АЦП и ЦПОС. Временная диаграмма работа АЦП представлена на рисунке 18. В качестве примера на рисунке представлена временная диаграмма работы АЦП AD7892 Analog Devices. АЦП последовательного приближения, 12 разрядов, время преобразования порядка 2 мкс., имеет интерфейс для включения непосредственно на шину микропроцессора, данные представляются в дополнительном коде. Данное АЦП позволяет подключать его непосредственно на шину микропроцессора, но в нашем примере мы не будем использовать эту возможность.

Рисунок 18.

Для запуска преобразования необходимо подать сигнал CONVST низким уровнем – это можно сделать либо непосредственно программируемым выходом процессора, либо специализированным внешним устройством:

запуск осуществляется внешним таймером, настроенным на постоянный интервал времени;

запуск производится путем записи кодовой последовательности во внешний регистр;

запуск производится любым обращением в определенную область памяти.

Наличие собственного запускающего таймера характерен для законченных периферийных устройств (модулей аналогового ввода), они, как правило, поддерживают блочный обмен с ЦПОС. Модуль включает в себя таймер, определяющий период квантования, фильтр низких частот, контроллер управления обменом и буфер данных АЦП, который может хранить несколько отсчетов входных данных. Запуск путем записи кодовой последовательности во внешний регистр является оптимальным решением, когда количество АЦП более 2, а период квантования более 10мкс. При этом устройство запуска состоит из дешифратора адреса регистра управления и собственно регистра. Запуск обращением в определенную область памяти - частный случай запуска путем записи кодовой последовательности во внешний регистр. В этом случае устройство запуска состоит только из дешифратора адреса внешней ячейки памяти или регистра. Сигнал ЕОС оповещает о завершении цикла преобразования, с приходом этого сигнала данные готовы для считывания.

Для оповещения программы ЦОС о новых входных данных могут использоваться следующие способы:

через сигналы прерывания INT;

через сигналы ветвления по внешнему событию BIO;

через специальный внешний регистр флагов.

В случае использования сигнала INT после получения запроса на прерывание по входу INT процессор прерывает свою работу, текущее значение счетчика команд запоминается в стеке, а в счетчик команд загружается число 2 (процессор переходит к выполнению команды, расположенной по адресу 2). Подпрограмму обработки прерываний следует располагать с адреса 2. В случае наличия в системе только одного источника прерывания (например, АЦП) происходит его обработка (чтение данных из буфера АЦП). Если источников прерывания несколько, процессор переходит к подпрограмме обработки прерываний, которая выдает сигнал подтверждения прерывания. Поскольку в ЦПОС TMS32010 отсутствует специальный вывод подтверждения прерывания, для этого используется команда вывода во внешний порт, например, в порт номер 3 выводится нулевое значение. При этом на линии подтверждения прерывания, полученной с помощью дешифратора адреса портов, формируется высокий уровень. Сигнал подтверждения прерывания проходит последовательно через все внешние устройства, но поступает на вход Разрешение только того внешнего устройства, выход INT которого имеет активный уровень. Получив сигнал разрешения, внешнее устройство выставляет на выходе BIO низкий (активный) уровень, а на шину данных – свой код. Далее программа анализирует состояние выхода BIO. При появлении на нем сигнала низкого уровня с шины данных считывается код устройства, вызвавшего прерывание (рисунок 19).

Рисунок 19.

В том случае, если в системе имеется только одно АЦП, или все АЦП (любые устройства ввода) работают в синхронном режиме, возможно использование линии BIO для оповещения программы ЦОС. Тогда при выполнении команды BIOZ (ветвление при условии равенства 0 внешней линии BIO) в программе обработки осуществится переход по адресу, указанному в этой команде. Для нескольких несинхронных источников сигнала производится определение источника запроса ветвления по алгоритму, описанному ранее. В случае использования внешнего регистра для оповещения программы ЦОС о новых входных данных в программе предусматривается чтение внешнего регистра и проверка его содержимого. В том случае, если в нем находится код, характеризующий завершения преобразования, производится переход на подпрограмму считывания данных из АЦП. Последний способ является общим случаем ранее рассмотренного. Многоканальные устройства аналогового ввода могут быть построены либо с помощью аналоговых коммутаторов, устанавливаемых на вход АЦП после ФНЧ, при этом в расчете фильтра учитывается и период коммутации, либо использованием нескольких АЦП.

Как уже говорилось, устройства ЦАП служат для вывода аналоговой информации на внешние устройства. В этом разделе рассмотрим принципы построения устройств вывода аналоговой информации. В качестве примера рассмотрим отечественный ЦАП 594ПА1, имеющий 12 разрядов, время преобразования 3.5 мкс. Выбранный ЦАП имеет токовый выход и требует внешнего источника опорного напряжения. Система аналогового вывода состоит из Буфера 2 (рисунок 20), предназначенного для согласования скорости работы ЦАП и ЦПОС. Запись данных в буфер производится сигналом MEN. ФНЧ 2 производит фильтрацию выходного сигнала. Особенностью данного ЦАП является работа цифровых линий данных в прямом коде, поэтому программа вывода данных в ЦАП должна производить преобразование форматов данных. Многоканальные устройства аналогового вывода могут строится по схеме "один ЦАП, несколько УВХ (УВХ- устройства выборки хранения)", либо использованием нескольких ЦАП с одним опорным напряжением (рисунок 20).

Рисунок 20.

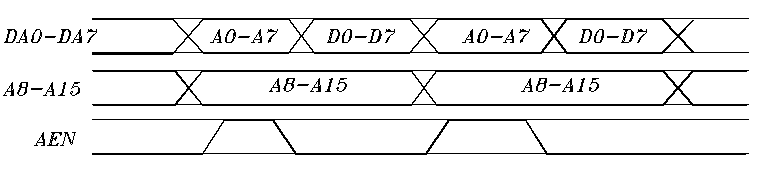

При проектировании особый интерес представляют интерфейсы ЦПС. Наиболее распространенной среди микроконтроллеров является мультиплексированная внешняя шина адреса и данных, данная особенность позволяет изготовителю микросхемы сэкономить на внешних выводах, а разработчика заставляет усложнить конструкцию при использовании внешней памяти. Мультиплексированная шина имеет два разделенных во времени цикла:

выдача адреса;

чтение или запись данных.

Временные диаграммы работы устройства, использующего мультиплексированную внешнюю шину, представлены на рисунке 21. Для различения циклов выдачи адреса и данных контроллеры имеют дополнительный управляющий сигнал AEN, говорящий о достоверности адреса.

Рисунок 21.

Структурная схема преобразования мультиплексированной шины к разделенным шинам адреса и данных приведена на рисунке 22.

Рисунок 22.