- •Обеспечение согласованности кэш-памяти микропроцессоров в мультипроцессорных системах

- •Программные механизмы обеспечения когерентности.

- •Аппаратные способы обеспечения когерентности.

- •Протоколы наблюдения.

- •Протокол mesi

- •Другие протоколы наблюдения сходные с mesi: msi, mosi, moesi, mesif.

- •Протоколы на основе справочника.

- •Литература.

Протокол mesi

Рассмотрим один из наиболее распространенных протоколов, обеспечивающих согласованную работу кэш-памяти нескольких микропроцессоров и основной памяти в мультипроцессорных системах, протокол MESI, который относится к группе протоколов наблюдения с аннулированием. Разберем его на примере системы, состоящей из микропроцессора МП 1 и прочих микропроцессоров {МП i}.

Этот протокол использует 4 признака состояния строки кэш-памяти микропроцессора, по первым буквам которых и называется протокол:

измененное состояние (Modified): информация, хранимая в кэш-памяти 1, достоверна только в этом кэше; она отсутствует в оперативной памяти и в кэш-памяти других микропроцессоров;

исключительная копия (Exclusive): информация, содержащаяся в кэше 1, содержится еще только в оперативной памяти;

разделяемая информация (Shared): информация, содержащаяся в кэше 1, содержится в кэш-памяти, по крайней мере, еще одного МП, а также в оперативной памяти;

недостоверная информация (Invalid): в строке кэш-памяти находится недостоверная информация.

Порядок перехода строки кэш-памяти из одного состояния в другое зависит от: текущего состояния строки, выполняемой операции (чтение или запись), результата обращения к строке (попадание или промах) и, наконец, от того является ли строка совместно используемой или нет. При работе МП 1 с точки зрения обеспечения когерентности памяти возможны следующие 7 ситуаций:

RH (Read Hit) – кэш-попадание при чтении;

WH (Write Hit) – кэш-попадание при записи;

RME (Read Miss Exclusive) – кэш-промах при чтении;

RMS (Read Miss Shared) – кэш-промах при чтении, но соответствующий блок есть в кэш-памяти другого микропроцессора;

WM (Write Miss) – кэш-промах при записи;

SHR (Snoop Hit Read) – обнаружение копии блока при прослушивании операции чтения другого кэша;

SHW (Snoop Hit Write) – обнаружение копии блока при прослушивании операции записи другого кэша.

Рис.1. Диаграмма MESI. |

Естественно, что в каждом состоянии есть одни ситуации, но нет других, т.е. нет состояний, из которых исходил бы все 7, стрелок. Например, в состоянии «I» не может быть кэш-попаданий, (то нет RH и WH), и не может быть обнаружена копия блока (то нет SHR и SHW), т.е. есть только ситуации кэш-промаха – RME, RMS и WM.

Аналогично, для состояний «S», «E» и «M» нет ситуаций кэш-промаха (RME, RMS и WM), но есть ситуации кэш-попаданий (RH и WH) и снупинга (SHR и SHW). Ниже приводятся иллюстрации для нескольких ситуаций.

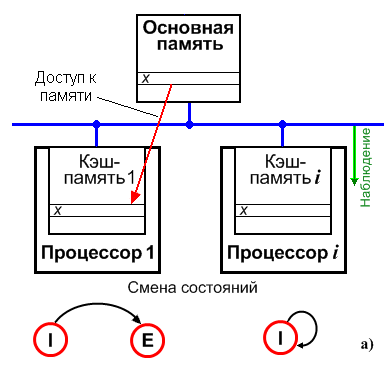

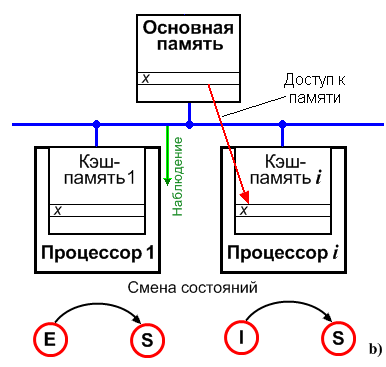

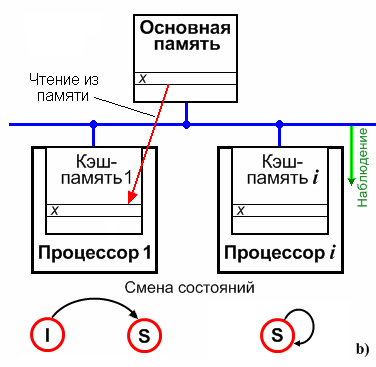

На рис.2a, чтение процессора 1 оказывается уникальным и создает ситуацию RME. На рис.2b, процессор i читает ту же строку x, для него создается ситуация RMS, а процессор 1 в результате наблюдения за шиной обнаруживает это и для него создается ситуация SHR. После того, кто бы не читал строку x, состояния S не изменятся.

Рис.2. Смена состояний в протоколе MESI при чтении: (a) для ПР1 ситуация RME, а для ПРi – ничего; (b) для ПРi ситуация RMS, а для ПР1 – SHR.

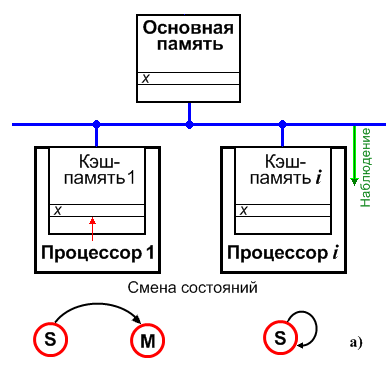

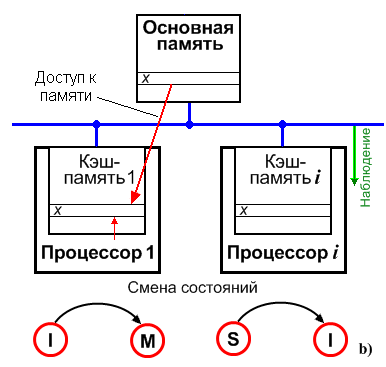

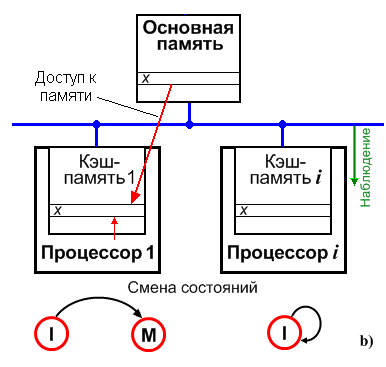

На рис.3а показана ситуация WH для процессора 1 без выхода на общую шину, таким образом ПР1 производит запись в строку кэша, меняет свое состояние, а остальные процессоры ничего не замечают. На рис.3b показана ситуация WH для ПР 1, но с выходом на общую шину, теперь все остальные процессоры замечают это и для них происходит ситуация SHW и они аннулируют свои копии.

Рис.3. Смена состояний в протоколе MESI при записи, для ПР1 ситуация WH: (a) без выхода на шину, остальные процессоры ничего не замечают; (b) с выходом на шину, тогда для остальных процессоров – ситуация SHW.

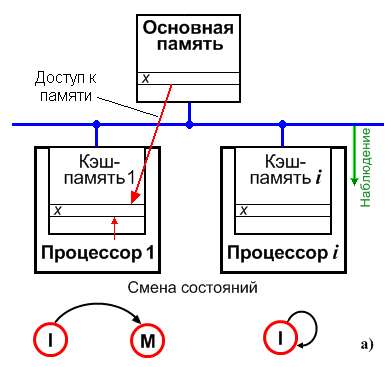

На рис.4 и рис.5 показана ситуация WM, т.е. ПР1 хочет записать данные в строку, которой нет в его кэше. Однако прежде чем записать данные в строку процессор должен считать эту строку в свой кэш и только потом модифицировать её. Но, прежде чем процессор сможет загрузить строку, он должен удостовериться, что в основной памяти действительно находится достоверная версия данных, то есть что в других кэшах отсутствует модифицированная копия данной строки.

Рис.4. Смена состояний в протоколе MESI при записи, для ПР1 ситуация WM: (a) нет копий в других процессорах; (b) есть копии они аннулируются – ситуация SHW.

Формируемая в данном случае последовательность операций носит название чтение с намерением модификации (Read With Intent To Modify – RWITM).

Если в кэшах других процессоров не было копий этой строки, то и доступ к основной памяти производится немедленно (рис.4a). Если же копия строки существовала в другом кэше и не имела состояния M (т.е. – E или S), то такая копия аннулируется, и доступ к основной памяти производится немедленно (рис.4b).

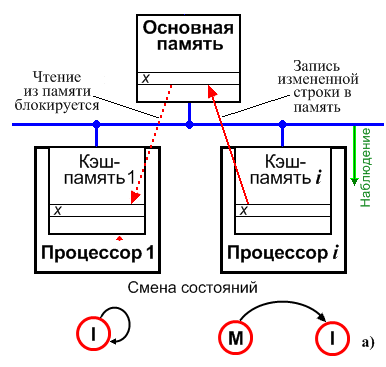

Если в одном из кэшей имеется копия нужной строки, находящаяся в состоянии M, то процессор, обладающий этой копией, прерывает RWITM-последовательность и переписывает строку в основную память, после чего меняет состояние строки в своем кэше на I (рис.5a). Если копия этой строки памяти была в каких-то других процессорах (кроме ПР1 и ПРi), то для них наступает ситуация SHW и все копии строки аннулируются. Затем RWITM-последовательность возобновляется и делается повторное обращение к основной памяти для считывания обновленной строки и строка изменяется в кэше ПР 1 (рис.5b).

Окончательным состоянием строки x в ПР 1 будет M, при этом ни в основной памяти, ни в других кэшах нет достоверной ее копии.

Рис.5. Этапы смены состояний в протоколе MESI при записи, для ПР1 ситуация WM, при условии, что в процессоре ПРi имеется копия нужной строки в состоянии M: (а) 1-й этап, чтение для ПР1блокируется, а ПРi выполняет запись строки в ОЗУ; (b) ПР1 выполняет чтение строки из ОЗУ и ее модификацию в своем кэше.

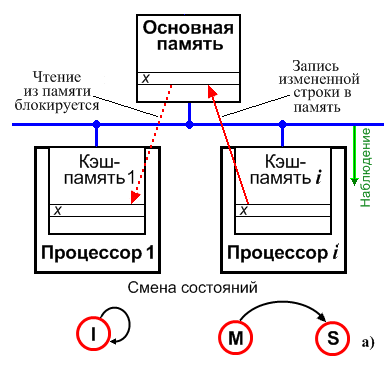

Обратите внимание, что если при кэш-промахе чтения процессором 1, оказалось, что соответствующий блок есть в кэш-памяти другого процессора ПРi, причем в состоянии М, то прежде чем ПР1 выполнит чтение, ПРi должен переписать модифицированную строку в основную память (рис.6a). При этом, ПРi переходит в состояние S, а все остальные процессоры, имеющие ту же строку, переходят в ситуацию SHW и сбрасываются в состояние I. На следующем этапе (рис.6.b), ПР1 спокойно читает строку из памяти и переходит в состояние S.

Рис.6. Этапы смены состояний в протоколе MESI при кэш-промахе чтения, но соответствующий блок есть в кэш-памяти другого микропроцессора, причем модифицированный: (a) 1-й этап, чтение для ПР1блокируется, а ПРi выполняет запись строки в ОЗУ; (b) ПР1 выполняет чтение строки из ОЗУ.