МУ ЛР Функциональные компоненты цифровых систем (1)

.pdf

Приложение 1

Таблица соответствия иностранных и отечественных микросхем

Условное изображение отечественной микросхе- |

Условное обозначение иностран- |

||

мы. |

|

|

ной микросхемы, аналогичной |

|

|

|

отечественной по выполняемым |

|

|

|

функциям |

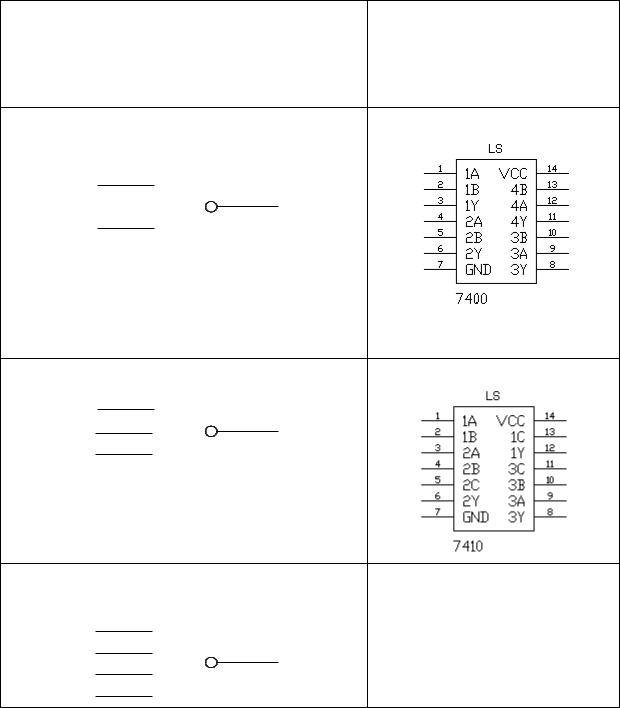

555ЛА3 – 4 элемента типа 2И-НЕ |

7400 – 74LS00 |

||

1,4,9,12 |

& |

|

|

|

ЛА3 |

3,6,8,11 |

|

|

|

|

|

2,5,10,13 |

|

|

|

555ЛА4 – 3 элемента типа 3И-НЕ |

7410 – 74LS10 |

||

1,3,9 |

& |

|

|

2,4,10 |

ЛА4 |

12,6,8 |

|

|

|

||

13,5,11 |

|

|

|

555ЛА1 – 2 элемента типа 4И-НЕ |

7420 – 74LS20 |

||

1,9 |

& |

|

|

2,10 |

|

||

ЛА1 |

6,8 |

||

4,12 |

|||

|

|||

|

|

||

5,13 |

|

|

|

71

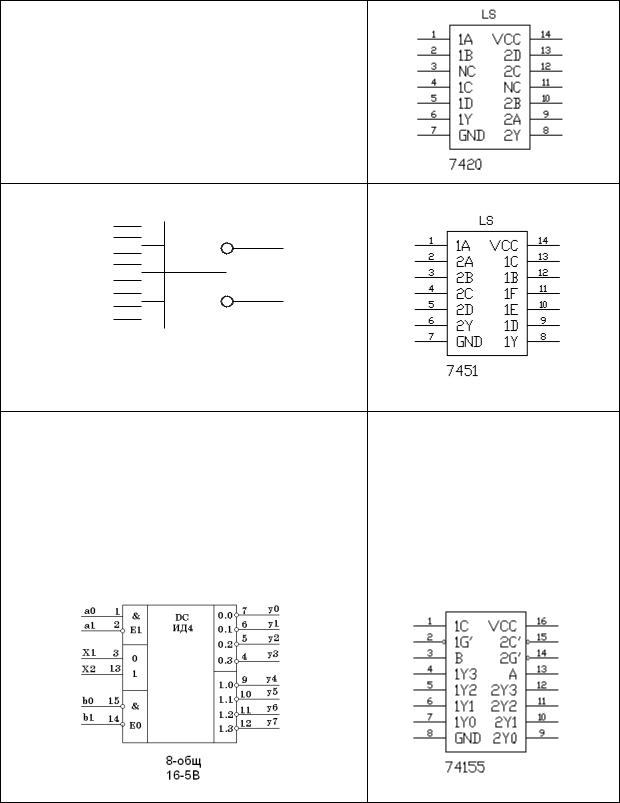

555ЛР1 (ЛР11) – 2 элемента типа 2-2И-ИЛИ-НЕ |

7451 – 74LS51 |

|||

2 |

& |

1 |

|

|

3 |

6 |

|

||

4 |

& |

ЛР11 |

|

|

5 |

|

|

|

|

|

|

|

|

|

1 |

& |

1 |

8 |

|

13 |

|

|||

|

ЛР11 |

|

||

9 |

|

|

|

|

& |

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

555ИД4 – два дешифратора типа 2-4 с общими |

74LS155 – спаренный дешифратор |

двумя адресными входами (контакты 13 и 3), с |

с общими адресными входами A и |

раздельными входами разрешения работы первого |

B, выходами первого (1Y0…1Y3) |

дешифратора (контакты 1 и 2) и второго (контак- |

и второго (2Y0…2Y3) дешифра- |

ты 14 и 15) и выходами первого дешифратора (0.0 |

тора и раздельными управляю- |

…0.3) и второго (1.0 …1.3) дешифратора. |

щими входами (1G, 1C и 2G, 2C) |

72

555КП2 – два мультиплексора типа 4-1 (4 входа |

74LS153 – два мультиплексора, |

информационных при одном выходе), у которых |

общие входы селекции которых |

общие входы селекции данных SED, раздельные |

обозначены буквами A и B, раз- |

управляющие (разрешающие работу) входы E0 и |

дельными разрешающими входа- |

E1. |

ми 1G и 2G. Информационные |

|

входы помечены символами |

|

(1C0…1C3) и (2C0…2C3), кото- |

|

рые соответствуют выходам 1Y и |

|

2Y. |

|

|

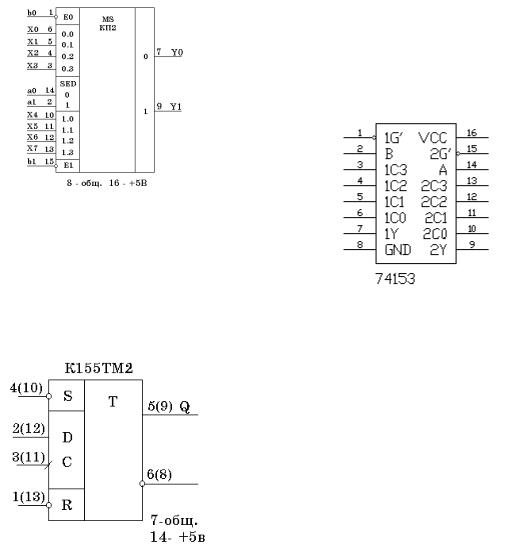

К155ТМ2 – два D-триггера с асинхронными уста- |

7474 – два D-триггера (1 и 2) с |

новочными входами. |

прямыми выходами (1Q и 2 Q) и |

|

инверсными выходами (1Q’ и 2 |

|

Q’), входами синхронизации |

|

(1CLK и 2CLK), информацион- |

|

ными входами (1D и 2D), асин- |

|

хронными входами сброса в ноль |

|

(1CLR’ и 2CLR’) и записи едини- |

|

цы (1PRE’ и 2PRE’). |

|

|

73

К155ТВ1 – JK-триггер с логикой на входах J и K и |

7472 – JK-триггер с логикой 3И |

асинхронными установочными входами R и S. |

на входах J (J1, J2, J3) и K (K1, |

|

K2, K3), входом синхронизации |

|

CLK и асинхронными установоч- |

|

ными входами R (CLR’) и S |

|

(PRE’). |

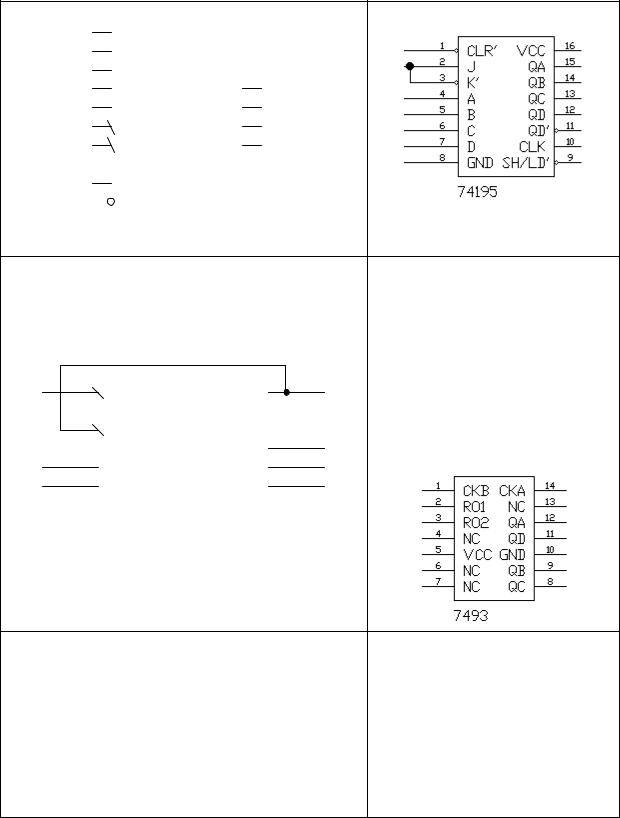

К155ИР1 – универсальный регистр, выполняющий |

74159 – универсальный регистр, |

две микрооперации: сдвиг на разряд при E=0 под |

выполняющий три микроопера- |

действием синхросигнала C> и параллельный при- |

ции. Под действием нуля на входе |

ём информации при E=1 под действием синхро- |

«CLR» осуществляется сброс в |

сигнала на входе CW. |

ноль, в зависимости от уровня |

|

сигнала на входе «SH/LD’» осу- |

|

ществляется по нарастающему |

|

фронту на входе «CLK» парал- |

|

лельный приём с входов A, B, C, |

|

D или сдвиг с приёмом информа- |

|

ции по соединённым вместе вхо- |

74

5 |

0 |

RG< |

|

|

4 |

|

|||

1 |

ИР1 |

|

||

3 |

|

|||

2 |

|

|

||

2 |

|

10 |

||

3 |

0 |

|||

1 |

11 |

|||

3> |

1 |

|||

8 |

12 |

|||

CWR |

2 |

|||

9 |

13 |

|||

C> |

3 |

|||

|

|

|||

6 |

EWR |

|

|

|

|

|

|

||

|

E> |

|

|

|

|

7 – общ., 14 - +5В |

|

||

К155ИЕ5 - сочетание T-триггера с входом +1T и трёхразрядного счётчика CT2 с входом +1CT. Сброс наблюдается при совпадении единиц на входах R.

14 |

+1T |

TCT2 |

T |

12 |

|

|

|||

01 |

|

ИЕ5 |

|

|

+1CT |

|

CT2 |

|

|

|

|

9 |

||

|

|

|

0 |

|

2 |

|

|

8 |

|

& |

|

1 |

||

3 |

|

11 |

||

R |

|

2 |

||

|

|

|

10 – общ., 05 - +5В

дам «J, K’».

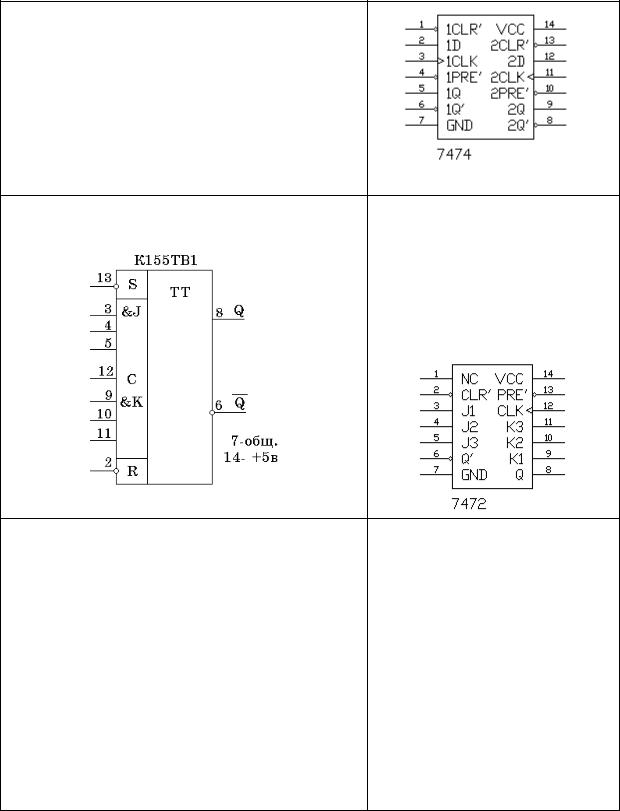

7493 – сочетание T-триггера с входом CKA и выходом A и трёхразрядного счётчика с входом CKB и выходами B, C, D. Сброс всех триггеров микросхемы происходит при одновременной подаче единичных уровней на входы

R01 и R02.

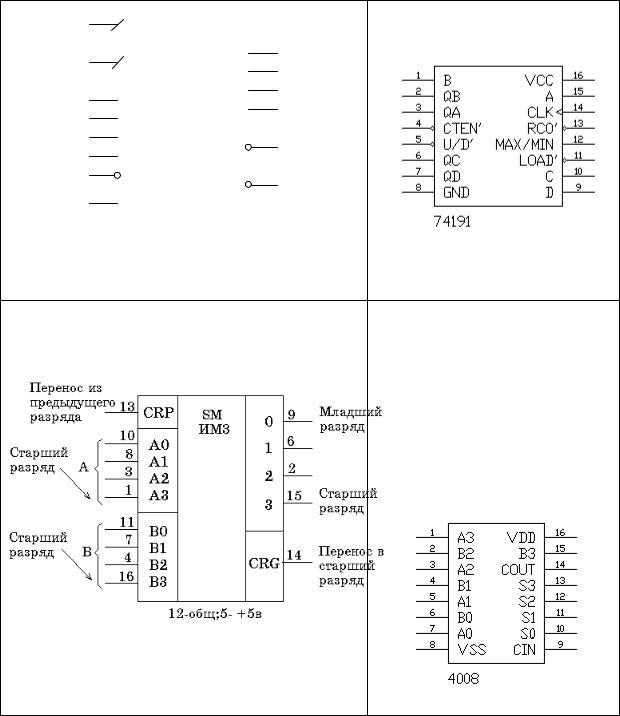

К155ИЕ7 – реверсивный счётчик с возможностью |

74191 – реверсивный двоичный |

параллельного занесения информации. |

счётчик с возможностью парал- |

|

лельного занесения информации |

|

по нулю на входе LOUD. Направ- |

|

ление счёта зависит от сигнала |

|

U/D’, вход переноса CTEN, выход |

|

переноса RCO. Счётным входом |

75

05 |

+1 |

CT2 |

|

|

|

|

|

||

04 |

E-1 |

ИЕ7 |

0 |

03 |

-1 |

|

02 |

||

|

|

|||

|

|

1 |

||

|

E+1 |

|

06 |

|

15 |

|

2 |

||

0 |

|

07 |

||

01 |

|

3 |

||

|

|

|||

1 |

|

|

||

10 |

|

|

|

|

2 |

|

|

12 |

|

09 |

|

CR |

||

3 |

|

|

||

11 |

|

|

|

|

C |

|

|

13 |

|

|

|

BR |

||

14 |

|

|

|

|

R |

|

|

|

|

|

|

|

|

08 – общ., 16 - +5В

К155ИМ3 – четырёхразрядный двоичный сумматор.

является вход синхронизации: CLK.

Микросхема 74192 аналогична К155ИЕ6 (десятичный счётчик)

4008 – четырёхразрядный двоичный сумматор.

S[3/0]=A[3/0]+B[3/0]+CIN, где

CIN – сигнал переноса в младший нулевой разряд. COUT – сигнал переноса в следующую микросхему сумматора, сигнал переполнения.

На отечественных микросхемах, содержащих несколько одинаковых элементов в одном корпусе, дано изображение одного элемента, но входы и выходы помечены номерами вы-

76

водов всех элементов. Для элемента 555ЛА3 входам 1 и 2 соответствует выход с номером 3, а входам 4 и 5 соответствует выход 6.

На условных обозначениях иностранных микросхем входы обозначены буквами A, B, C, D, …, а выходы буквами Y, Q, …. Цифры указывают на номер логического элемента или номер разряда. Вывод GND необходимо соединить с общим проводом (нулём), а на вывод Ucc надо подать напряжение +5Вольт. Для микросхемы 74LS00 первый элемент имеет два входа 1A и 1B, а выход этого элемента обозначен символом 1Y. Выполняемая элементом микросхемы функция при выводе условного обозначения на рабочий стол может быть определена таблицей истинности, которая выводится на экран нажатием клавиши F1 при отмеченном левой клавишей мышки изображении микросхемы. Если при моделировании возникнут проблемы, то выберите идеальные модели микросхем.

77

Приложение 2

Одноразрядный полный сумматор Рассмотрим задачу синтеза комбинационного одноразрядного двоично-

го сумматора, имеющего три эквивалентных входа: ai,bi,pi и два выхода: выход сигнала переноса в старший разряд pi+1 и выход суммы в данном разряде si (рис. 32,а).

Функционирование сумматора можно задать таблицей истинности (рис. 32,б).

a |

i |

SM |

|

|

|

|

||

|

|

|

|

|

||||

|

|

|

|

s |

|

|

||

|

|

|

|

|

S |

i |

|

|

b |

i |

|

|

|

|

|

||

|

|

|

p |

|

|

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i+1 |

|

|

p |

i |

|

|

CR |

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

ai |

|

bi |

|

pi |

|

pi+1 |

si |

|

0 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

|

0 |

|

1 |

|

0 |

1 |

|

0 |

|

1 |

|

0 |

|

0 |

1 |

|

0 |

|

1 |

|

1 |

|

1 |

0 |

|

1 |

|

0 |

|

0 |

|

0 |

1 |

|

1 |

|

0 |

|

1 |

|

1 |

0 |

|

1 |

|

1 |

|

0 |

|

1 |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

1 |

|

|

|

|

|

|

|

б) |

|

|

|

|

Рис. 32. Условное графическое обозначение одноразрядного сумматора |

||||||

(а), его |

|

таблица истинности (б) |

||||||

78

Для сигнала переноса pi+1 легко заполнить диаграмму Вейча и выполнить минимизацию

pi 1 aibi bi pi piai

Функция трех переменных si минимизации не подлежит. Но поскольку функция pi+1 легко реализуется, то, рассматривая si как функцию четырех переменных ai,bi,pi,pi+1, легко составить диаграмму Вейча для этой функции как частично заданной и, доопределив её, выполнить минимизацию функции:

si ai pi 1 bi pi 1 pi pi 1 aibi pi .

Можно исключить необходимость синтеза частично заданной функции для определения суммы si. Обратите внимание, что сумма на шести наборах значений входных переменных (от набора 001 до набора 110) равна инверсии переноса pi+1. Но на наборе 000 в этом случае необходимо обеспечить нулевое значение суммы, а на наборе 111 – обеспечить равенство суммы единице. Для обеспечения нуля достаточно использовать функцию ИЛИ для всех входных

переменных: ( ai |

bi |

pi ), а для формирования единицы следует использовать |

||||||

функцию |

И: |

|

( ai bi pi ). |

В |

результате |

сумма |

будет |

равна: |

si pi 1 (ai |

bi pi ) ai bi pi , что соответствует предложенному выше выраже- |

|||||||

нию. |

|

|

|

|

|

|

|

|

Реализовать полученные выражения можно с использованием элементов типа И-ИЛИ, а используя правила де Моргана сумматор можно реализовать на элементах типа И-НЕ.

79