ЛР4

.docМинистерство цифрового развития, связи и массовых коммуникаций российской федерации

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования

Московский технический университет связи и информатики

Кафедра многоканальных телекоммуникационных систем

ЛАБОРАТОРНАЯ РАБОТА

№ 4

по дисциплине

Цифровые системы передачи и методы их защиты

на тему

Реализация циклического сдвига 32-разрядных данных

Бригада № 5

Выполнил:

студент гр. БЗС2002

Ломакин А. А.

Проверила:

ст. пр. Зуйкова Т. Н.

Москва 2023

Индивидуальное задание

Запишите на языке ассемблер процессора ADSP-2181 фрагмент программы, содержащий запись в регистр SR шестнадцатеричного числа C0FFEE, а также команду, реализующую логический сдвиг содержимого регистра SR0 на 7 разрядов влево относительно регистра SR1. Ожидаемый результат выполнения команды представьте в двоичном и шестнадцатеричном виде для регистров SR1 и SR0.

Ответ: SR1 = 0x 00C0; SR0 = 0x FFEE; SR = LSHIFT SR0 by 7 (HI); SR1 = B# 1111 0111 0000 0000; SR0 = B# 0000 0000 0000 0000;

SR1 = 0x F700; SR0 = 0x 0000;

Запишите на языке ассемблер процессора ADSP-2181 фрагмент программы, содержащий запись в регистр SR шестнадцатеричного числа C0FEB0B, а также команду, реализующую логическую операцию «ИЛИ» содержимого регистра SR и регистра SR1, логически сдвинутого на 11 разрядов вправо относительно регистра SR0. Ожидаемый результат выполнения команды представьте в двоичном и шестнадцатеричном виде для регистров SR1 и SR0.

Ответ: SR1 = 0x 0C0F; SR0 = 0x EB0B; SR = SR OR LSHIFT SR1 by -11 (LO); SR1 = B# 0000 1100 0000 1111; SR0 = B# 1110 1011 0000 1011; SR1 = 0x 0C0F; SR0 = 0x EB0B;

Запишите заданные десятичные числа в двоичной и шестнадцатеричной системах счисления, используя префиксы 0x и B#, для 16-разрядного процессора.

520 = B# 0010 0000 1000 = 0x 208;

-267 = B# 1110 1111 0101 = 0x FEF5;

0.5 = B# B# 0100 0000 0000 0000 = 0x 4000;

-0.25 = B# 1010 0000 0000 0000= 0x A000;

1.0625 = B# 1000 1000 0000 0000 = 0x 8800.

1. Постановка задачи

Средствами сигнального процессора ADSP-2181 реализовать циклический сдвиг 32-разрядного начального вектора V.

2. Исходные данные

Исходные данные представлены в таблице 1.

Таблица 1 — Исходные данные (шестнадцатеричная запись)

№ ПК |

Старшая половина вектора V |

Младшая половина вектора V |

Количество разрядов и направление циклического сдвига |

5 |

C5CE |

9D6B |

на 7 разрядов влево |

3. Структурная схема сдвигателя

Сдвигатель – это функциональный блок, входящий в состав архитектуры 16- разрядного сигнального процессора ADSP-2181. Предназначен для поддержания функций арифметического и логического сдвигов 16-разрядных операндов в 32- разрядном поле с возможностью логического сложения с содержимым поля посредством операции логического «ИЛИ». Кроме того, сдвигатель позволяет преобразовать многоразрядный операнд в формат с плавающей запятой.

Структурная схема сдвигателя представлена на рисунке 1, где

SI – регистр операнд

SE – разрядный регистр

SR1 – старший регистр результата

SR0 – младший регистр результата

SR – объединенный регистр результата

R – шина результата

HI - позиция, по отношению к которой рассматривается сдвиг в SR1

LO - позиция, по отношению к которой рассматривается сдвиг в SR0

Рисунок 1 — Структура и система команд сдвигателя (нарисовать на бумаге)

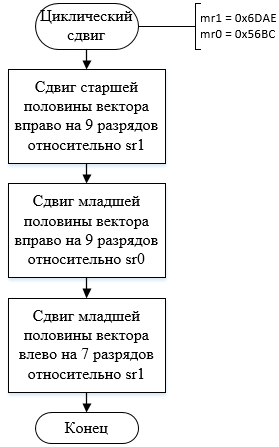

4. Блок-схема алгоритма

Блок-схема алгоритма, реализующего циклический сдвиг, представлена на рисунке 2.

Рисунок

2 — Блок-схема алгоритма

Рисунок

2 — Блок-схема алгоритма

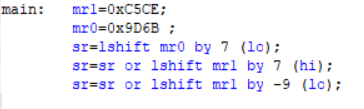

5. Исходный текст программы

Исходный текст программы, реализующей циклический сдвиг, представлен на рисунке 3.

Рисунок 3 — Исходный текст программы

6. Результаты отладки программы

Результаты отладки программы представлены в таблице 2.

Таблица 2 — Результаты отладки программы

РЕЗУЛЬТАТЫ |

Старшая половина вектора V |

Младшая половина вектора V |

|

Предварительный расчет (двоичная запись) |

До сдвига |

|

|

После сдвига |

|

|

|

Предварительный расчет (шестнадца-теричная запись) |

До сдвига |

|

|

После сдвига |

|

|

|

Результат выполнения программы (двоичная запись) |

До сдвига |

|

|

После сдвига |

|

|

|

Результат выполнения программы (шестнадцате-ричная запись) |

До сдвига |

|

|

После сдвига |

|

|

|

7. Результаты работы программы

Результаты работы программы представлены в таблице 3.

Таблица 3 — Результаты работы программы (двоичная запись)

Номер итерации |

Старшая половина вектора V |

Младшая половина вектора V |

Начальное значение |

|

|

1-я итерация |

|

|

2-я итерация |

|

|

3-я итерация |

|

|

8-я итерация |

|

|

16-я итерация |

|

|

32-я итерация |

|

|

8. Анализ полученных результатов и выводы

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

Контрольные вопросы для защиты

1. Какие функции в процессоре выполняет блок сдвигателя? Поясните примером.

2. Как формируется результат арифметического сдвига? Поясните примером.

3. Чем отличается логический сдвиг от арифметического сдвига? Поясните примером.

4. Перечислите все регистры, в которых могут находиться исходные 16-разрядные данные для операции сдвига?

5. Как определяется направление сдвига? Поясните примером.

6. Что обозначает запись (LO) в системе команд сдвигателя? Поясните примером.

7. Что обозначает запись (HI) в системе команд сдвигателя? Поясните примером.

8. С какой целью применяется в сдвигателе операция логическое «ИЛИ»? Поясните примером.

9. Каким образом в процессоре можно реализовать логический сдвиг 32-разрядных данных, если сдвигатель осуществляет сдвиг только 16-разрядных данных? Поясните примером.

10. Каким образом выделить 32 старших бита в 34-разрядном результате умножителя, сформированном при суммировании произведений? Поясните примером.

11. С какой целью в криптографии применяется операция циклического сдвига? Обоснуйте и поясните примером.

12. Каким образом можно реализовать в сдвигателе циклический сдвиг 32-разрядных данных на 25 битов вправо? Поясните примером.

Список литературы

1. Шаврин С.С., Мельник С.В. Цифровые системы передачи и методы их защиты [Электронный ресурс]: учебное пособие для бакалавров. - М.: ЭБС МТУСИ, 2020.- 91 с. Количество книг в библиотеке МТУСИ – 5. Режим доступа: https://lms.mtuci.ru/lms/local/mtt/elib_download.php?book_id=2375

2. Шаврин С.С. Реализация базовых операций защиты информации на сигнальных процессорах. Часть 2: Учебное пособие / МТУСИ. – М.: ЭБС МТУСИ, 2016. – 40 с. ЭБС МТУСИ. Количество книг в библиотеке МТУСИ – 99. Режим доступа: https://lms.mtuci.ru/lms/local/mtt/elib_download.php?book_id=1399