Министерство науки и высшего образования Российской Федерации

Федеральное государственное автономное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №4

по дисциплине «Электроника и схемотехника 2»

Вариант №11

Выполнил:

Студент гр. 712-1

21.06.2024

Руководитель

Старший преподаватель кафедры КИБЭВС

________ Семенов А.С.

15.06.2024

Томск 2024

Введение

Цель лабораторной работы: научиться совместно применять устройства средней степени интеграции.

Постановка задачи:

Разработать структурную схему устройства.

Описать составные части схемы.

Составить таблицы функционирования операционного блока.

Составить план моделирования в виде двух столбцов таблицы: входные данные (код операции, данные), выходные данные (ожидаемый результат). Использовать для каждой операции по два различных набора данных. Выбирать данные таким образом, чтобы результат операции не был зеркальным и отличался при разном направлении его передачи (MSB, LSB).

Организовать приём и выдачу данных согласно варианту из таблицы для выполнения 4-х операций, используя встроенные блоки регистров, счётчиков и мультиплексоров.

Создать схему реализации вычислительного блока, выполняющего заданные операции и осуществляющего приём входных данных и выдачу результата согласно варианту в таблице.

Промоделировать работу схемы в двух режимах. Провести анализ результатов моделирования разных режимов.

Повторить п. 5-7, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL. Для вариантов приёма или выдачи данных последовательным кодом использовать конечный автомат для организации приёма данных нефиксированной структуры или выдачи данных и генерации синхроимпульсов C_out.

Задание по варианту:

Приём: последовательным кодом старшими разрядами вперед, синхронизация убывающим фронтом, синхронный сброс устройств.

Выдача: параллельным кодом, синхронизация нарастающим фронтом, активный уровень "read" равен 1

Операция 01: разработать схему декодирования IBM GCR-кода в двоичное число. При несовпадении входного символа с таблицей установить выход FB=1.

Операция 10 (OP1):

.

.Операция 11 (OP2): A + B + 1.

HDL: VHDL.

Описание схемы устройства

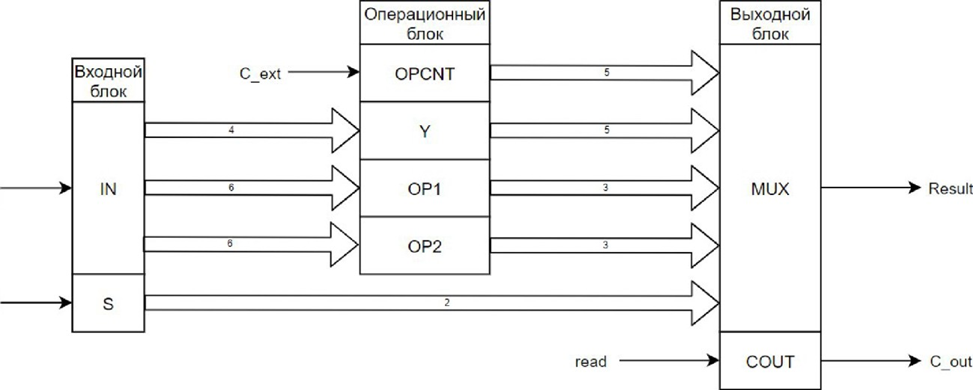

На рисунке 1.1 представлена обобщенная функциональная схема устройства, которое необходимо реализовать.

Рисунок 1.1 – Обобщенная функциональная схема

Устройство получает на вход 6-разрядный код x, выполняет четыре операции и выводит результат одной из них по линии result в зависимости от кода операции S.

При подаче активного уровня сигнала read вырабатываются сигналы C_out, количество которых зависит от длины result.

Обозначения в схеме:

IN - хранение входных данных;

S - хранение кода операции;

OPCNT - счётчик операций;

Y - кодирование двоичного числа;

OP1 - логическая операция;

OP2 - арифметическая операция;

MUX - мультиплексирование выходных данных;

COUT - выработка выходного синхросигнала.

Разработка вычислительного блока

Вычислительный блок представляет собой несколько последовательных операций над входными данными. Для каждой операции была построена отдельная таблица функционирования.

В таблице 2.1 представлена таблица декодирования IBM GCR-кода в двоичное число.

Таблица 2.1 - Таблица функционирования IBM GCR-кода

Код операции |

Входы |

Выходы |

||||||||||||||||

x4 |

x3 |

x2 |

x1 |

x0 |

ST2 |

ST1 |

SP2 |

SP1 |

FB |

|||||||||

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|||||||

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|||||||

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|||||||

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|||||||

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|||||||

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|||||||

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|||||||

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|||||||

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

|||||||

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

|||||||

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|||||||

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|||||||

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|||||||

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|||||||

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|||||||

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|||||||

В

таблице 2.2 представлена таблица истинности

Таблица 2.2 - Таблица истинности логической операции

Код операции |

Входы |

|

Выходы |

|||||||||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP1.2 |

OP1.1 |

OP1.0 |

||||

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

||

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

||

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

||

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

||

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

||

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

||

Продолжение таблицы 2.2

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

Продолжение таблицы 2.2

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

В

таблице 2.3 представлена таблица истинности

арифметической операции

.

.

Таблица 2.3 - Таблица истинности арифметической операции

Код операции |

Входы |

Выходы |

|||||||||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP2.3 |

OP2.2 |

OP2.1 |

OP2.0 |

||

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

Продолжение таблицы 2.3

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

Продолжение таблицы 2.3

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

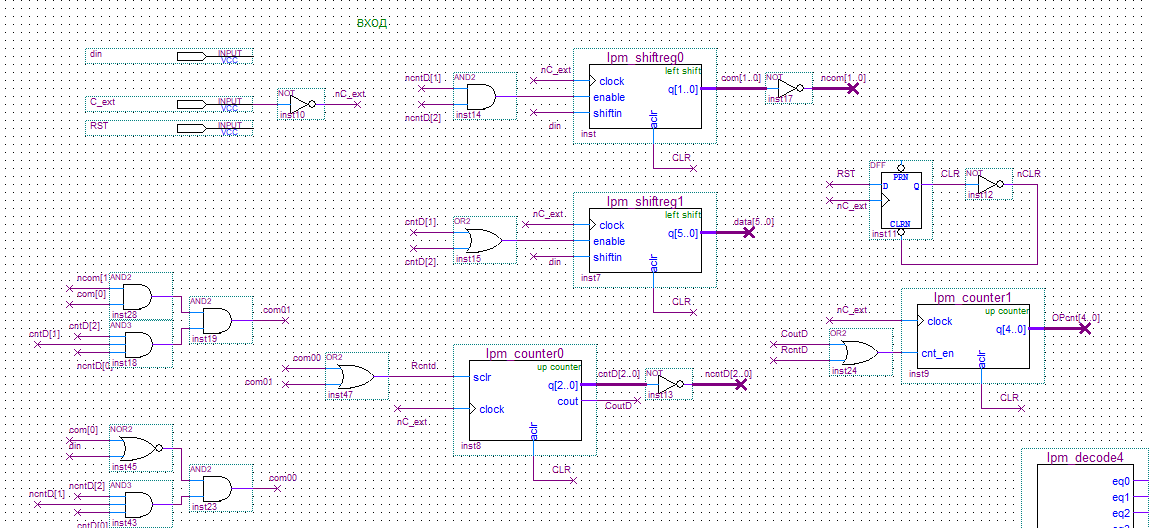

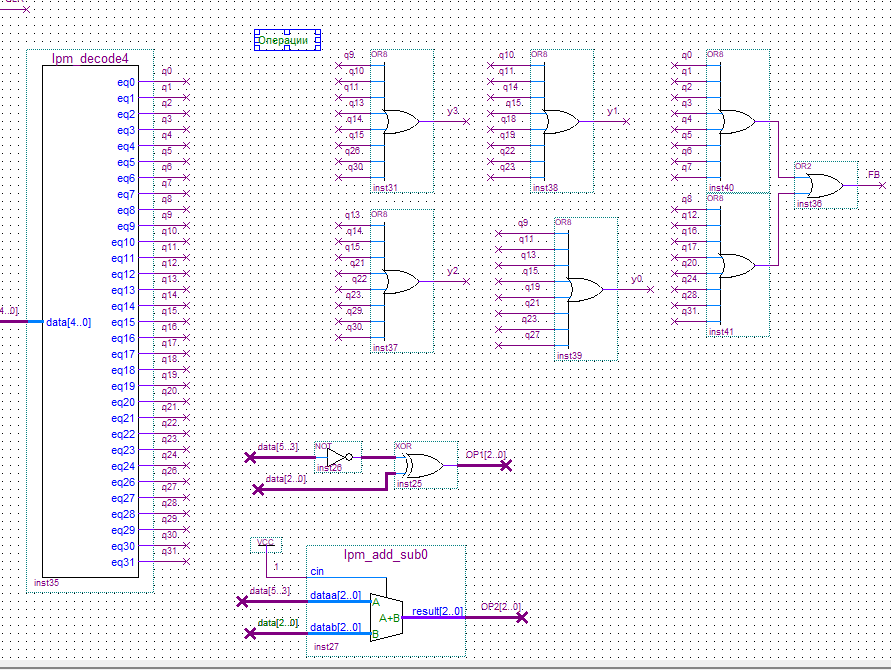

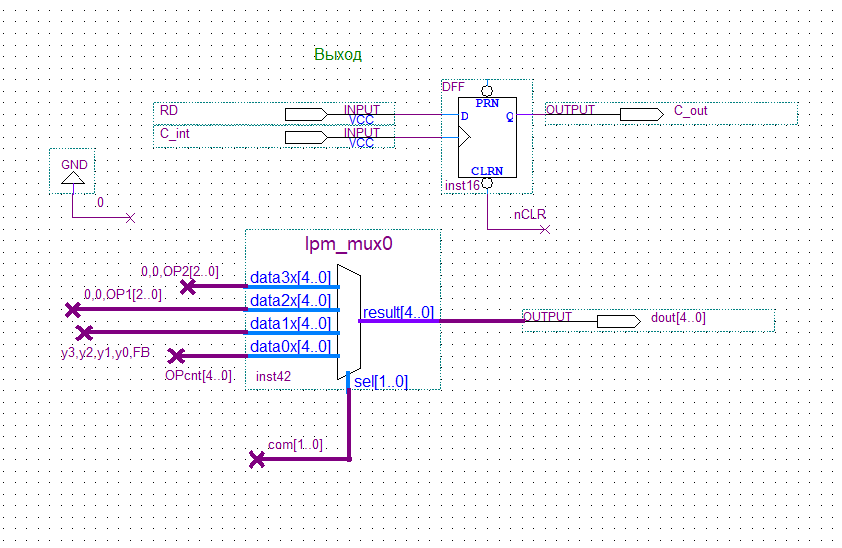

Для выполнения данных операций была построена схема в САПР Quartus II.

Рисунок 2.1 – Входной блок схемы

Рисунок 2.2 – Операционный блок схемы

Рисунок 2.3 – Выходной блок схемы

План моделирования схемы представлен в таблице 2.4.

Таблица 2.4 - План моделирования схемы

Входы |

Выходы |

||||||||||||||||||||||

cmd1 |

cmd0 |

A |

B |

X |

C |

||||||||||||||||||

X |

x4 |

x3 |

x2 |

x1 |

x0 |

y3 |

y2 |

y1 |

y0 |

FB |

|||||||||||||

0 |

1 |

- |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|||||||||||

0 |

1 |

- |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|||||||||||

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|||||||||||

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|||||||||||

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|||||||||||

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|||||||||||

0 |

0 |

- |

- |

- |

- |

- |

- |

0 |

0 |

1 |

1 |

1 |

|||||||||||

Сброс |

- |

- |

- |

- |

- |

- |

0 |

0 |

0 |

0 |

0 |

||||||||||||

0 |

0 |

- |

- |

- |

- |

- |

- |

0 |

0 |

0 |

0 |

1 |

|||||||||||

На рисунках 2.4 – 2.7 представлено моделирование схемы в двух режимах согласно созданному плану.

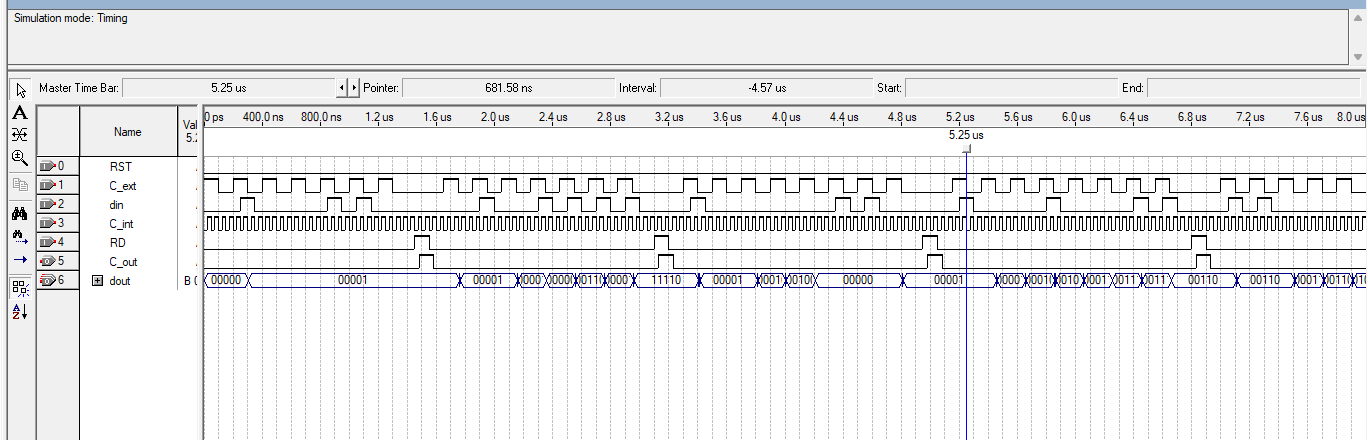

Рисунок 2.4 – Первая часть моделирования в режиме Timing

Рисунок 2.5– Вторая часть моделирования в режиме Timing

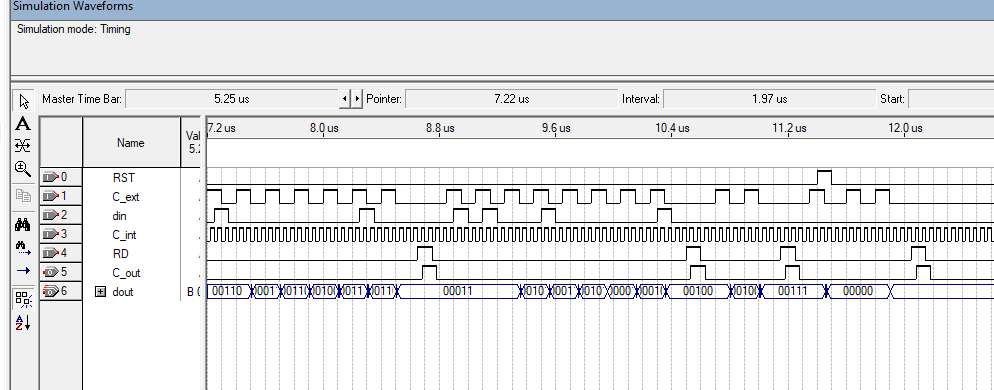

Рисунок 2.6 – Первая часть моделирования в режиме Functional

Рисунок 2.7 – Вторая часть моделирования в режиме Functional

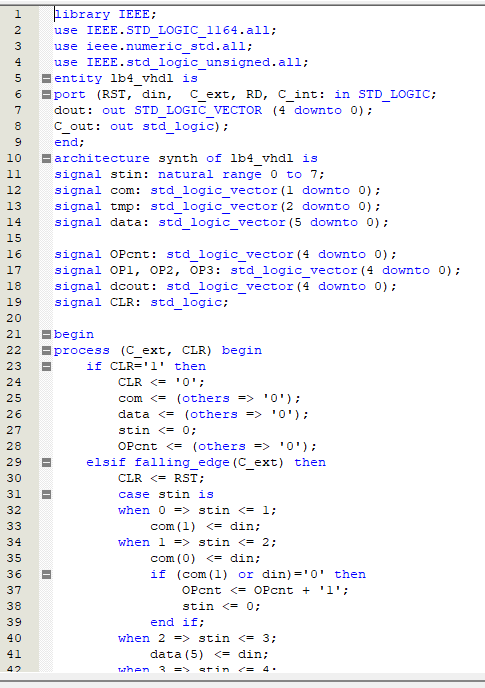

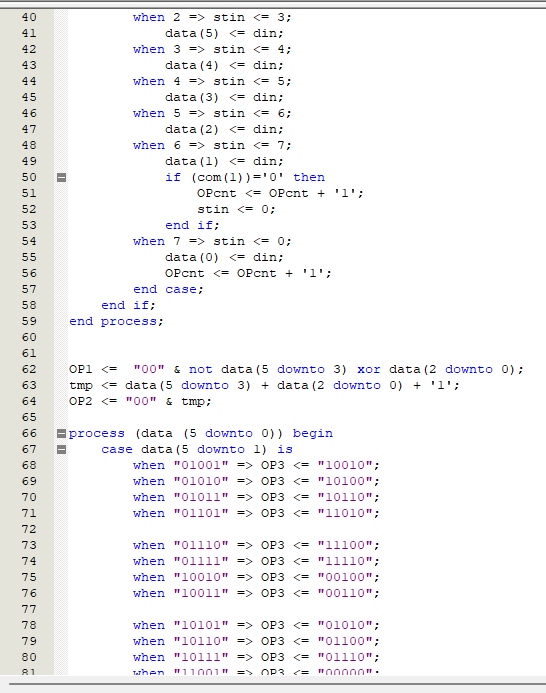

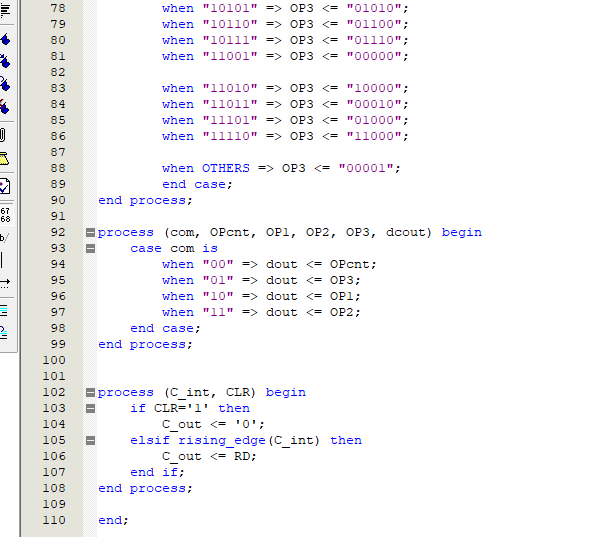

Далее схема была описана на языке описания аппаратуры (HDL) VHDL. Результат представлен на рисунках 2.8 – 2.11.

Рисунок 2.8 – Описание схемы на VHDL

Рисунок 2.9 – Продолжение описания схемы на VHDL

Рисунок 2.10 – Продолжение описания схемы на VHDL

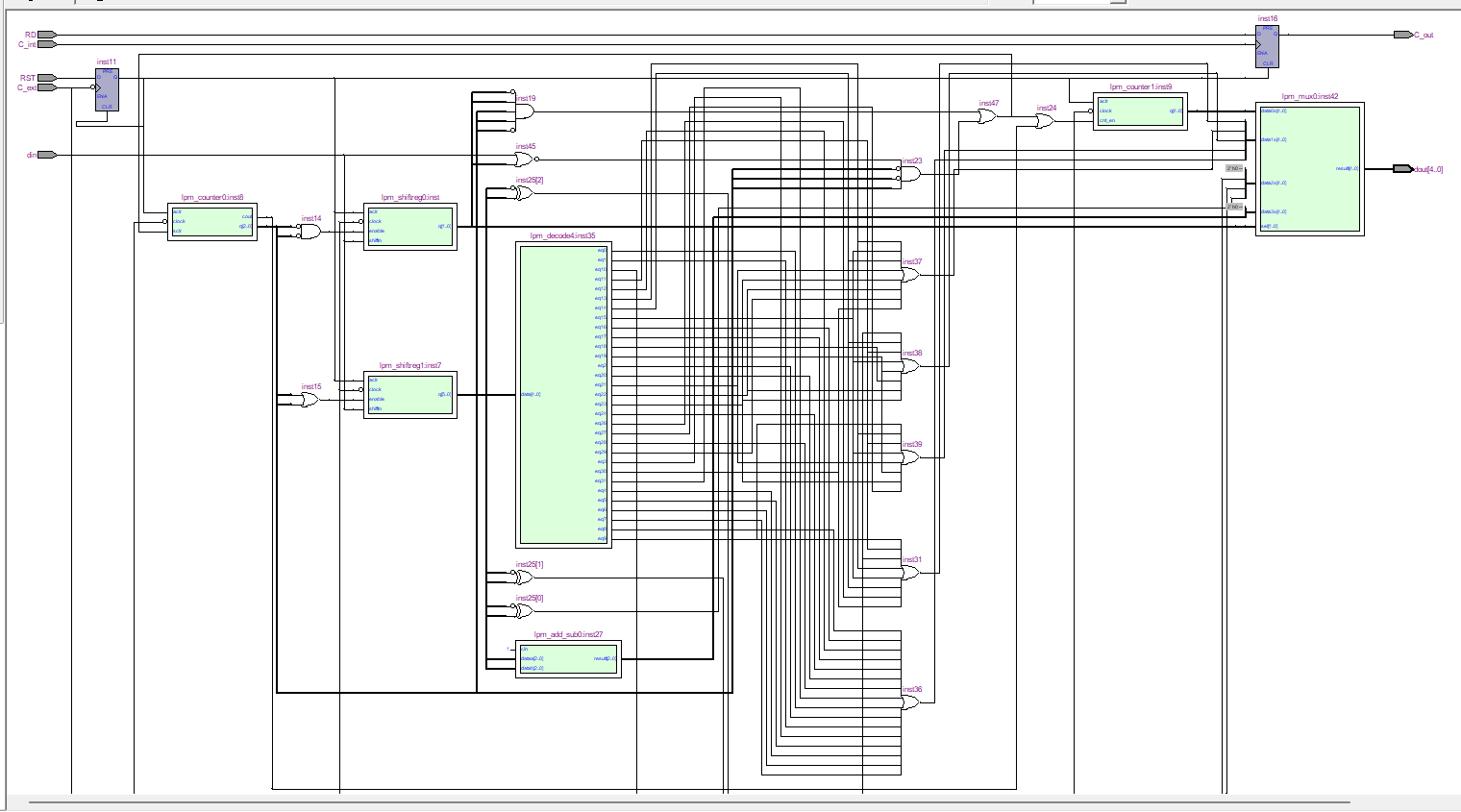

По данному коду было построено схемотехническое представление при помощи инструмента RTL Viewer (рисунок 2.11).

Рисунок 2.11 – Схема по коду в RTL Viewer

Работа схемы, описанной в виде кода, также была промоделирована в 2 режимах (рисунки 2.12 – 2.17). Комбинации входных данных аналогичны тем, что использовались при прошлом моделировании.

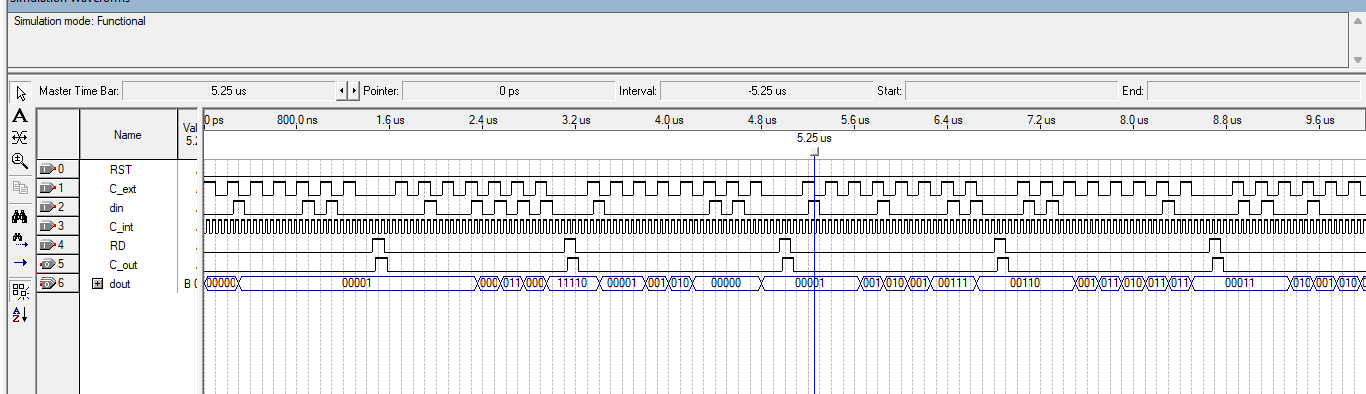

Рисунок 2.12 – Первая часть моделирования в режиме Timing

Рисунок 2.13 – Вторая часть моделирования в режиме Timing

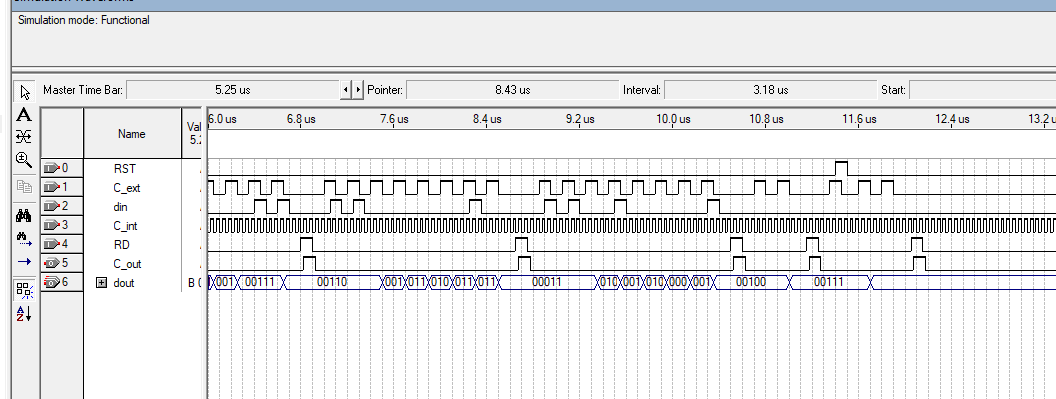

Рисунок 2.14 – Первая часть моделирования в режиме Functional

Рисунок 2.15 – Вторая часть моделирования в режиме Functional

Можно заметить, что результаты моделирования, проведенного по изначальной схеме и по коду, написанному на VHDL, абсолютно идентичны, а также совпадают с планом моделирования и построенными таблицами функционирования для различных операций, из чего можно сделать вывод, что построение и моделирование схемы было произведено без ошибок.