ЛР 3 / ЭИС2_ЛР3

.docx

|

|

|

Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ ТРИГГЕРОВ, РЕГИСТРОВ И СЧЁТЧИКОВ

Отчет по лабораторной работе №11

по дисциплине «Электроника и схемотехника 2»

Вариант №11

Студент гр. 712-1

31.05.2024

Руководитель

Старший преподаватель кафедры КИБЭВС

_______ Семёнов А.С.

01.06.2024

Введение

Цель работы: научиться совместно применять триггеры, регистры и счётчики.

Постановка задачи: взять четыре функции из таблицы первой лабораторной работы (собственную, две выше своей и одну ниже своей) и составить для них таблицу истинности, обозначив в ней порядок разрядов.

Формулы выглядят следующим образом:

F12: 𝑋=𝐴∪𝐵⊕𝐶∩𝐷;

F11: 𝑋=𝐴⊕𝐵∩𝐶∪𝐷;

F10: 𝑋=𝐴∩𝐵∪𝐶⊕𝐷;

F9:

𝑋=𝐴∪𝐵∪ .

.

После этого организовать прием и выдачу данных для выполнения 4-х параллельных операций над полубайтом согласно варианту №11 (прием осуществляется с синхронизацией данных по нарастающему фронту, параллельным кодом и синхронным типом сброса, а выдача осуществляется синхронизацией данных по убывающему фронту, последовательным кодом старшими разрядами вперед и активным уровнем сигнала «read», равным единицы), собрать схему с использованием встроенных блоков регистров.

Далее промоделировать работу схемы в двух режимах и сверить результаты моделирования с данными из таблицы истинности. Потом повторить предыдущие действия, только для описания устройств с использованием языка System Verilog, заданного нечетностью варианта №11 (также должен быть реализован конечный автомат для выдачи данных и их тактирования, в связи с передачей выходных данных последовательным кодом, по варианту). После написать отчет о проделанной работе.

1 РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ 12,11,10,9

Таблица истинности

Для реализации вычислителя функций была составлена таблица истинности, представленная ниже (таблица 1.1).

Таблица 1.1 - Таблица истинности для реализации вычислителя функций

Входы |

Выходы |

|||||||

A |

B |

C |

D |

F4 |

F3 |

F2 |

F1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

1.2 Логические формулы

Формулы для выходов таблицы истинности выглядят следующим образом:

Формула для функции 4: 𝑋=𝐴∪𝐵⊕𝐶∩𝐷;

Формула для функции 3: 𝑋=𝐴⊕𝐵∩𝐶∪𝐷;

Формула для функции 2: 𝑋=𝐴∩𝐵∪𝐶⊕𝐷;

Формула для функции 1: 𝑋=𝐴∪𝐵∪ .

1.3 Функциональная схема

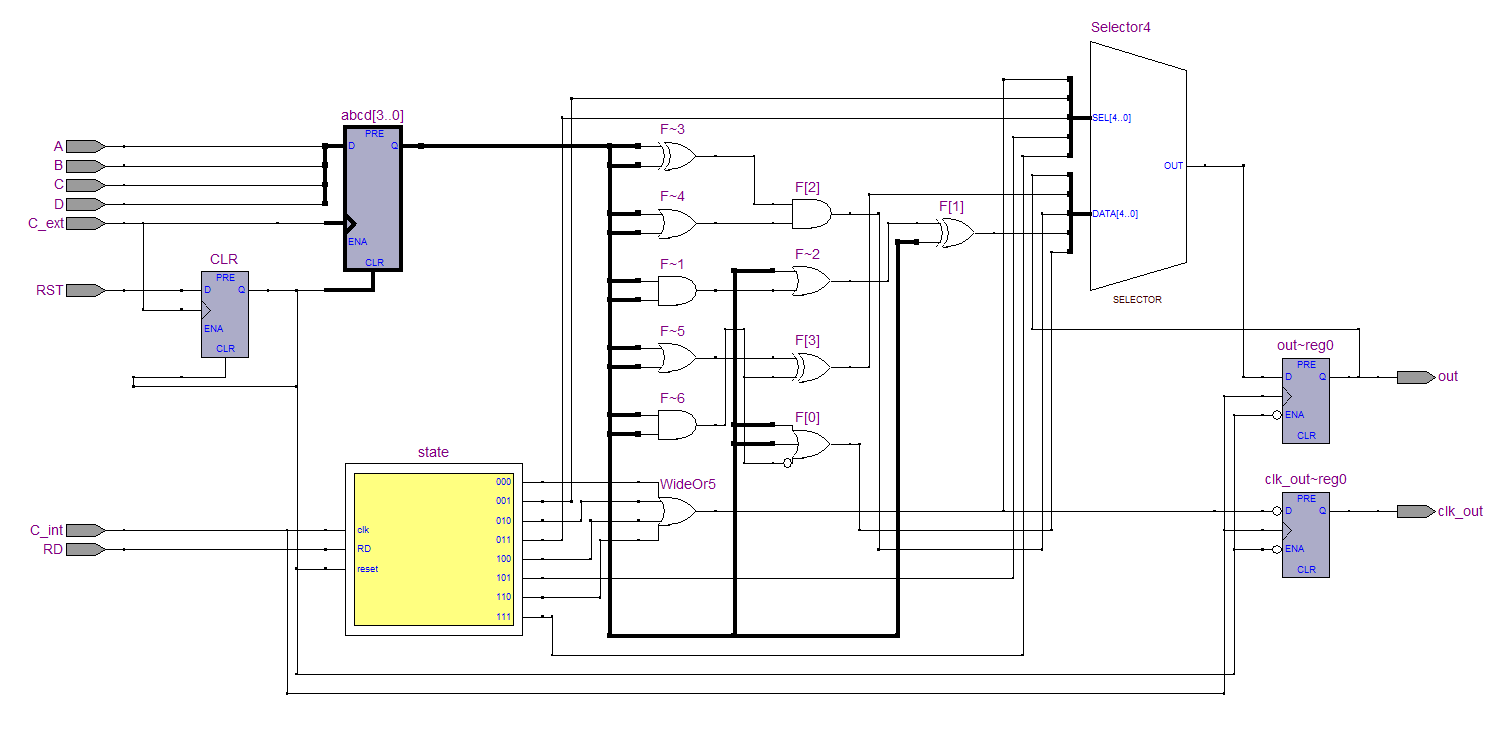

Ниже приведена функциональная схема вычислителя функций, в которой функции F12, F11, F10, F9 реализованы через формулы, а также реализован встроенный блок регистра lpm_dff, который генерирует входные значения на мультиплексоры функций (рисунок 1.1).

Рисунок 1.1 – Функциональная схема вычислителя функций

1.4 Моделирование

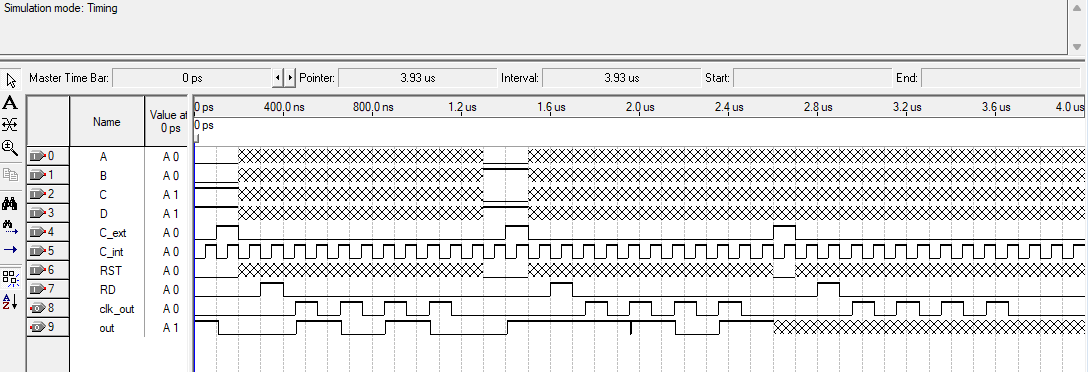

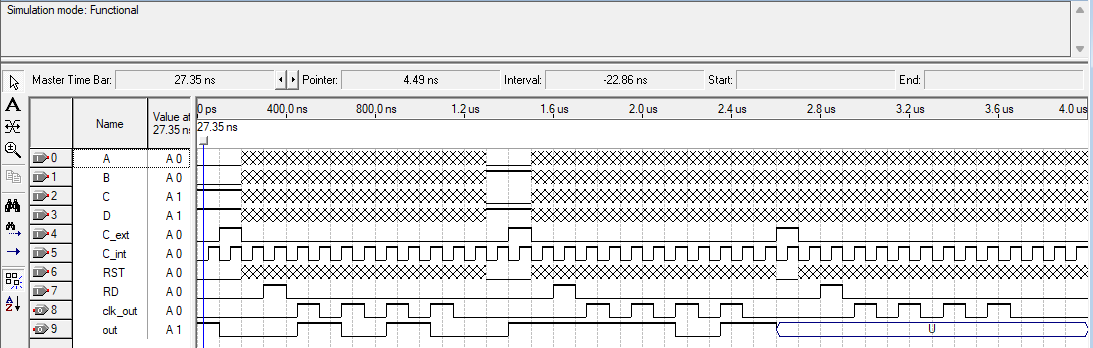

Ниже представлено моделирование схемы в режимах Timing и Functional (рисунок 1.2 – 1.3). Для моделирования были выбраны строки, выделенные маркером из таблицы истинности, которые задаются в моделировании в таком же порядке. Прием данных осуществляется по переднему фронту сигнала C_ext, параллельным кодом.

Рисунок 1.2 – Моделирование схемы в режиме Timing

Рисунок 1.3 – Моделирование схемы в режиме Functional

Как можно заметить из рисунков 1.2 – 1.3, результаты моделирования совпадают с данными из таблицы истинности.

1.5 Код на System Verilog

Ниже представлен код схемы на System Verilog (рисунок 1.4 – 1.5). На строках 2-4 описаны входы и выходы схемы, на строках 23-26 записаны формулы функций. На строках 33-72 описана работа конечного автомата, а на строках, а также присвоение значений функций к переменной RD.

Рисунок 1.4 – Первая часть кода на System Verilog

Рисунок 1.5 – Вторая часть кода на System Verilog

1.6 Схема из RTL Viewer для кода SV

Ниже представлена схема из RTL viewer для написанного кода на System Verilog (рисунок 1.6).

Рисунок 1.6 – Схема из RTL viewer для кода на System Verilog

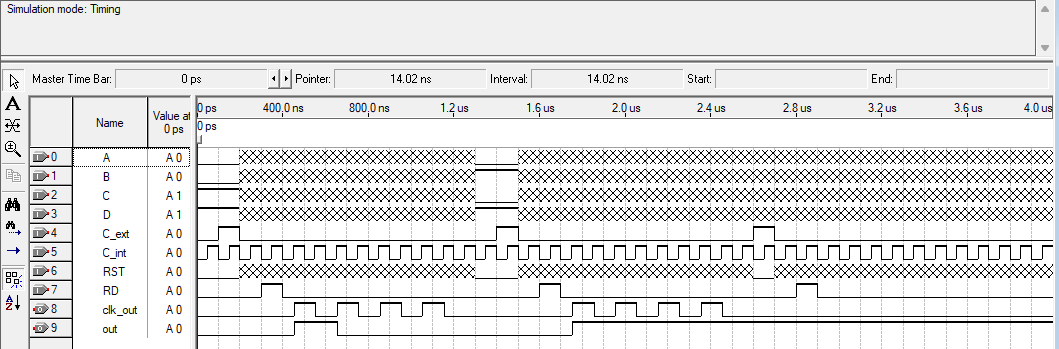

Ниже представлено моделирование в режиме Timing и Functional устройства, описанного кодом System Verilog (рисунок 1.7-1.8).

Рисунок 1.7 – Моделирование устройства, описанного кодом System Verilog, в режиме Timing

Рисунок 1.8 – Моделирование устройства, описанного кодом System Verilog, в режиме Functional

Как можно заметить из рисунка 1.7-1.8, результаты моделирования полностью совпадают с данными из таблицы истинности.

Заключение

В результате лабораторной работы было изучено совместное применение триггеров, регистров и счётчиков.

Были взяты четыре функции из таблицы первой лабораторной работы (собственная, две выше своей и одна ниже своей) и составлена для них таблица истинности.

После этого был организован прием и выдача данных для выполнения 4-х параллельных над полубайтом согласно варианту №11 (прием осуществляется с синхронизацией данных по нарастающему фронту, параллельным кодом и синхронным типом сброса, а выдача осуществляется синхронизацией данных по убывающему фронту, последовательным кодом старшими разрядами вперед и активным уровнем сигнала «read», равным единицы), собрать схему с использованием встроенных блоков регистров

Потом были повторены предыдущие действия, только для описания устройств с использованием языка System Verilog, заданного нечетностью варианта №11 (также был реализован конечный автомат для выдачи данных и их тактирования, в связи с передачей выходных данных последовательным кодом, по варианту). Было проведено моделирование написанного кода и его результаты были сравнены с данными из таблицы истинности. Так как результаты моделирования совпали с данными из таблицы истинности, можно сказать, что эта часть работы была выполнена правильно.

|

Томск 2024 |

|