- •Введение

- •1. Ознакомление с лабораторным стендом и исследование простейших комбинаторных логических схем

- •1.1. Краткое описание лабораторной работы

- •1.2.1. Общие сведения о лабораторном стенде

- •1.2.2. Накладки для выполнения стандартных лабораторных работ

- •1.2.3. Работа с пользовательским интерфейсом стенда

- •1.2.4. Загрузка в стенд новых лабораторных работ

- •1.2.5. Рекомендации по сборке электрических схем

- •1.3. Основные теоретические сведения

- •1.4. Задание на проведение лабораторной работы

- •2. Мультивибраторы на логических элементах

- •2.1. Краткое описание лабораторной работы

- •2.2. Основные теоретические сведения

- •2.3. Задание на проведение исследований

- •3. Исследование схем триггеров

- •3.1. Краткое описание лабораторной работы

- •3.2. Основные теоретические сведения

- •3.3. Задание на проведение исследований

- •4. Регистры и счетчики

- •4.1. Краткое описание лабораторной работы

- •4.2. Основные теоретические сведения

- •4.3. Задание на проведение исследований

- •5. Синхронные цифровые схемы и устройства ввода-вывода

- •5.1. Краткое описание лабораторной работы

- •5.2. Основные теоретические сведения

- •5.3. Задание на проведение исследований

- •6.1. Краткое описание лабораторной работы

- •6.2. Основные теоретические сведения

- •6.3. Задание на проведение исследований

- •7. Исследование схем ЦАП и АЦП

- •7.1. Краткое описание лабораторной работы

- •7.2. Основные теоретические сведения

- •7.3. Задание на проведение исследований

3.ИССЛЕДОВАНИЕ СХЕМ ТРИГГЕРОВ

3.1.Краткое описание лабораторной работы

1.В лабораторной работе собираются и исследуются простейшие схемы RS-триггеров на ЛЭ, а также триггер-защелка, универсальный RS-D триггер, D-триггер с разрешением и синхронный JK-триггер, реализованные при помощи ПЛИС.

2.Для сборки схем простейших RS-триггеров используются универсальные ЛЭ 2И-НЕ,

2ИЛИ-НЕ.

3.Входные сигналы для собранных схем поступают с кнопок и переключателей, выходные сигналы исследуются осциллографом и индицируются светодиодами.

3.2. Основные теоретические сведения

Триггер – простейшее устройство последовательностной логики. В отличие от комбинаторной логики, где состояния выходов схемы определяются только текущими состояниями входов, в последовательностной логике уровни выходов зависят еще и от предыдущего состояния системы, имевшего место до последнего изменения уровней входов. Последовательностные цифровые схемы имеют способность запоминать свое состояние. Простейшее устройство, способное хранить информацию – триггер: схема на ЛЭ или готовая микросхема, функциональный узел, который хранит логический уровень, или один бит данных.

Простейший из триггеров, который можно построить на логических элементах – RS-триггер. Свое название он получил в соответствии с существующими у него входами управления: R (от англ. «reset», сброс) и S (от англ. «set», установка).

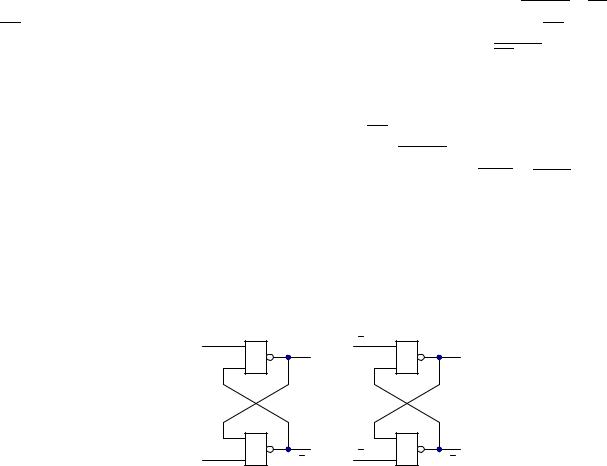

Схема такого триггера на ЛЭ типа ИЛИ-НЕ показана на Рис. 41, а. Принцип ее действия предельно прост. Предположим, в данный момент на входах схемы R и S действует уровень лог. «0», а на выходе схемы Q, называемым прямым выходом, действует некоторый уровень Qn.

Согласно принципу действия ЛЭ DD2, на его выходе уровень будет равен + 0 = . Выходназывают инверсным выходом триггера. Логический уровень с выхода поступает на

второй вход ЛЭ DD1, и на выходе продолжает действовать уровень + 0 = . Благодаря перекрестному включению ЛЭ, формирующему своего рода положительную обратную связь, пока оба входа R и S установлены в лог. «0», состояние схемы не изменится, т.е. триггер находится в режиме хранения бита. Если на вход R подать уровень лог. «1» (а на входе S будет

оставаться лог. «0»), то вне зависимости от значения , согласно принципу действия ЛЭ ИЛИНЕ, на выходе DD1 установится новый уровень +1 = + 1 = 0. Этот логический уровень

поступает на вход DD2, и на его выходе формируется уровень +1 = 0 + 0 = 1. Иными словами, подача уровня лог. «1» на вход R привела к сбросу триггера (к записи в него нулевого значения). Т.к. лог. «0» не меняет состояние схемы, а лог. «1» устанавливает Q = 0, вход R

называется входом сброса с активным высоким уровнем.

Рассуждая аналогично, несложно убедиться в том, что подача лог. «1» на вход S при R = 0 и при любом устанавливает +1=1, т.е. вход S является входом установки с активным высоким уровнем. В принципе, это следует и из описанного выше принципа действия входа R с учетом полной симметрии схемы.

R |

DD1 |

|

S |

DD1 |

|

|

Q |

|

Q |

||

|

1 |

|

& |

||

|

|

|

|

|

DD2 |

|

DD2 |

|

1 |

|

& |

S |

Q |

R |

Q |

|

|

||

|

а |

|

б |

Рис. 41. Схемы RS-триггера на ЛЭ ИЛИ-НЕ (а), И-НЕ (б)

— 36 —

При одновременной подаче уровня лог. «1» на оба входа, на обоих выходах схемы устанавливаются уровни лог. «0». Какой логический уровень будет действовать на выходе Q после снятия активных уровней с входов, определится лишь тем, с какого входа уровень будет снят последним (в реальности одновременно изменить логические уровни в двух разных цепях невозможно). Для схемы RS-триггера комбинация двух активных уровней на входах установки и сброса считается запрещенной, т.к. схема перестает выполнять свою основную функцию. Состояние триггера при одновременной подаче двух управляющих сигналов называется

метастабильным.

Немного отличается от рассмотренной схемы вариант RS-триггера на элементах И-НЕ

(см. Рис. 41, б). Нетрудно убедиться в том, что если установить = = 1, состояние схемы не

изменяется. Установка = 1, = 0 переводит выход Q в состояние лог. «1», а = 0, = 1 – в лог. «0». То есть, выходы сброса и установки у такого RS-триггера имеют низкий активный

уровень, а запрещенной комбинацией является, соответственно, = = 0. Обратите внимание, что взаимное расположение входов сброса/установки и прямого/инверсного выходов у двух крайне похожих друг на друга схем – разное.

Помимо RS-триггера существует еще множество схем триггеров со своими входами управления и особенностями работы, доступных в виде готовых интегральных схем или функциональных узлов ПЛИС. Описание схемотехнических реализаций всех триггеров на ЛЭ не входит в задачи настоящих методических указаний и широко освещено в литературе. Отметим лишь, что существуют, в частности:

JK-триггеры, которые выгодно отличаются от RS-триггеров отсутствием запрещенного состояния входов. Одновременная подача активных уровней на вход установки J (от англ. «jump») и вход сброса K (от англ. «kill») приводит к изменению состояния выхода такого триггера на противоположное.

T-триггеры (от англ. «toggle»). Логический переход на Т-входе (положительный или отрицательный фронт, в зависимости от модификации схемы или компонента) приводит к изменению состояния на противоположное. Фактически, Т-триггер – это JK-триггер, входы которого закорочены.

Триггеры с разрешением. Например, если объединить оба входа R и S схемы, показанной на Рис. 41, а, с дополнительным входом E через элементы И, то при

Е= 0 триггер оказывается нечувствительным к изменениям состояний R и S, а при

Е= 1 работает как обычно.

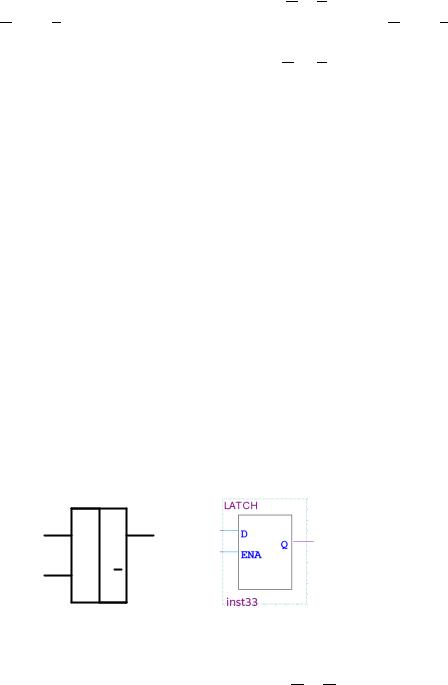

Интересной разновидностью триггера с разрешением является триггер-защелка:

DD2

T

DQ

EQ

а |

б |

Рис. 42. УГО триггера-защелки согласно ЕСКД (а) и примитив LATCH (б)

Данный триггер представляет собой узел, способный запоминать бит, присутствующий на

входе D. Работает он следующим образом. Если E = 0, то Q = D (и, = , соответственно). Такой режим называется режимом прозрачности: всякое изменение входного логического уровня мгновенно (с задержкой, определяемой только быстродействием компонента) отражается на выходе триггера-защелки.

— 37 —

После подачи на вход Е уровня лог. «0», режим прозрачности выключается и триггер переходит в режим хранения, защелкивая бит, присутствовавший на входе D непосредственно до перевода E в лог. «0».

В настоящей лабораторной работе триггер-защелка построен в ПЛИС с использованием ПО Quartus Prime и примитива LATCH. Примитивом называется элементарный функциональный узел, поддерживаемый данной ПЛИС, и могущий быть использованным для построения более сложных схем без применения каких-либо сторонних библиотек компонентов. УГО примитива LATCH в Quartus Prime показано на Рис. 42, б. Компонентом дискретной логики, аналогичным данному примитиву, является, например, микросхема 74хх77. Для получения инверсного выхода у триггера-защелки для выполнения лабораторной работы (здесь и далее) в конфигурации ПЛИС был использован обычной инвертор, также являющийся примитивом.

Отдельное внимание следует уделить синхронным триггерам. В сущности, все современные цифровые схемы и узлы, в том числе, реализуемые на ПЛИС или являющиеся частью сложных интегральных схем, построены исключительно с применением синхронных триггеров, а обычный, или асинхронный RS-триггер или триггер-защелка представляют, скорее, академический интерес.

Термин «синхронный» применительно к последовательностным цифровым узлам означает, что у схемы, примитива или интегральной микросхемы существует отдельный тактовый вход, обычно обозначаемый как С или CLK (от англ. «clock»). Все изменения состояния функционального узла, в том числе, триггера (будь то синхронный RSJK- или Т-триггер) происходят только по логическому переходу уровня на тактовом входе, чаще всего – по фронту.

Если речь идет о синхронном Т-триггере, то вход T приобретает, фактически, смысл входа разрешения переключения по фронту сигнала на входе C, если о синхронных RSили JKтриггере, то входы приобретают смысл разрешения установки или сброса триггера по фронту тактового сигнала.

Синхронные триггеры состоят из целого ряда ЛЭ, подробно внутренние структуры синхронных триггеров здесь рассматриваться не будут. Рассмотрим лишь особенности функционирования синхронных триггеров, изучаемых в настоящей лабораторной работе.

Практика разработки цифровых узлов последовательностного типа, в том числе, с использованием микросхем программируемой логики, показывает, что практически любую задачу можно решить, используя лишь синхронные триггеры одного типа, например, D- триггеры. Фактически, такой триггер является элементарной ячейкой памяти с одним входом D. Логический уровень, присутствующий на этом входе, запоминается по фронту тактового сигнала, подключенного ко входу С, и становится доступным на выходе Q.

Существует две трактовки названия этого триггера. Согласно одной из них, более распространенной, D происходит от английского «data» – вход данных, что совершенно естественно для основной функции триггера. Вторая трактовка говорит, что D образовано от слова «delay» («задержка»). Действительно, изменение логического уровня на входе D отражается на выходе Q с некоторой задержкой, только в момент поступления импульса на тактовый вход С. Если включить несколько таких триггеров последовательно, можно получить задержку на 2, 3 и более периодов тактового сигнала.

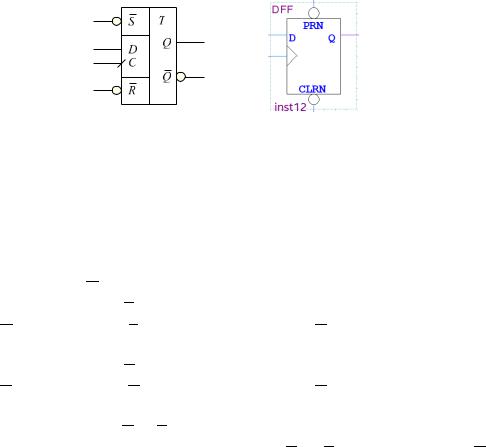

Наиболее удобны и популярны D-триггеры с дополнительными, асинхронными входами сброса (R) и установки (S). Работают эти входы точно так же, как и у простейшего RS-триггера, и никак не завязаны на тактовый вход С (отсюда название – «асинхронные»). Обычно они служат для того, чтобы реализовать начальную установку триггера в нужное состояние «по умолчанию», непосредственно после включения питания схемы. Примером такого триггера является весьма популярная микросхема 74хх74 – два синхронных D-триггера с асинхронными входами установки/сброса и с комплементарными выходами, которые можно также назвать RS-D триггерами. Условное графическое обозначение (УГО) такого триггера показано на Рис. 43, а.

— 38 —

а б

Рис. 43. УГО RS-D триггера согласно ЕСКД (а) и примитив DFF (б)

Принцип действия такого триггера следующий:

По фронту тактового сигнала С триггер запоминает логический уровень входа D. Он подается на выход Q, т.е. +1 = . Тот факт, что триггер меняет состояние по фронту С, находит свое отражение в его УГО в виде косой черты «/» на тактовом входе (для других микросхем, которые срабатывают по срезу (обратному фронту) тактового сигнала, направление этой косой черты противоположное – «\»).

Инверсный выход всегда обратен прямому Q.

Подача лог. «0» на вход в любой момент времени устанавливает триггер в состояние

Q = 1, = 0. Удержание = 0 обеспечивает Q = 1, = 0 вне зависимости от уровней

и переключений D и С.

Подача лог. «0» на вход в любой момент времени устанавливает триггер в состояние

Q = 0, = 1. Удержание = 0 обеспечивает Q = 0, = 1 вне зависимости от уровней

и переключений D и С.

Одновременная подача = = 0 переводит триггер в нестабильное состояние, т.к.

при попытке одновременной смены уровней на = = 1 состояния Q и будут не определены ввиду невозможности одновременного изменения уровней (см. выше).

В настоящей лабораторной работе RS-D триггер получен при помощи примитива DFF (см. Рис. 43, б; инверсный выход триггера получен из прямого при помощи инвертора). Вход асинхронной установки у данного триггера-примитива называется PRN (от англ. «Preset Negative»), а сброса – CLRN («CLeaR Negative»). Тактовый вход примитива-триггера, как видно, обозначен символом «►». Заметим, что почти все примитивы триггеров в ПО Quartus Prime имеют в составе своего названия символы «FF» от англ. «Flip-Flop»

Куда более полезным функциональным узлом для построения сложных схем является RS- D триггер, аналогичный рассмотренному выше, но имеющий дополнительный вход – вход разрешения работы, который разрешает или запрещает триггеру запоминать бит со входа D по фронту тактового сигнала. Самым простым примером, где подобный триггер незаменим, является задача защиты от дребезга кнопок какой-то цифровой схемы, работающей на высокой тактовой частоте. Подробно данный пример будет рассмотрен в настоящих методических указаниях ниже, сейчас же ограничимся тем, что для реализации такой защиты требуется разрешать триггеру запоминать состояние кнопки не на каждом, а на каждом энном такте, так, чтобы опрос кнопки происходил примерно каждые 10-20 мс.

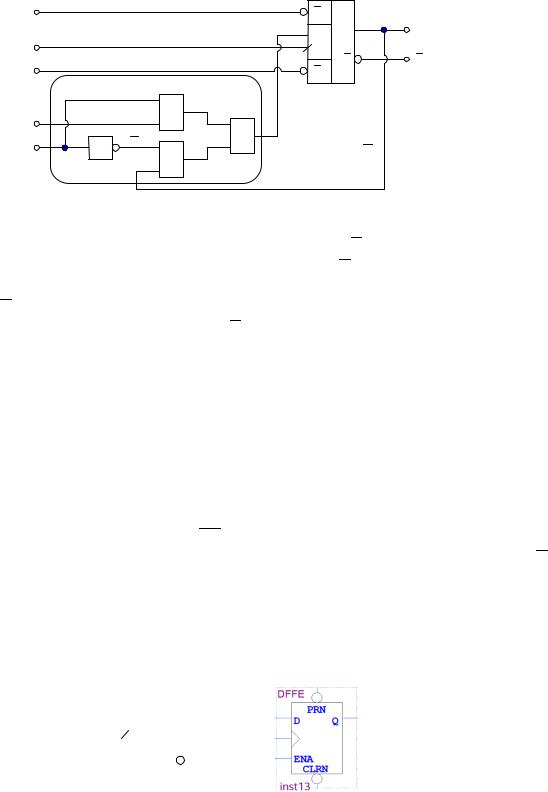

Для получения такого функционала категорически нельзя использовать обычный D- триггер и отключить ему тактовый сигнал логическим элементом, так как в этом случае нарушается основной принцип построения синхронных логических схем из-за того, что на некоторый тактовый вход начинает воздействовать более одного сигнала (о последствиях такого подхода речь также пойдет в следующих лабораторных работах). В действительности, для того, чтобы дополнить микросхему 74хх74 или ее аналог функцией разрешения защелкивания бита на D, требуется использовать несколько логических элементов и построить из них двухвходовый мультиплексор – схему, которая передает на свой выход один из двух входных сигналов. Какой из сигналов передается на выход, определяется управляющим сигналом. Назовем его, в применении к схеме D-триггера с разрешением, E, от англ. «enable» (см. Рис. 44).

— 39 —

|

DD5 |

|

|

S |

S |

T |

|

|

D |

Q |

Q |

|

|

|

|

C |

C |

|

|

|

|

Q |

Q |

R |

R |

|

|

|

Схема мультиплексора |

|

|

|

DD2 |

|

|

&DD3

D |

1 |

|

E |

E |

|

& |

||

|

= ∙ + ∙

DD1 |

DD4 |

|

Рис. 44. Схема D-триггера с разрешением на основе обычного RS-D триггера

Рассмотрим состояние мультиплексора при E = 1. В этом случае на выходе DD2 (И) логический уровень равен ∙ = ∙ 1 = . В то же самое время = 0 и на выходе такого же

логического элемента DD4 уровень определяется выражением ∙ = ∙ 0 = 0. Соответственно, логический уровень на выходе ЛЭ DD3 (ИЛИ) определится выражением вида

= ∙ + ∙ = ∙ 1 + ∙ 0 = . В случае если Е = 0, согласно тому же выражению для

логического уровня Х получим: = ∙ + ∙ = ∙ 0 + ∙ 1 = . Соответственно, логику работы мультиплексора можно описать следующим образом:

, если = 1

= { , если = 0 .

Таким образом, при E = 0 триггер DD5 на каждом такте С будет запоминать значение, поступающее с его же прямого выхода. То есть, фактически, состояние схемы изменяться по фронту тактового сигнала не будет. Если же Е = 1, то на вход триггера будет приходить сигнал со входа D всей схемы, и на каждом такте сигнала С значение, хранящееся в триггере, будет обновляться.

К сожалению, одиночные D-триггеры с входом разрешения синхронной работы в наборе микросхем 74хх отсутствуют. Имеется лишь микросхема 74xx377, представляющая собой восемь

D-триггеров с общим входом разрешения (от англ. «clock enable», с активным низким

уровнем). Индивидуальных входов разрешения для триггеров, комплементарных выходов , входов асинхронной установки S и сброса R, у данной микросхемы нет. В средах разработки конфигураций микросхем программируемой логики, однако, такой примитив присутствует в обязательном порядке, и является одним из наиболее популярных при составлении каких-либо схем.

В настоящей лабораторной работе исследуется D-триггер с разрешением (см. Рис. 45, а), который построен на примитиве DFFE.

DD2

|

D |

T |

|

||

|

|

||||

|

C |

Q |

|

||

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

Q |

|

||

|

|

||||

|

|

|

|

|

|

а б

Рис. 45. УГО D триггера с разрешением согласно ЕСКД (а) и примитив DFFE (б)

Как видно, примитив DFFE, фактически, реализует RS-D триггер с разрешением, также имеющим асинхронные входы установки и сброса. В лабораторной работе они, однако, для простоты не выведены на физические линии со штырьковыми разъемами, и конфигурацией ПЛИС оба подключены к лог. «1» (то есть, функционал асинхронной установки и сброса отключен). В реальных схемах следует задействовать как минимум один из таких входов для

— 40 —

начальной инициализации состояния триггера, что будет показано в следующих лабораторных работах.

Конфигурация ПЛИС для данной лабораторной работы реализует еще три триггера, рассмотренных ниже.

Синхронный JK-триггер, имеющий тактовый вход и два входа управления – J и K. Изменение состояния триггера происходит по фронту тактового сигнала, при этом:

если J = 1, K = 0 то триггер устанавливается в +1 = 1;

если J = 0, K = 1, триггер сбрасывается в +1 = 0;

если J = K = 0 то триггер не меняет состояния ( +1 = );

|

|

|

|

|

|

|

+1 |

̅̅̅̅ |

|

|

|

если J = K = 1, то триггер меняет свое состояние на противоположное ( |

= |

|

). |

||||||

|

|

DD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

|

T |

|

|

|

|

|

|

|

|

C |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

б |

в |

|

|

|

|

|

Рис. 46. УГО синхронного JK-триггера согласно ЕСКД (а),

примитив JKFF (б), примитив SRFF (в)

Синхронный RS-триггер, примитив которого показан на Рис. 48, в, фактически, по функционалу ничем не отличается от JKFF. Асинхронный RS-триггер имеет запрещенное состояние в виде двух активных уровней на входах, инициирующих сброс и установку. В синхронном же RS-триггере входы имеют смысл входов разрешения сброса и установки по фронту тактового сигнала, вопрос невозможности одновременного снятия двух активных уровней не стоит; синхронный RS-триггер, построенный на примитиве SRFF в используемой ПЛИС, ведет себя так же, как синхронный JK-триггер.

Последний триггер, реализованный в ПЛИС – синхронный Т-триггер, или, как его еще называют, пересчетный триггер. Его вход Т выполняет функцию разрешения изменения состояния. Если Т = 0, то состояние триггера не меняется, и на очередном такте +1 = . Если

же T = 1, то на каждом такте |

имеет место |

изменение уровня на выходе триггера на |

|||||||||

|

+1 |

̅̅̅̅ |

|

|

|

|

|

|

|

|

|

противоположный, т.е. |

= |

|

, а триггер «переворачивается», «переключается», что и дало |

||||||||

|

|

||||||||||

ему имя от английского «toggle». |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

DD2 |

|

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

T |

|

|

|||

|

|

|

C |

|

Q |

|

|

|

|||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

Q |

|

|

|

|||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

б |

||||

Рис. 47. УГО синхронного Т-триггера согласно ЕСКД (а), примитив TFF (б)

— 41 —