МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №7

по дисциплине «Цифровая схемотехника»

Тема: Исследование схем ЦАП и АЦП

Студент гр. 0207 _________________ Маликов Б.И.

Преподаватель _________________ Аристов С.А.

Санкт-Петербург

2023

ЦЕЛЬ РАБОТЫ

Целью работы является исследование схемы ЦАП на резисторной матрице R-2R и АЦП, использующее этот ЦАП в своем составе.

ОБРАБОТКА РЕЗУЛЬТАТОВ ИЗМЕРЕНИЙ

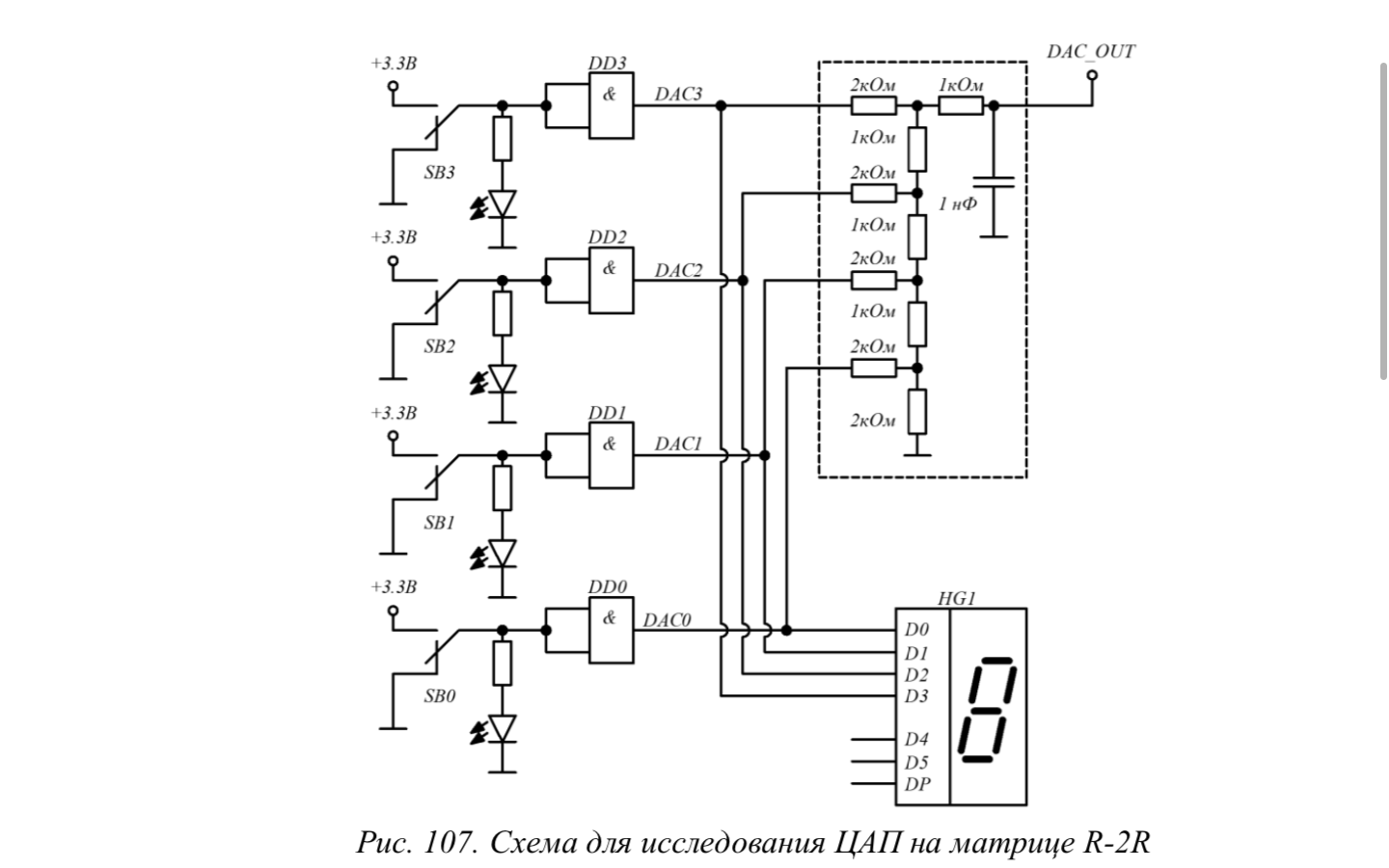

1. Исследование схемы ЦАП на матрице R-2R

Рис. 1 – Схема для исследования ЦАП на матрице R-2R

Таблица 1. Зависимость напряжения в цепи DAC_OUT от числа DAC[3..0]

DAC[3..0] |

B16 |

UИЗМ, В |

UТЕОР, В |

(относ. погрешность) |

Дифф. нелинейность (DNL), LSB |

0000 |

0 |

0 |

0 |

- |

0,143 |

0001 |

1 |

0,24 |

0,21 |

14,29 |

-0,238 |

0010 |

2 |

0,4 |

0,41 |

2,44 |

-0,048 |

Продолжение таблицы 1

DAC[3..0] |

B16 |

UИЗМ, В |

UТЕОР, В |

% (относ. погрешность) |

Дифф. нелинейность (DNL), LSB |

0011 |

3 |

0,6 |

0,62 |

3,23 |

-0,048 |

0100 |

4 |

0,8 |

0,83 |

3,61 |

-0,048 |

0101 |

5 |

1 |

1,03 |

2,91 |

-0,048 |

0110 |

6 |

1,2 |

1,24 |

3,23 |

-0,048 |

0111 |

7 |

1,4 |

1,44 |

2,70 |

0,048 |

1000 |

8 |

1,62 |

1,65 |

1,81 |

0,143 |

1001 |

9 |

1,86 |

1,86 |

0,20 |

-0,714 |

1010 |

10 |

1,92 |

2,06 |

6,91 |

0,333 |

1011 |

11 |

2,2 |

2,27 |

3,08 |

-0,048 |

1100 |

12 |

2,4 |

2,48 |

3,23 |

0,048 |

1101 |

13 |

2,62 |

2,68 |

2,28 |

0,048 |

1110 |

14 |

2,84 |

2,89 |

1,65 |

-0,048 |

1111 |

15 |

3,04 |

3,09 |

1,74 |

- |

Примеры вычислений при B16 = 1:

UТЕОР

= 0 + 0

+ 0 + 0

+ 0 + 1

+ 1

= 1

= 1 + 0

+ 0 + 1

+ 1 + 1

+ 1 = 0,21 В

= 0,21 В

=

=

=

=

= 14,29%

= 14,29%

LSB

=

=

=

= 0,21 В – младший

значащий разряд

= 0,21 В – младший

значащий разряд

DNL =

–

1 =

–

1 =

–

1 = -0,238 LSB

–

1 = -0,238 LSB

Интегральная

нелинейность: INL

=

100%

=

100%

=

100%

= 4,5%

100%

= 4,5%

Рис. 2 – График зависимости напряжения в цепи DAC_OUT от числа DAC[3..0]

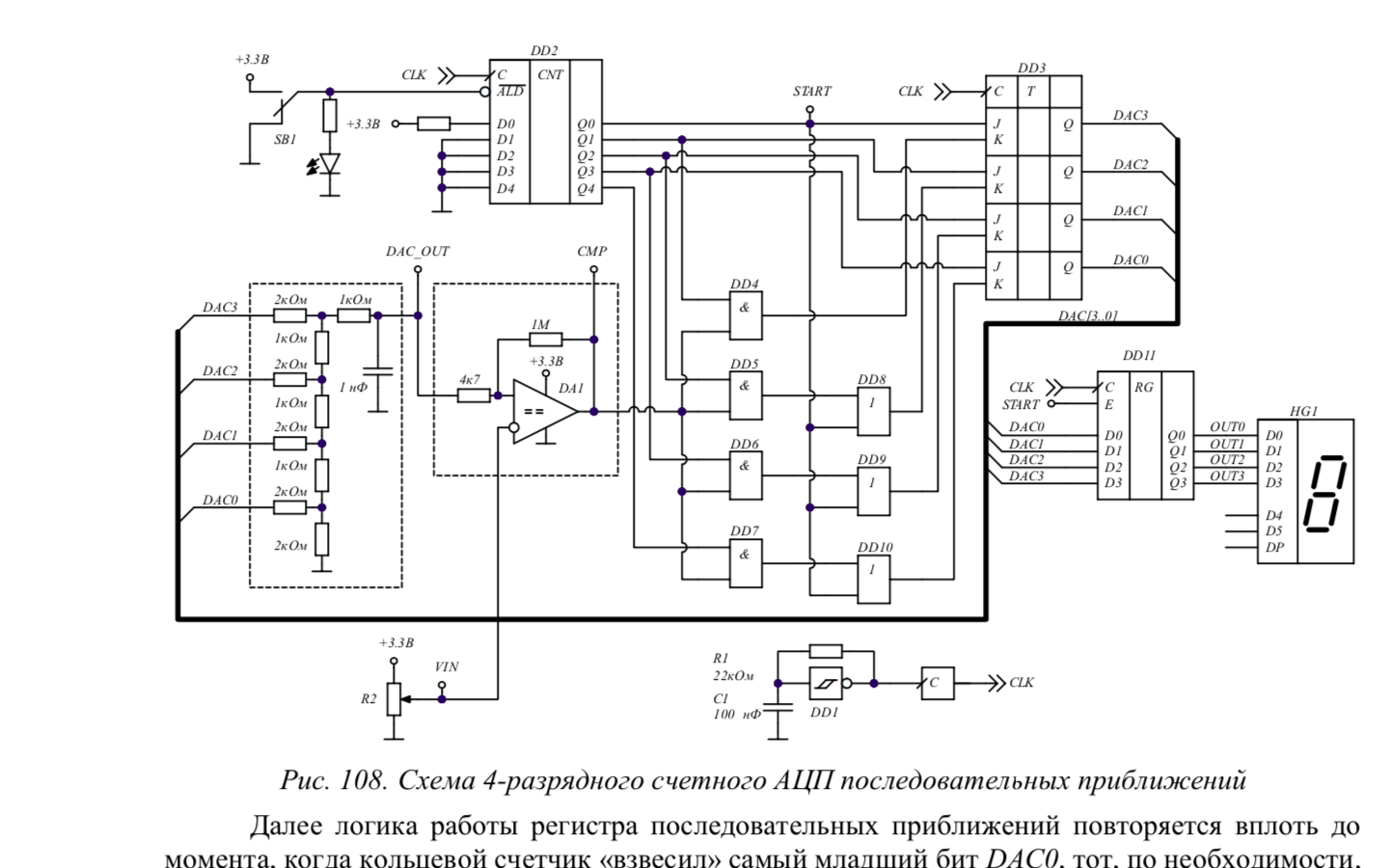

2. Исследование схемы 4-разрядного счетного АЦП последовательных приближений

Рис. 3 - Схема 4-разрядного счетного АЦП последовательных приближений

Таблица 2. Зависимость результата преобразования схемы OUT[3..0] от входного напряжения VIN

B2 |

B16 |

UИЗМ, В |

UТЕОР, В |

0000 |

0 |

0 |

0 |

0001 |

1 |

0,24 |

0,21 |

0010 |

2 |

0,4 |

0,41 |

0011 |

3 |

0,6 |

0,62 |

0100 |

4 |

0,82 |

0,83 |

0101 |

5 |

1 |

1,03 |

0110 |

6 |

1,2 |

1,24 |

0111 |

7 |

1,4 |

1,44 |

1000 |

8 |

1,64 |

1,65 |

1001 |

9 |

1,88 |

1,86 |

1010 |

10 |

2,08 |

2,06 |

1011 |

11 |

2,28 |

2,27 |

1100 |

12 |

2,4 |

2,48 |

1101 |

13 |

2,64 |

2,68 |

1110 |

14 |

2,84 |

2,89 |

1111 |

15 |

3,24 |

3,09 |

Рис. 4 – График зависимости результата преобразования схемы OUT[3..0] от входного напряжения VIN

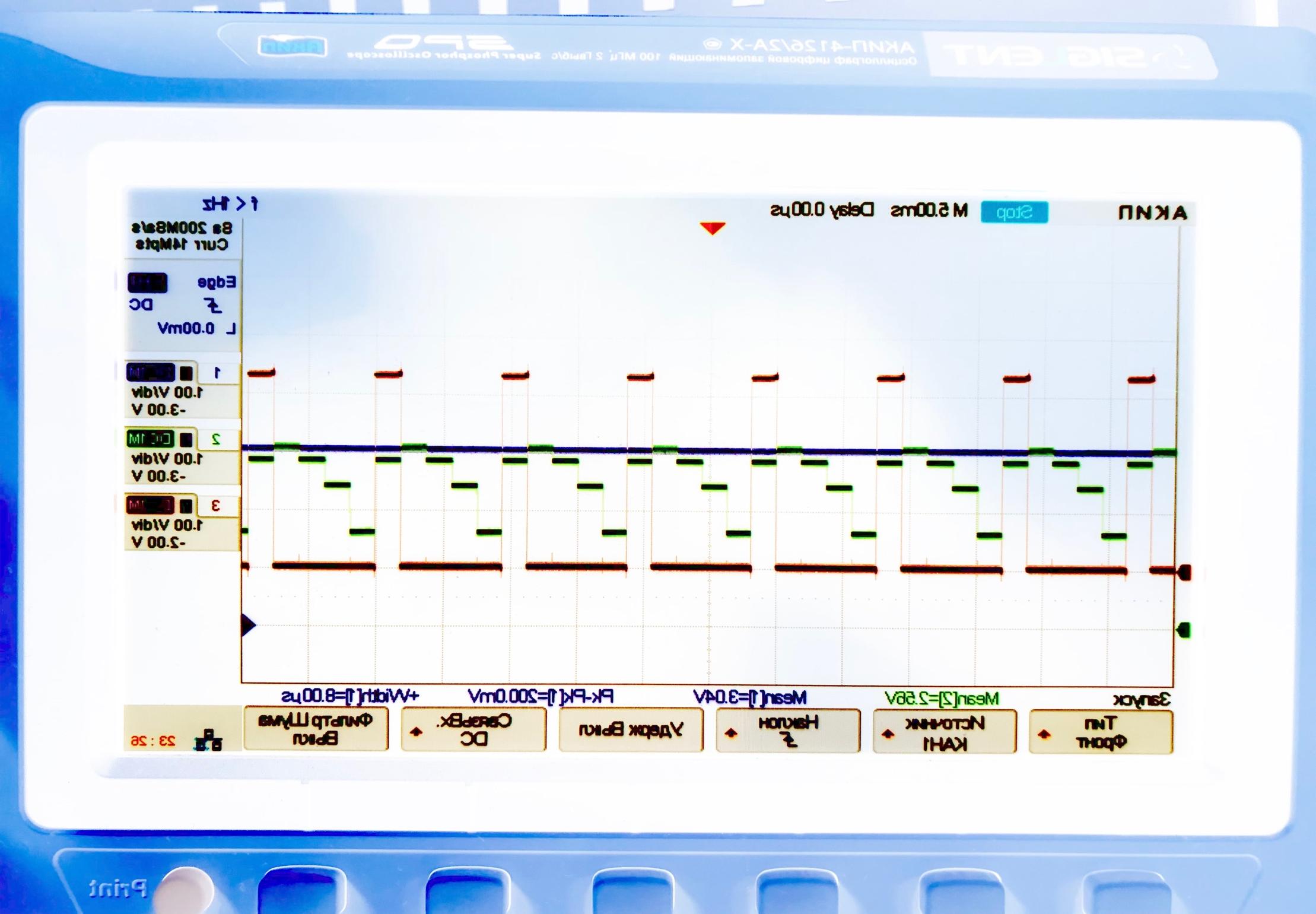

Цепь START (1

В/дел.)

Цепь VIN (1

В/дел.)

5

мс/дел.

Цепь DAC_OUT

(1 В/дел.)

Рис. 5 – Осциллограмма работы схемы 4-разрядного счетного АЦП последовательных приближений при B = 14 (номер стола – 14)

Опишем принцип действия данной схемы, разбив осциллограмму по тактам генератора, тактирующего схему:

Такт 1: Результат предыдущего преобразования копируется в регистр хранения, схемой устанавливается старший бит на ЦАП, все остальные – сбрасываются.

Такт 2: если сигнал с аналогового компаратора показывает, что напряжение ЦАП выше входного напряжения, схема сбрасывает старший бит ЦАП, в противном случае – сохраняет его равным 1. На этом же такте устанавливается второй по старшинству бит ЦАП.

Такт 3: если сигнал с компаратора показывает, что напряжение ЦАП выше входного напряжения, схема сбрасывает второй по старшинству бит ЦАП, в противном случае – сохраняет его равным 1. На этом же такте устанавливается третий по старшинству бит ЦАП.

Такт n-1: устанавливается младший бит на ЦАП.

Такт n: если сигнал с компаратора показывает, что напряжение ЦАП выше входного напряжения, схема сбрасывает младший бит, в противном случае – сохраняет его равным 1. На этом преобразование завершено. Нумерация тактов сбрасывается на 0.

За хранение промежуточного числа, выводимого в ЦАП, в простейшей схеме РПП отвечает массив JK-триггеров. Каждый из них устанавливается в единицу на том или ином такте, и сбрасывается в ноль на следующем такте, если компаратор показывает превышение напряжения ЦАП уровня входного напряжения. За «нумерацию» тактов отвечает кольцевой счетчик, одноединичный код на выходе которого показывает, какой из JK-триггеров следует установить или осуществить условный (по сигналу с аналогового компаратора) сброс. Результат преобразования же хранится в обычном параллельном регистре.

ВЫВОД

В ходе выполнения данной лабораторной работы были исследованы: c-схема ЦАП на матрице R-2R и схема 4-разрядного счетного АЦП последовательных приближений.

Для данных двух схем были рассчитаны теоретические значения напряжений от числа B. Сравнивая теоретические и практические зависимости, делаем вывод, что обе схемы работают корректно.

При этом, вращая ручку потенциометра по часовой и против часовой стрелки, делаем вывод, что наблюдения соответствует описанному принципу действия РПП.

%

%