МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №3

по дисциплине «Цифровая схемотехника»

Тема: Исследование схем триггеров

Студент гр. 0207 _________________ Маликов Б.И.

Преподаватель _________________ Аристов С.А.

Санкт-Петербург

2023

ЦЕЛЬ РАБОТЫ

Целью работы является сбор и исследование простейших схем RS-триггеров на ЛЭ, а также триггера-защелки, универсального RS-D триггера, D-триггера с разрешением и синхронного JK-триггера, реализованные при помощи ПЛИС.

ОСНОВНЫЕ ТЕОРЕТИЧЕСКИЕ ПОЛОЖЕНИЯ

Триггер – простейшее устройство последовательностной логики. В отличие от комбинаторной логики, где состояния выходов схемы определяются только текущими состояниями входов, в последовательностной логике уровни выходов зависят еще и от предыдущего состояния системы, имевшего место до последнего изменения уровней входов. Последовательностные цифровые схемы имеют способность запоминать свое состояние. Простейшее устройство, способное хранить информацию – триггер: схема на ЛЭ или готовая микросхема, функциональный узел, который хранит логический уровень, или один бит данных.

Простейший из триггеров, который можно построить на логических элементах – RS-триггер. Свое название он получил в соответствии с существующими у него входами управления: R (от англ. «reset», сброс) и S (от англ. «set», установка).

Схема такого триггера на ЛЭ типа ИЛИ-НЕ показана на Рис. 41, а. Принцип ее действия предельно прост. Предположим, в данный момент на входах схемы R и S действует уровень лог. «0», а на выходе схемы Q, называемым прямым выходом, действует некоторый уровень Qn.

Согласно принципу

действия ЛЭ DD2,

на его выходе уровень будет равен

=

=

.

Выход

называют

инверсным выходом триггера. Логический

уровень с выхода

поступает

на второй вход ЛЭ DD1,

и на выходе продолжает действовать

уровень

.

Выход

называют

инверсным выходом триггера. Логический

уровень с выхода

поступает

на второй вход ЛЭ DD1,

и на выходе продолжает действовать

уровень

=

.

Благодаря перекрестному включению ЛЭ,

формирующему своего рода положительную

обратную связь, пока оба входа R

и S

установлены

в лог. «0», состояние схемы не изменится,

т.е. триггер находится в режиме хранения

бита. Если на вход R

подать

уровень лог. «1» (а на входе S

будет

оставаться лог. «0»), то вне зависимости

от значения

,

согласно принципу действия ЛЭ ИЛИ- НЕ,

на выходе DD1

установится

новый уровень

=

.

Благодаря перекрестному включению ЛЭ,

формирующему своего рода положительную

обратную связь, пока оба входа R

и S

установлены

в лог. «0», состояние схемы не изменится,

т.е. триггер находится в режиме хранения

бита. Если на вход R

подать

уровень лог. «1» (а на входе S

будет

оставаться лог. «0»), то вне зависимости

от значения

,

согласно принципу действия ЛЭ ИЛИ- НЕ,

на выходе DD1

установится

новый уровень

=

=

= 0. Этот логический уровень поступает

на вход DD2,

и на его выходе формируется уровень

=

= 0. Этот логический уровень поступает

на вход DD2,

и на его выходе формируется уровень

=

= 1. Иными словами, подача уровня лог.

«1» на вход R

привела к

сбросу

триггера (к

записи в него нулевого значения). Т.к.

лог. «0» не меняет состояние схемы, а

лог. «1» устанавливает Q

= 0, вход R

называется

входом сброса

с активным

высоким уровнем.

= 1. Иными словами, подача уровня лог.

«1» на вход R

привела к

сбросу

триггера (к

записи в него нулевого значения). Т.к.

лог. «0» не меняет состояние схемы, а

лог. «1» устанавливает Q

= 0, вход R

называется

входом сброса

с активным

высоким уровнем.

Рис. 1 – Схемы RS-триггера на ЛЭ ИЛИ-НЕ (a), И-НЕ (б)

При одновременной подаче уровня лог. «1» на оба входа, на обоих выходах схемы устанавливаются уровни лог. «0». Какой логический уровень будет действовать на выходе Q после снятия активных уровней с входов, определится лишь тем, с какого входа уровень будет снят последним (в реальности одновременно изменить логические уровни в двух разных цепях невозможно). Для схемы RS-триггера комбинация двух активных уровней на входах установки и сброса считается запрещенной. Состояние триггера при одновременной подаче двух управляющих сигналов называется метастабильным.

ОБРАБОТКА РЕЗУЛЬТАТОВ ИЗМЕРЕНИЙ

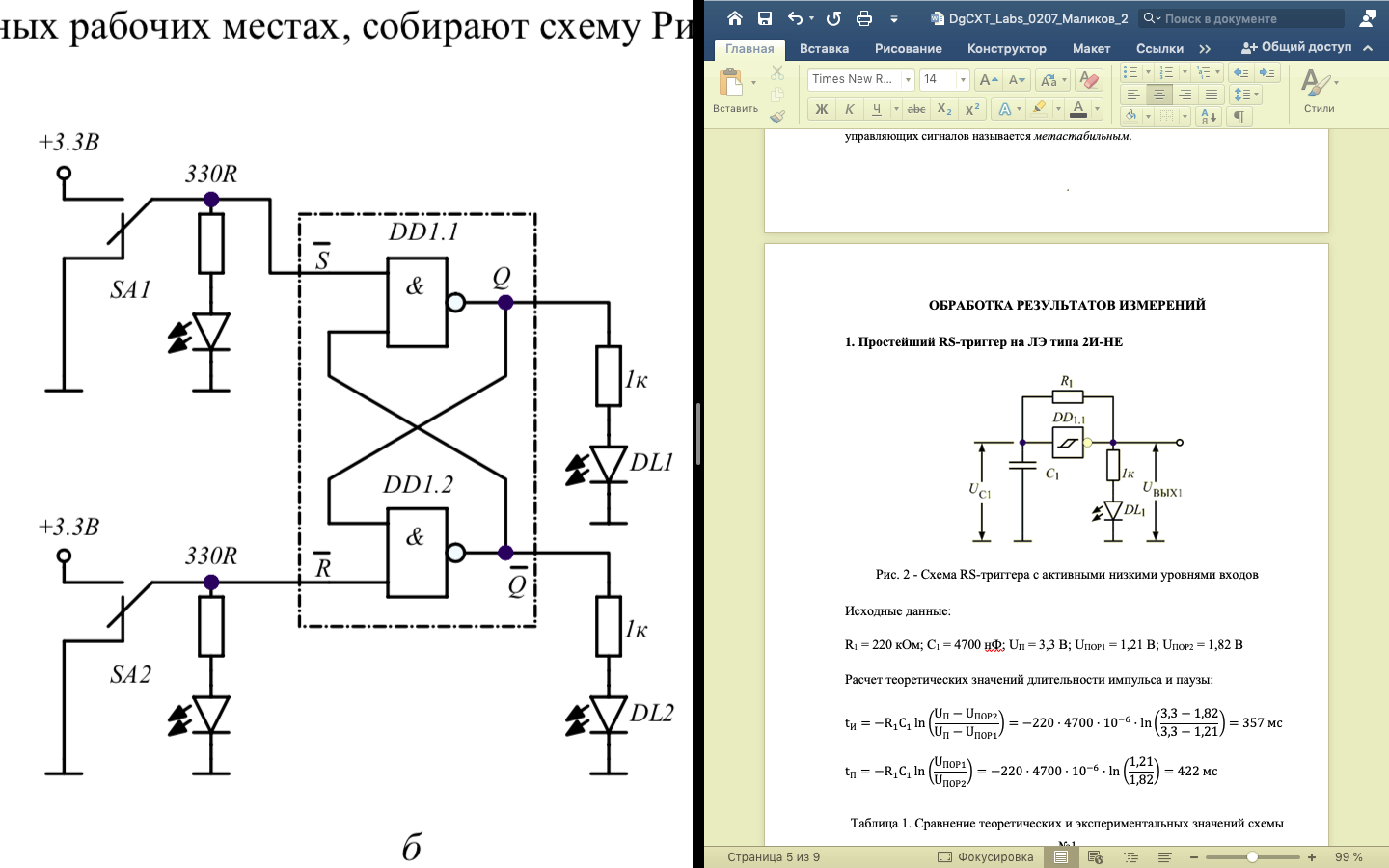

1. Простейший RS-триггер на ЛЭ типа 2И-НЕ

Рис. 2 - Схема RS-триггера с активными низкими уровнями входов

Таблица 1. Таблица переходов RS-триггера на ЛЭ 2И-НЕ

№ п.п

|

Текущее состояние Qn |

Воздействие на входы |

Новое состояние 𝑄n+1

|

||

|

|

Комментарий |

|||

1 |

0 |

0 |

0 |

Активные уровни на обоих входах |

1 |

2 |

1 |

0 |

0 |

1 |

|

3 |

0 |

0 |

1 |

Активный уровень на входе установки |

1 |

4 |

1 |

0 |

1 |

1 |

|

5 |

0 |

1 |

0 |

Активный уровень на входе сброса |

0 |

6 |

1 |

1 |

0 |

0 |

|

7 |

0 |

1 |

1 |

Уровни обоих входов неактивные |

0 |

8 |

1 |

1 |

1 |

|

|

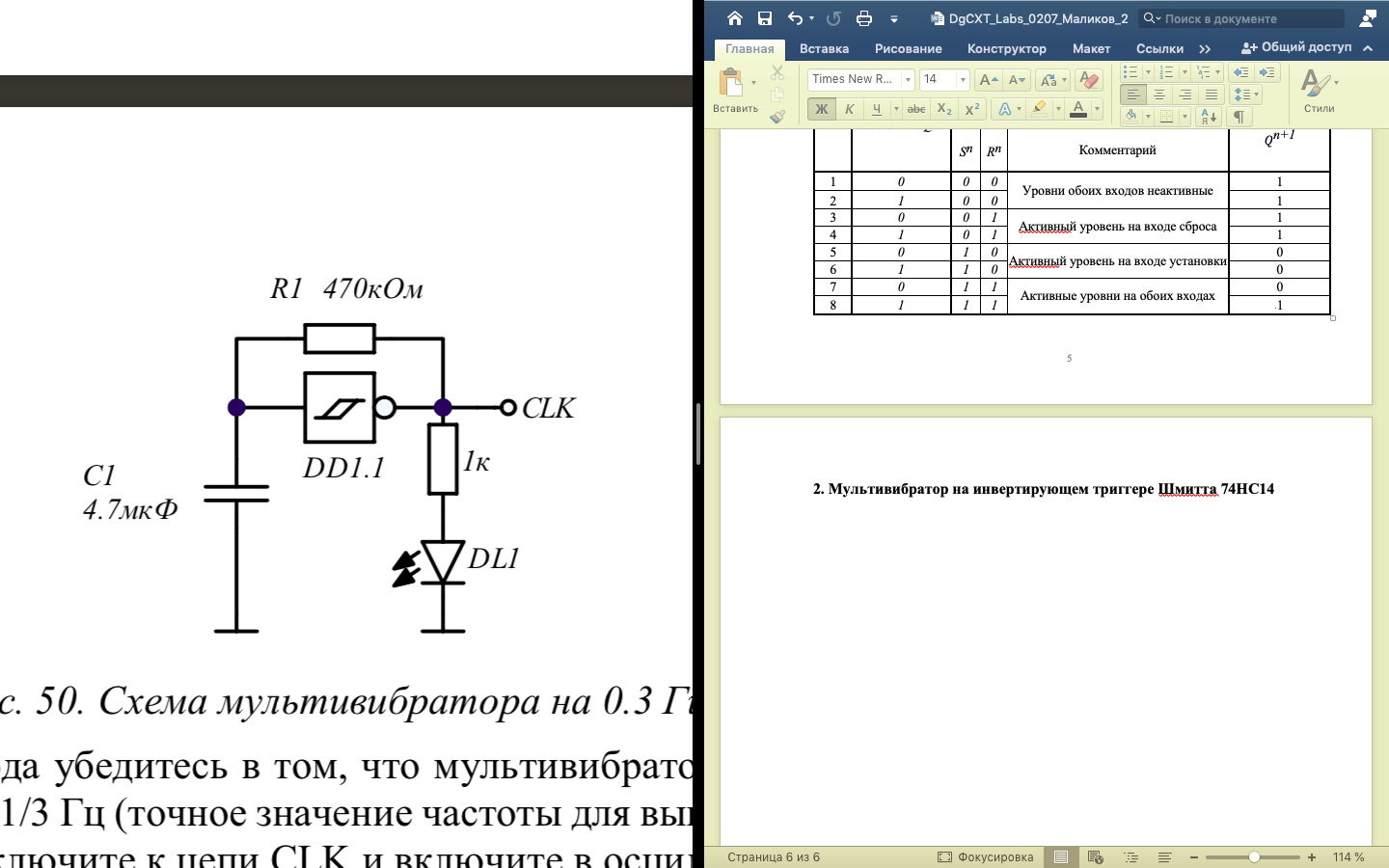

2. Триггер-защелка

Изначально была собрана схема мультивибратора на 0,3 Гц:

Рис. 3 - Схема мультивибратора на 0,3 Гц

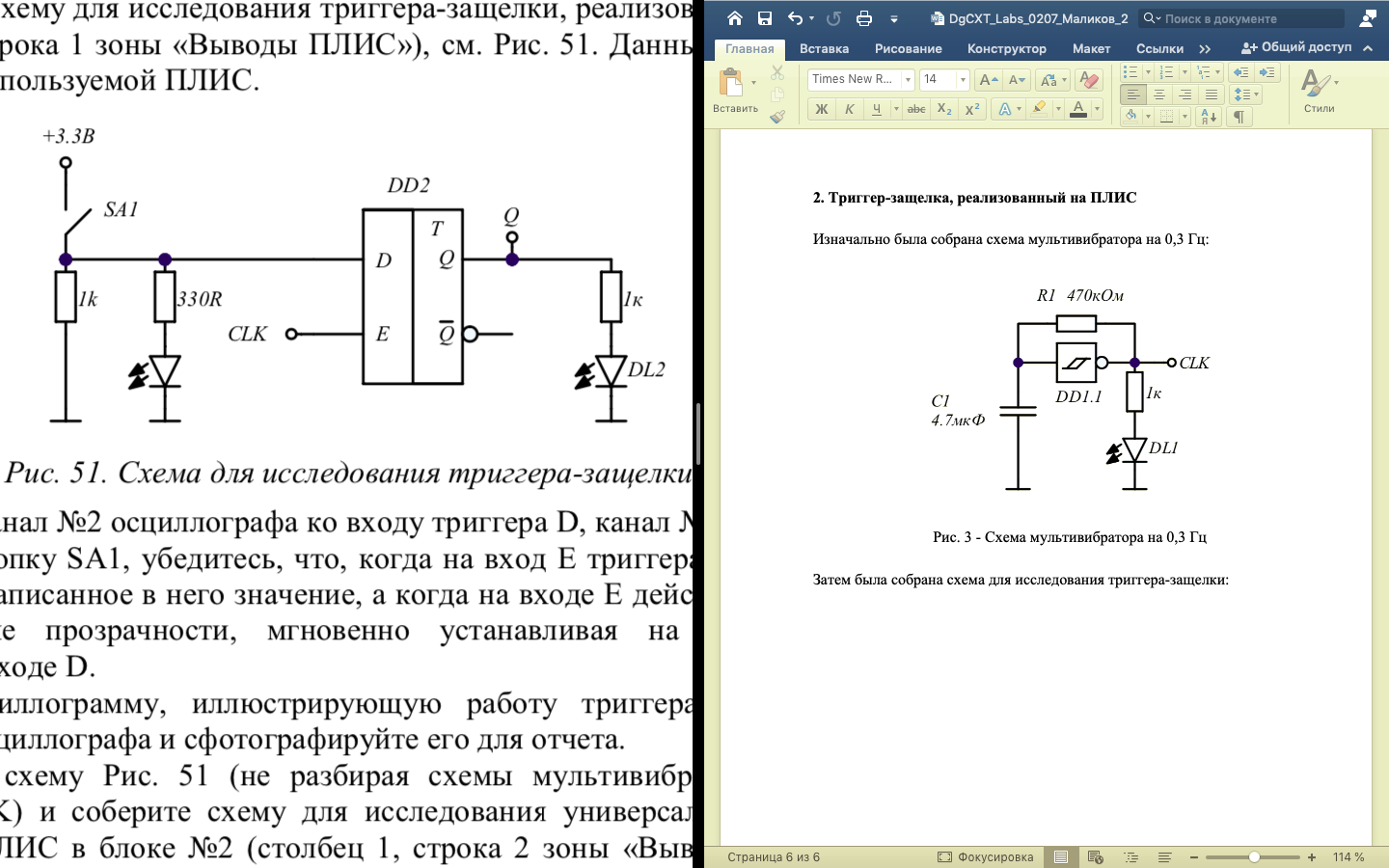

Затем была собрана схема для исследования триггера-защелки:

Рис. 4 – Схема для исследования триггера-защелки

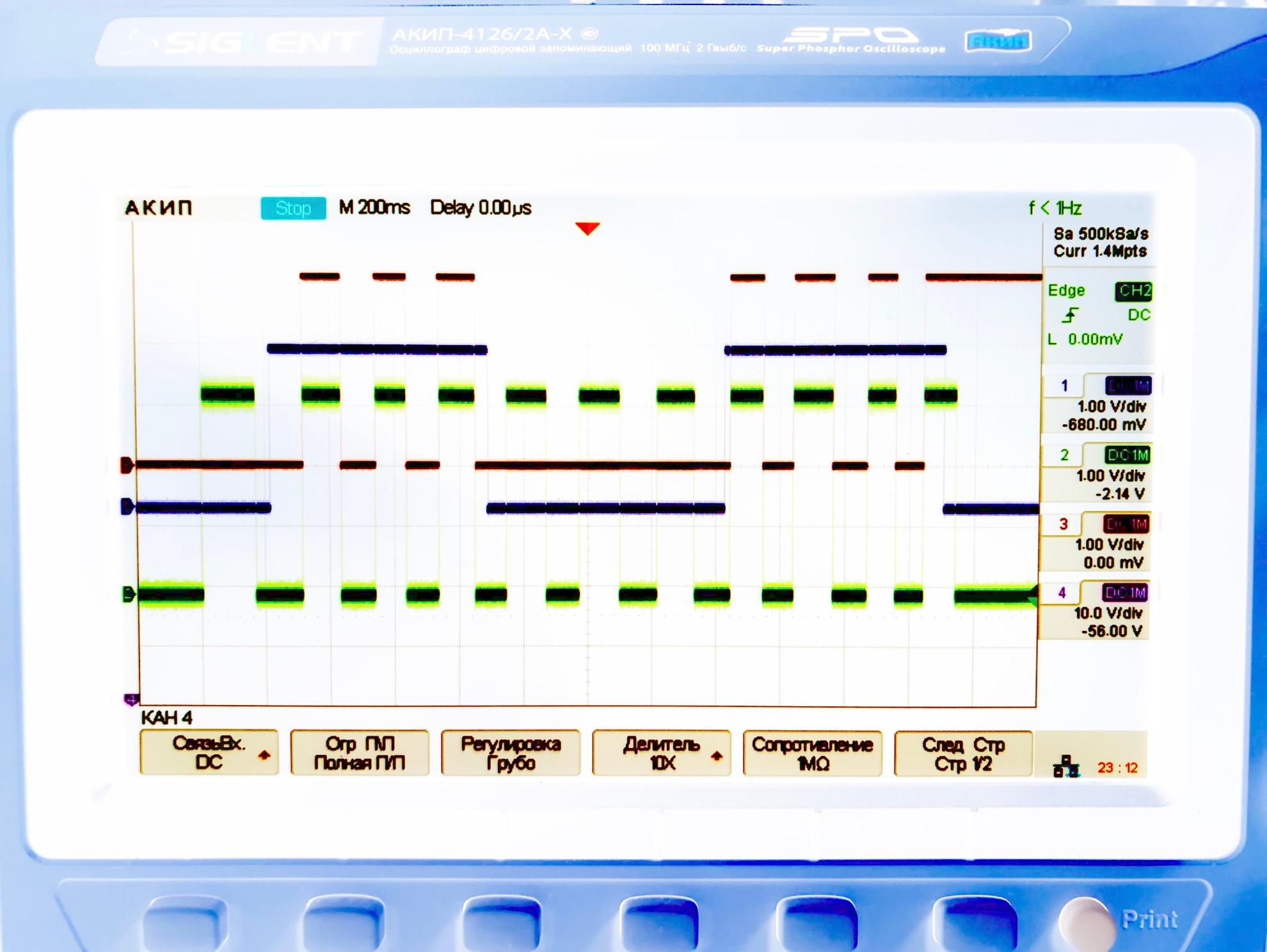

Выход триггера Q

(1 В/дел.)

Вход триггера D

(1 В/дел.)

Цепь CLK (1

В/дел.)

200 мс/дел.

Рис. 5 – Осциллограмма работы триггера-защелки

То есть, когда на вход E триггера подается лог. «0», он хранит предыдущее записанное в него значение, а когда на входе Е действует лог. «1», триггер находится в режиме прозрачности, мгновенно устанавливая на выходе Q уровень, присутствующий на входе D.

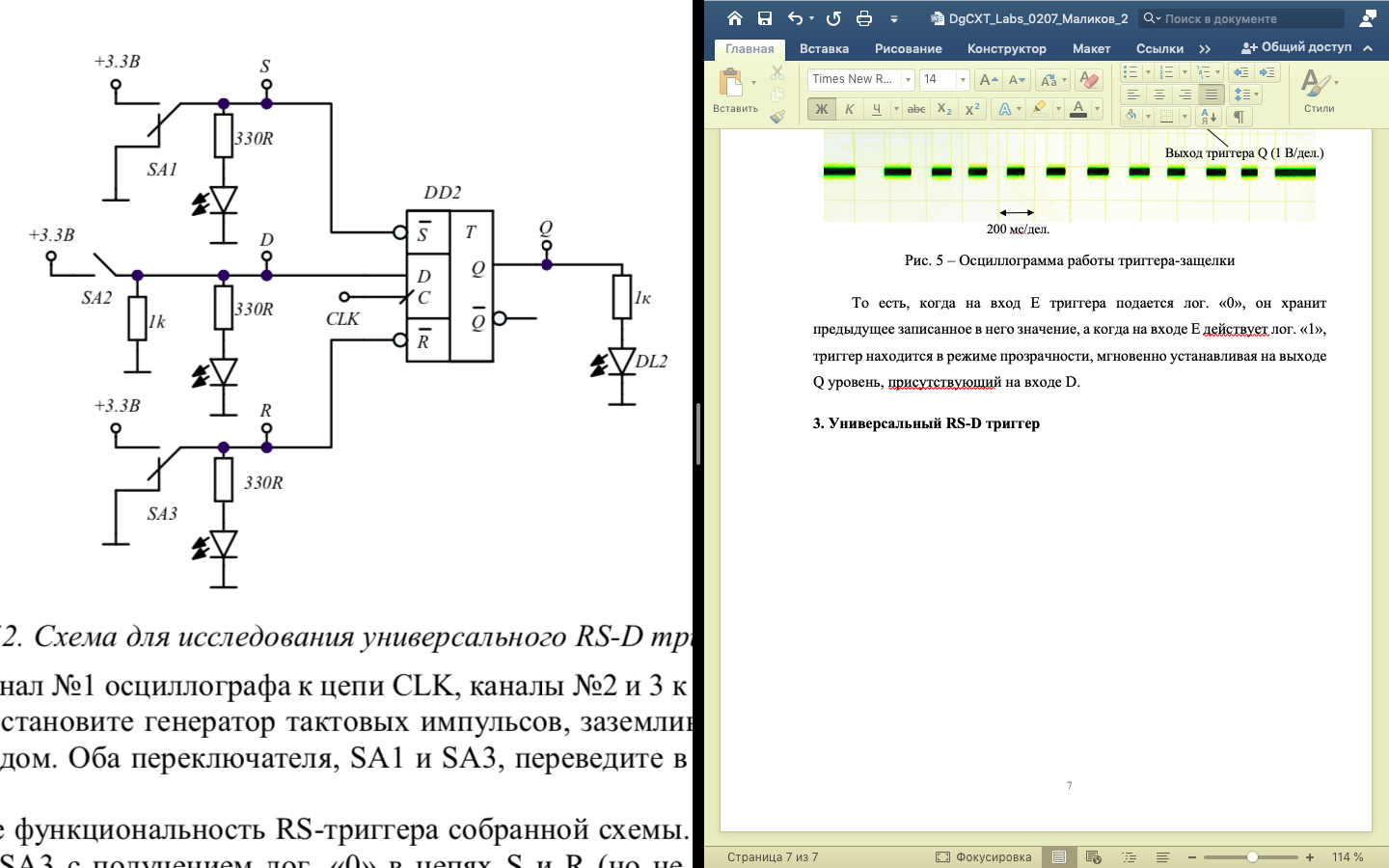

3. Универсальный RS-D триггер

Рис. 6 – Схема для исследования универсального RS-D триггера

Цепь Q (1

В/дел.)

Цепь CLK (1

В/дел.)

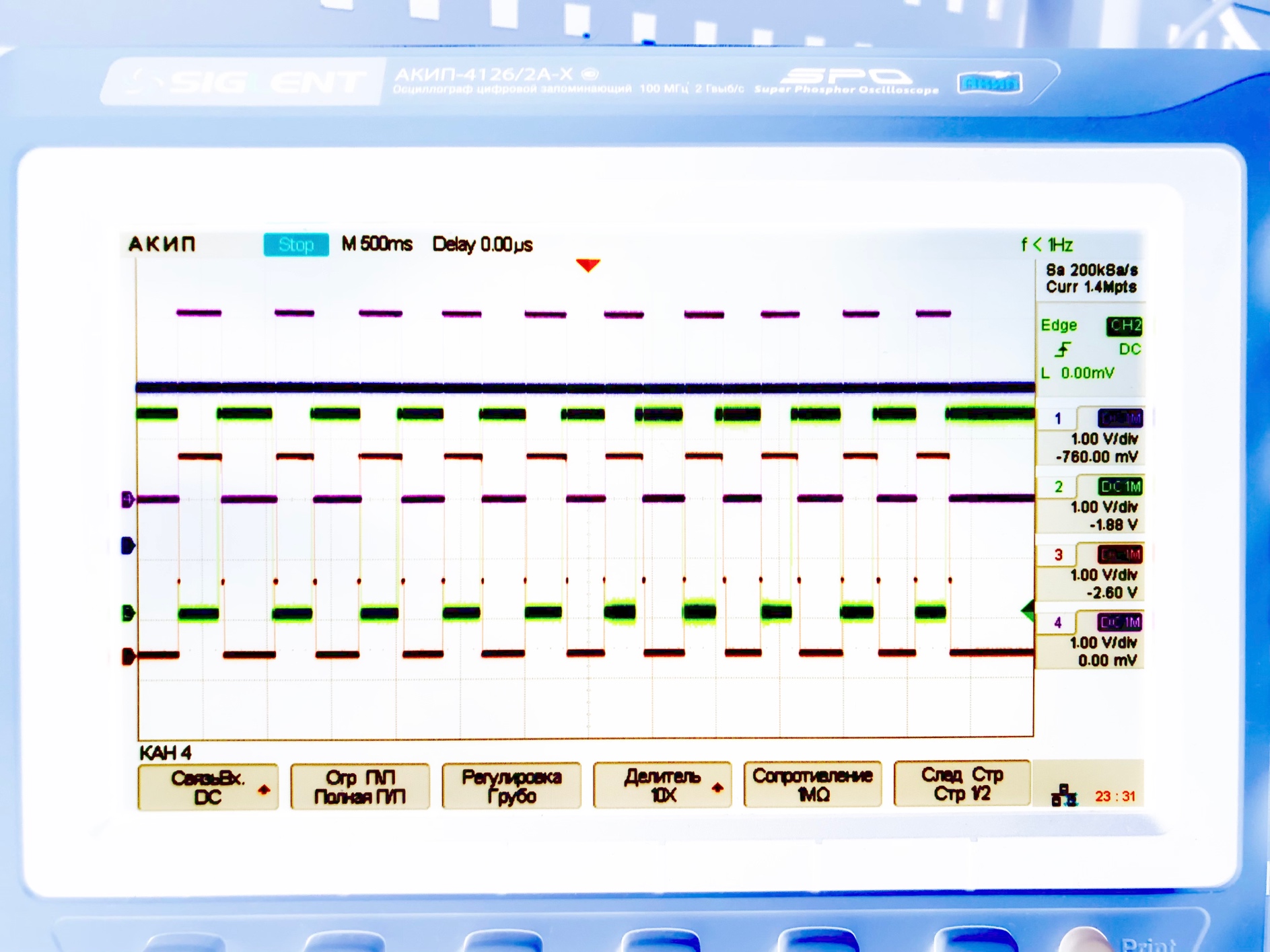

500 мс/дел.

Цепь R (1

В/дел.)

Цепь S (1

В/дел.)

Рис. 7 – Осциллограмма работы RS-D триггера с заземленным входом DD1.1

Таким образом, низкий уровень в цепи S устанавливает триггер, низкий уровень в цепи R сбрасывает его вне зависимости от того обстоятельства, что тактовый генератор остановлен.

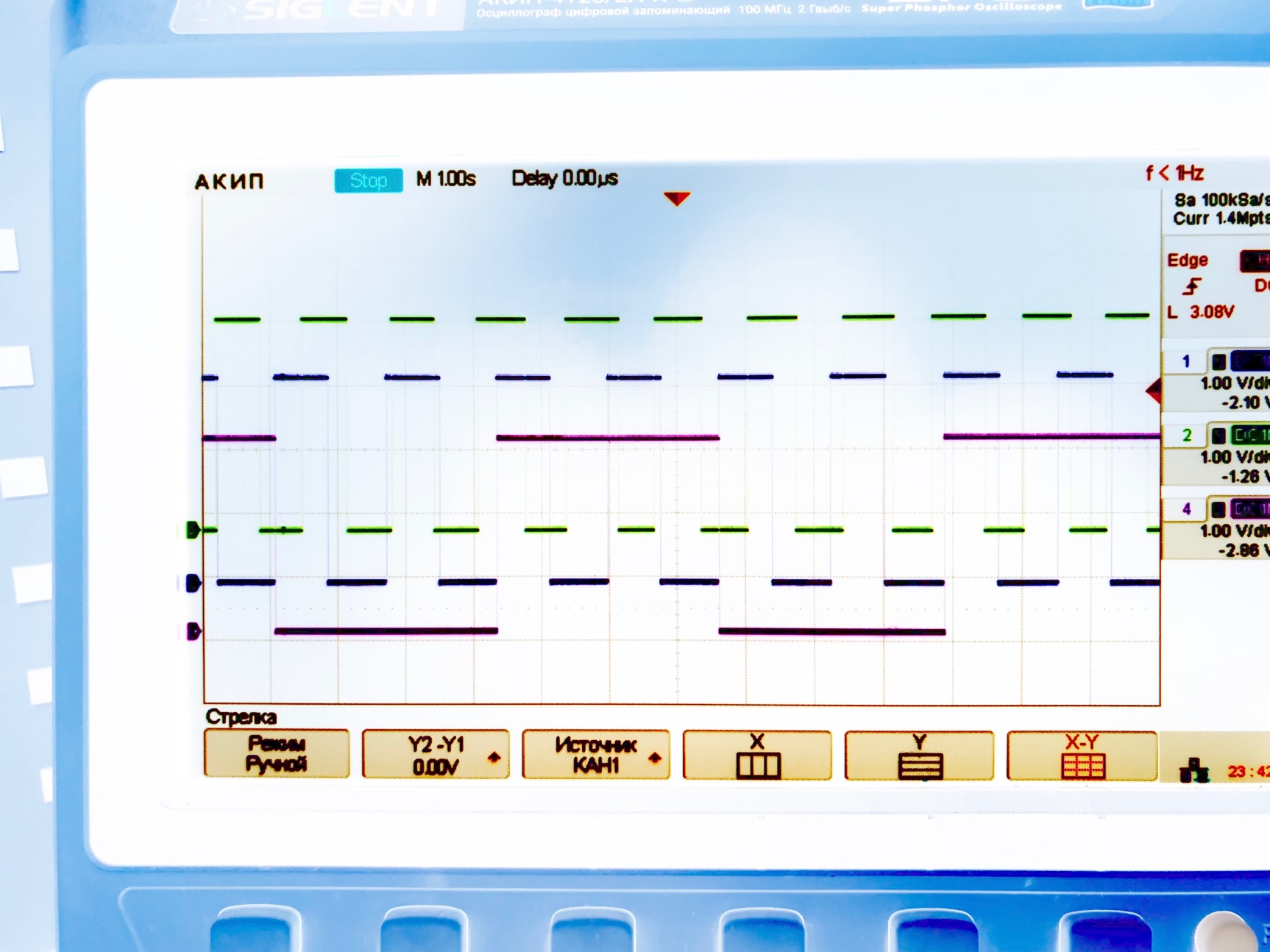

Удаляем монтажный провод, останавливающий тактовый генератор, нажимаем на кнопку SA2, получим следующую осциллограмму:

1 с/дел.

Цепь Q (1

В/дел.)

Цепь D (1

В/дел.)

Цепь CLK (1

В/дел.)

Рис. 8 – Осциллограмма работы RS-D триггера

То есть, нажимая на кнопку SA2, состояние цепи D запоминается триггером по фронту тактового сигнала CLK.

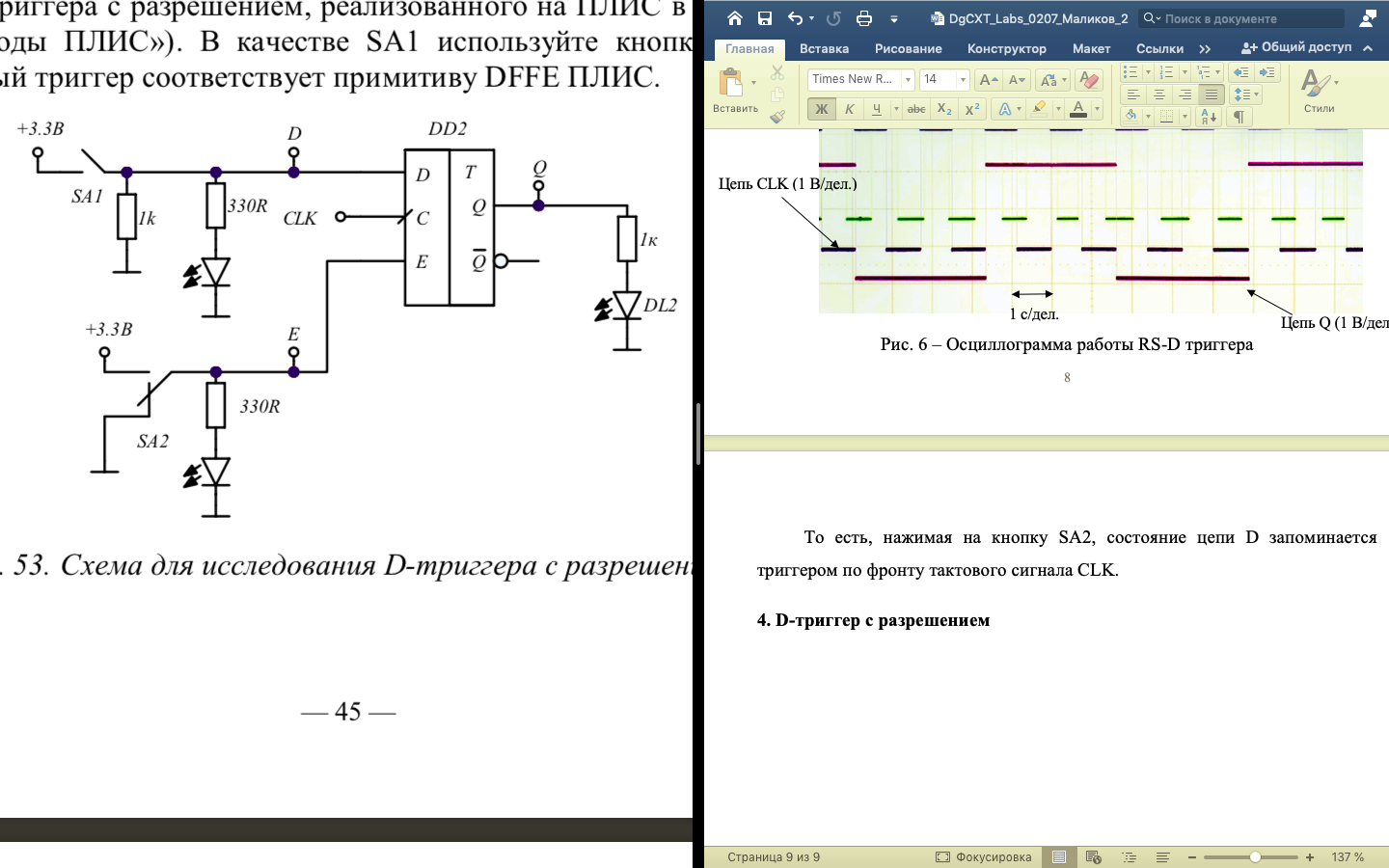

4. D-триггер с разрешением

Рис. 9 – Схема для исследования D-триггера с разрешением

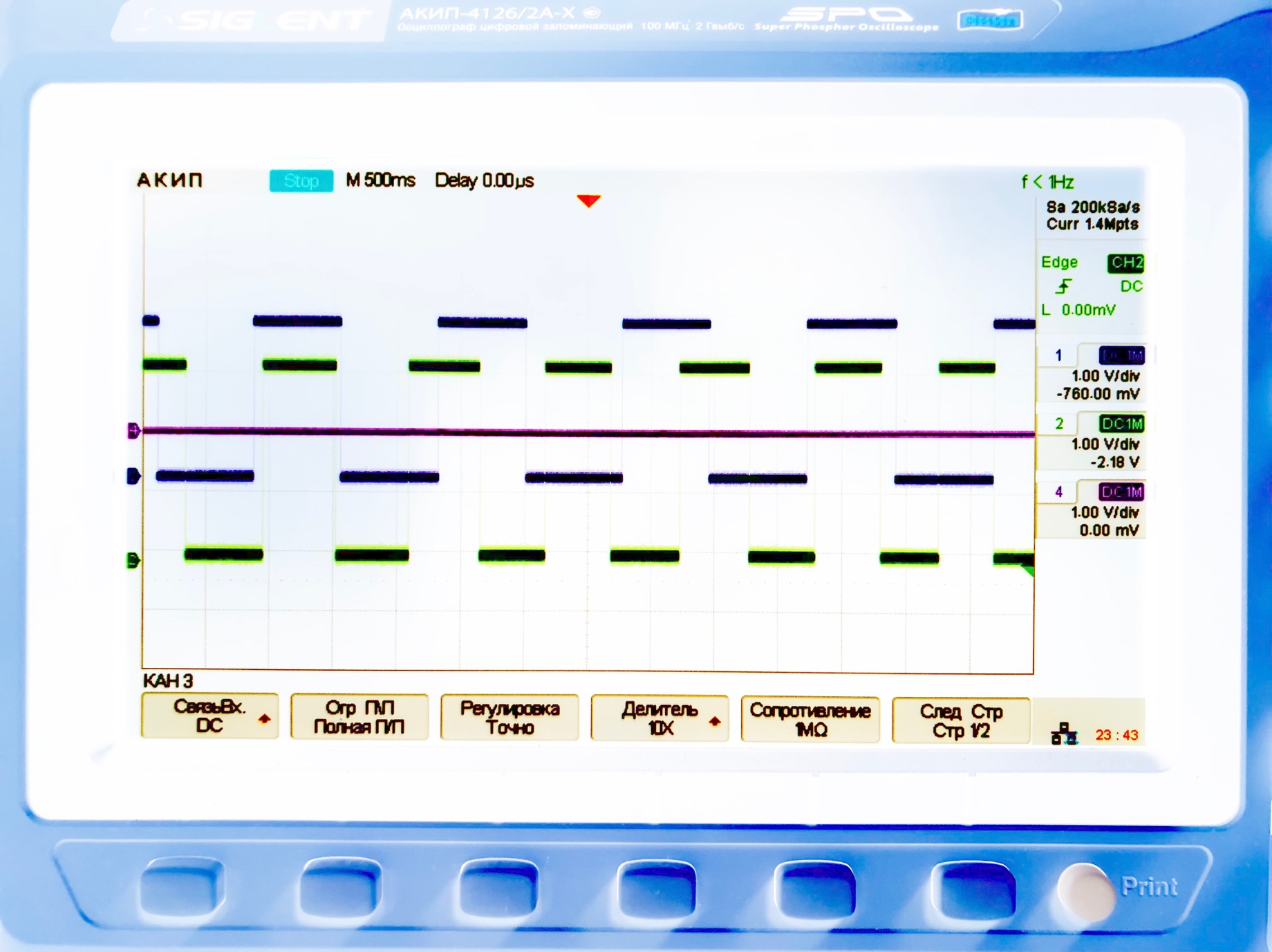

Переведем SA2 (переключатель) в лог. «0», нажимаем кнопку D, получим следующую осциллограмму:

Вход E (1

В/дел.)

Выход Q (1

В/дел.)

Вход D (1

В/дел.)

Цепь CLK (1

В/дел.)

500 мс/дел.

Рис. 10 – Осциллограмма работы D-триггера с разрешением (SA2 в лог. «0»)

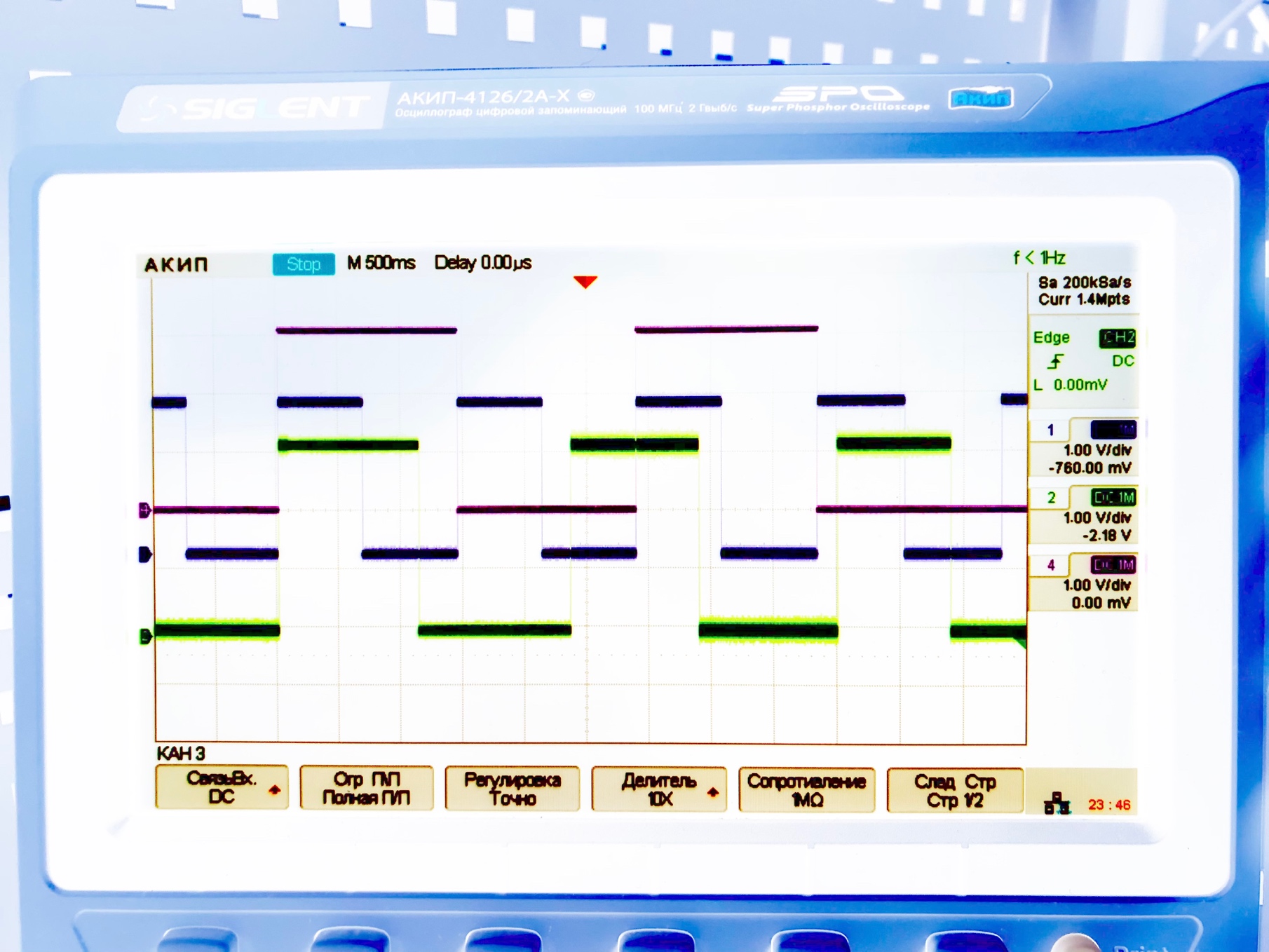

Переведем SA2 (переключатель) в лог. «1», нажимаем кнопку D, получим следующую осциллограмму:

Цепь CLK (1

В/дел.)

Вход D (1

В/дел.)

500 мс/дел.

Вход E (1

В/дел.)

Выход Q (1

В/дел.)

Рис. 11 – Осциллограмма работы D-триггера с разрешением (SA2 в лог. «1»)

Таким образом, переводя SA2 в лог. «1» и нажимая кнопку D, состояние выхода Q становится равным D в момент поступления на триггер фронта тактового сигнала C. В случае SA2 в лог. «0», состояние выхода Q не меняется, какой бы уровень в цепи D не присутствовал в момент поступления на триггер фронта тактового сигнала C.

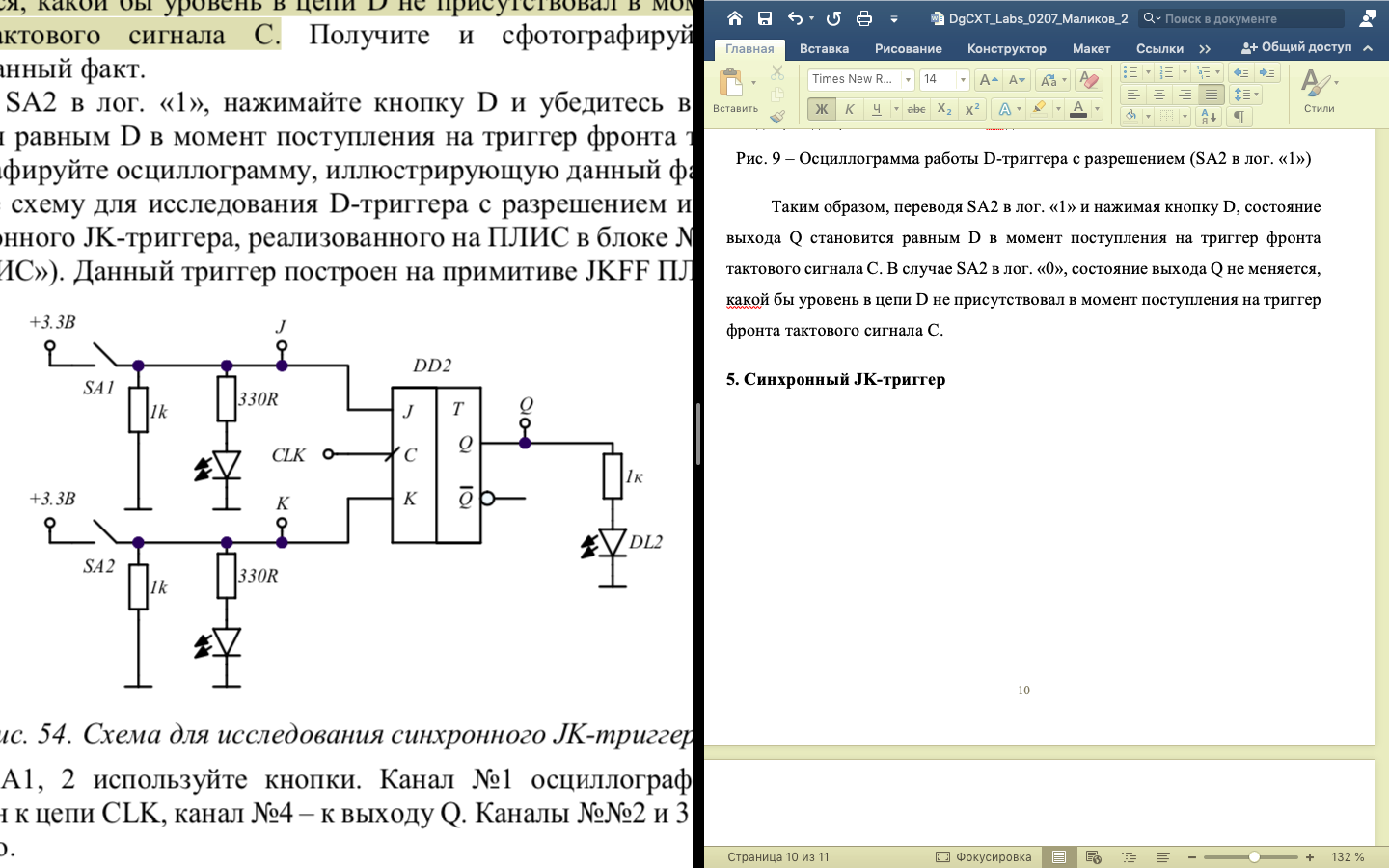

5. Синхронный JK-триггер

Рис. 12 – Схема для исследования синхронного JK-триггера

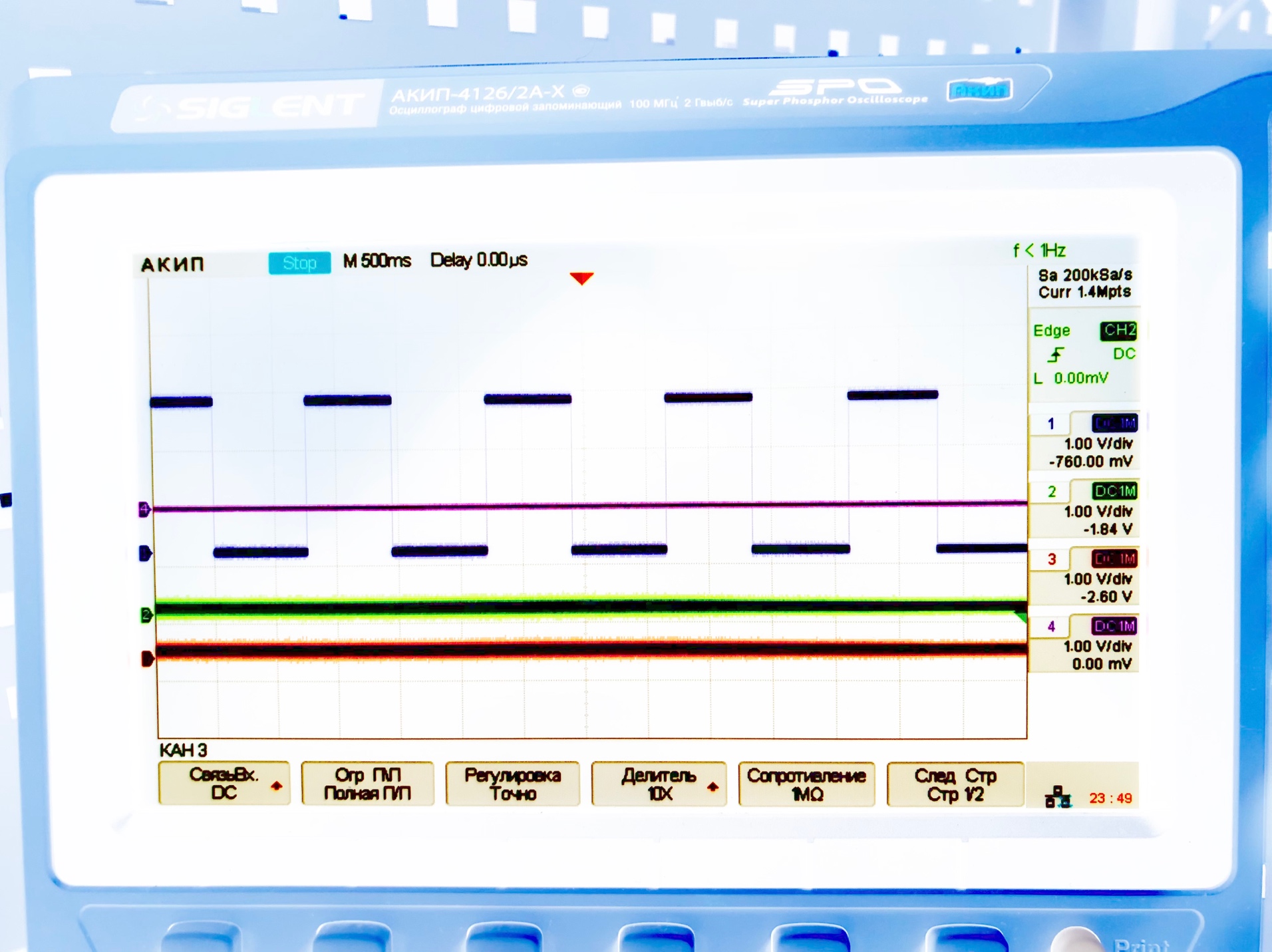

Получим 4 осциллограммы при разных значениях J и K:

Выход K (1

В/дел.)

Выход J (1

В/дел.)

Выход Q (1

В/дел.)

Цепь CLK (1

В/дел.)

500 мс/дел.

Рис. 13 – Осциллограмма работы синхронного JK-триггера при J=0 и K=0

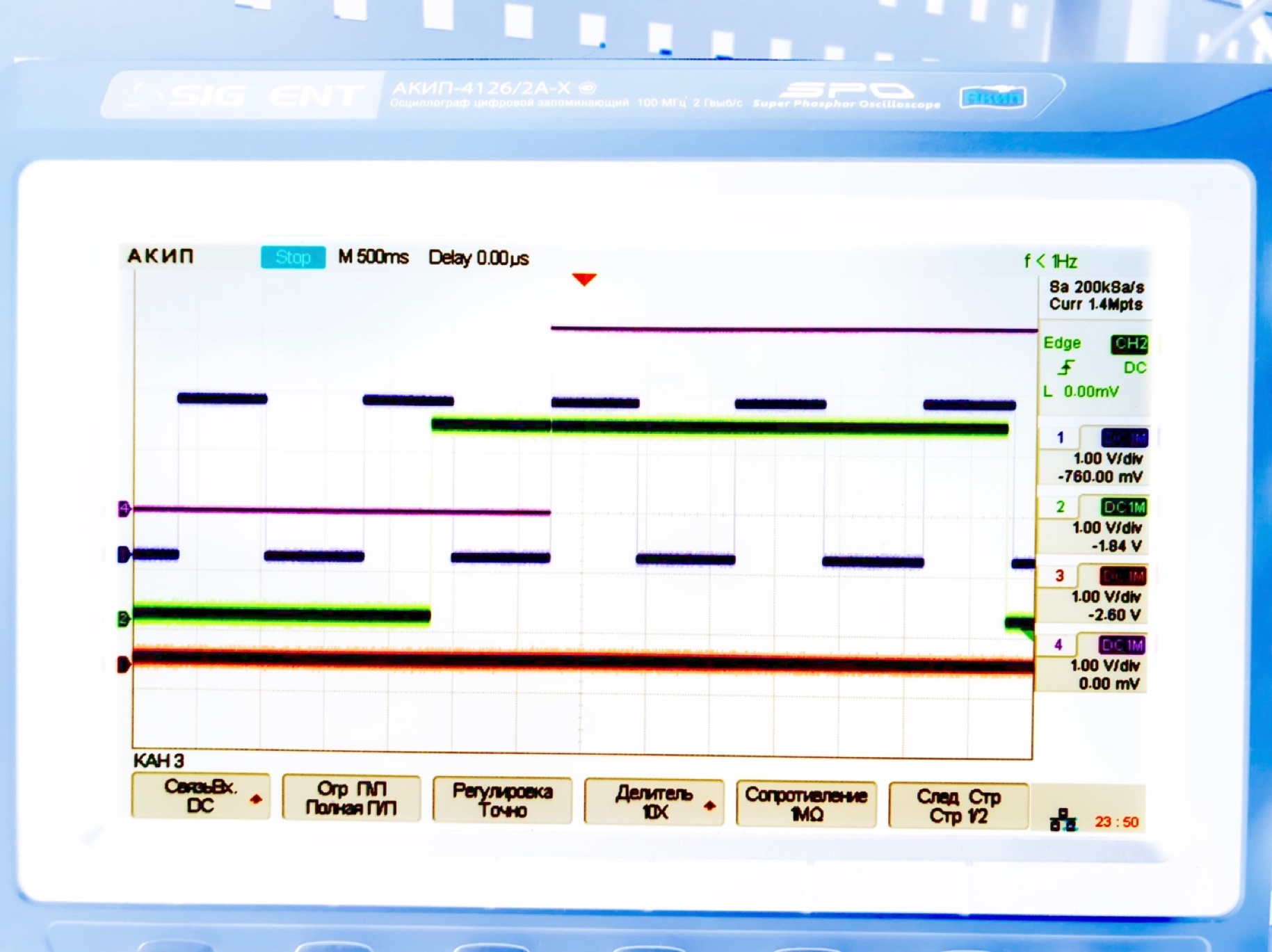

Цепь CLK (1

В/дел.)

Выход Q (1

В/дел.)

Выход J (1

В/дел.)

Выход K (1

В/дел.)

500 мс/дел.

Рис. 14 – Осциллограмма работы синхронного JK-триггера при J=1 и K=0

Таким образом, при J=K=0, синхронный JK-триггер хранит последнее записанное в него значение, то есть Q неизменно, а при J=1 и K=0 устанавливается.

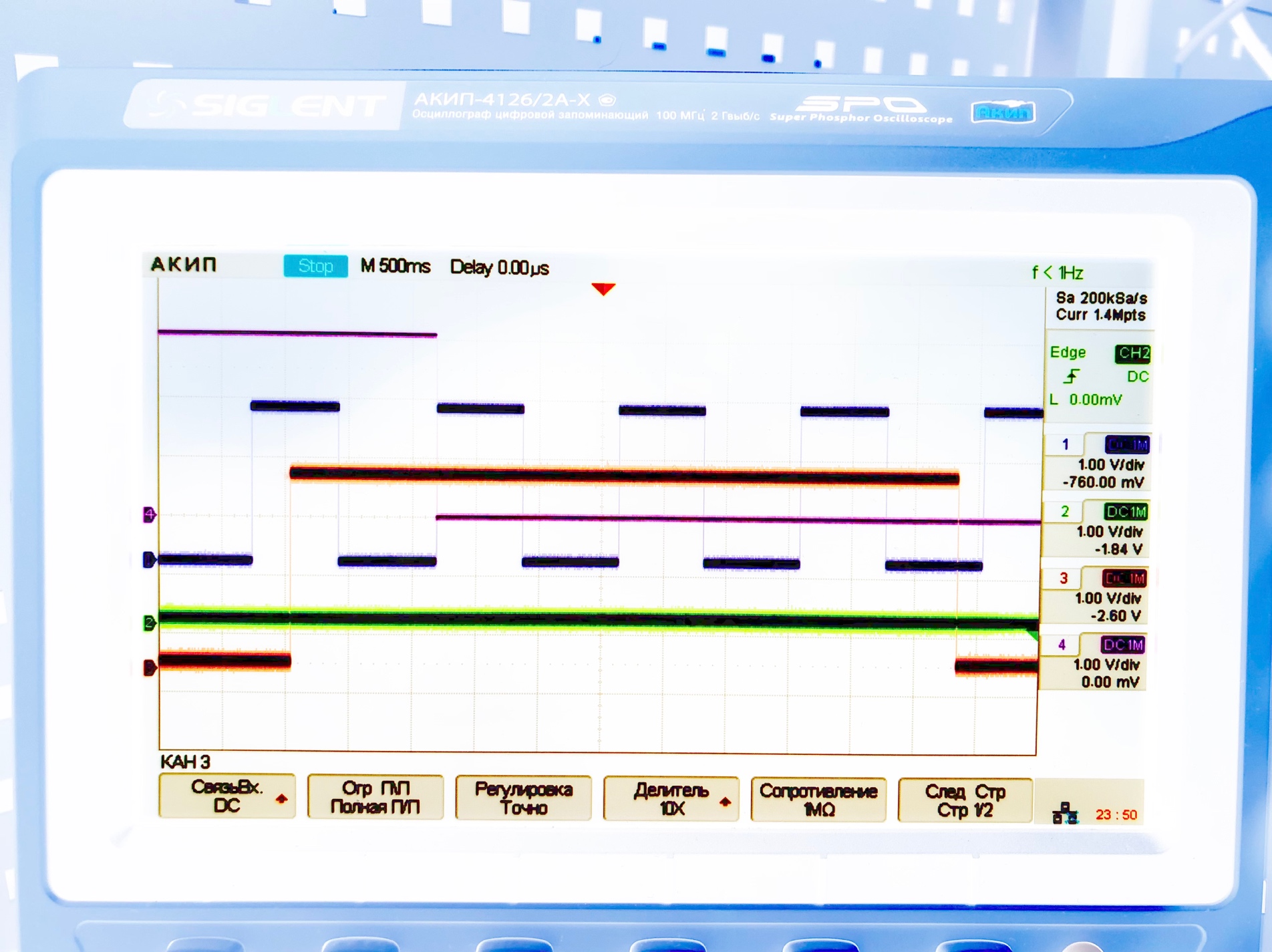

Цепь CLK (1

В/дел.)

Выход Q (1

В/дел.)

Выход J (1

В/дел.)

Выход K (1

В/дел.)

500 мс/дел.

Рис. 15 – Осциллограмма работы синхронного JK-триггера при J=0 и K=1

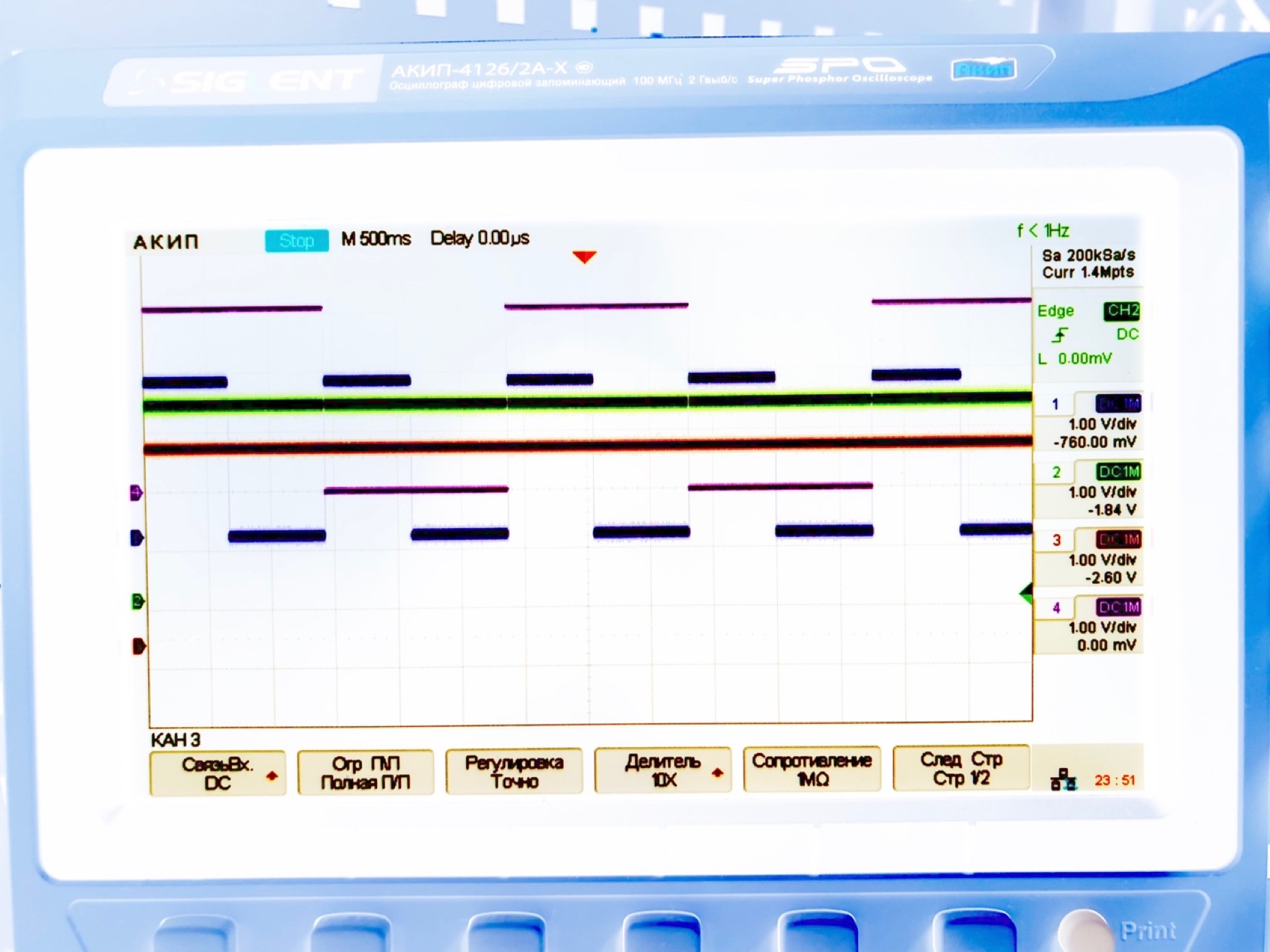

Выход J (1

В/дел.)

Выход K (1

В/дел.)

Цепь CLK (1

В/дел.)

Выход Q (1

В/дел.)

500 мс/дел.

Рис. 16 – Осциллограмма работы синхронного JK-триггера при J=K=1

Таким образом, при J=0 и K=1, синхронный JK-триггер сбрасывается, а при J=1 и K=1 переводит Q в состояние, противоположное предыдущему.

ВЫВОД

Анализируя схему триггера-защелки (рис. 4) и осциллограмму данной схемы (рис. 5), делаем вывод, что данный триггер представляет собой узел, способный запоминать бит, присутствующий на входе D. Когда на вход E триггера подается лог. «0», он хранит предыдущее записанное в него значение, а когда на входе Е действует лог. «1», триггер находится в режиме прозрачности, мгновенно устанавливая на выходе Q уровень, присутствующий на входе D.

Также, анализируя схему универсального RS-D триггера (рис. 6) и осциллограмму данной схемы (рис. 7), делаем вывод, что низкий уровень в цепи S устанавливает триггер, низкий уровень в цепи R сбрасывает его.

Анализируя схему D-триггера с разрешением (рис. 9) и осциллограммы работы данной схемы (рис. 10 и рис. 11), делаем вывод, что при переключении SA2 в лог. «1» и нажатии кнопки D, состояние выхода Q становится равным D в момент поступления на триггер фронта тактового сигнала C (цепь CLK). В случае переключения SA2 в лог. «0», состояние выхода Q не меняется, какой бы уровень в цепи D не присутствовал в момент поступления на триггер фронта тактового сигнала C (цепь CLK).

Также, анализируя схему синхронного JK-триггера (рис. 12) и осциллограммы данной схемы (рис. 13, 14, 15), делаем вывод, что при J=K=0 синхронный JK-триггер хранит последнее записанное в него значение, то есть Q неизменно; при J=1 и K=0 синхронный триггер устанавливается; при J=0 и K=1 триггер сбрасывается; при J=K=1 синхронный триггер переводит Q в состояние, противоположное предыдущему.