lr4

.docxФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ

Федеральное государственное бюджетное образовательное

учреждение высшего образования

«Санкт-Петербургский государственный университет телекоммуникаций

им. проф. М. А. Бонч-Бруевича»

___________________________________________________________________________

Кафедра программной инженерии и вычислительной техники.

Дисциплина «Микропроцессорные устройства»

Лабораторная работа № 4

«Исследование 4х-разрядного сумматора»

Выполнили: ст. гр.

Проверил: ст.пр. Неелова О.Л.

_____________________

Санкт-Петербург

2024

Программа 4.1

Одноразрядный сумматор

module biba_sum

(input wire a,b,cr,

output wire s,crp);

assign s=(a^b)^cr;

assign crp=(a&b) | ((a^b)&cr);

endmodule

Testbench

`timescale 1ns/100ps

module biba_sum_tb;

logic a, b,cr;

logic s,crp;

biba_sum uut_biba_sum (.a(a), .b(b), .cr(cr), .s(s), .crp(crp));

initial

begin

a=1'b0;

b=1'b0;

cr=1'b0;

#100;

a=1'b1;

b=1'b0;

cr=1'b0;

#100;

a=1'b0;

b=1'b1;

cr=1'b0;

#100;

a=1'b0;

b=1'b0;

cr=1'b1;

#100;

a=1'b1;

b=1'b1;

cr=1'b0;

#100;

a=1'b1;

b=1'b0;

cr=1'b1;

#100;

a=1'b0;

b=1'b1;

cr=1'b1;

#100;

a=1'b1;

b=1'b1;

cr=1'b1;

#100;

$stop;

end

endmodule

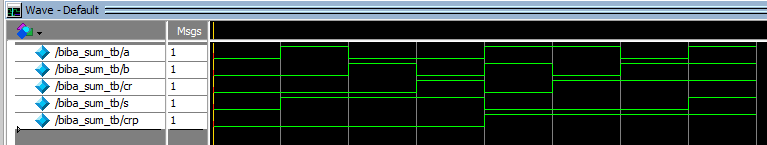

Рис.1 Симуляция работы одноразрядного сумматора

Программа 4.2 Четырехразрядный сумматор

module biba_sum_4

(input wire [3:0]a_in,b_in,

input wire cr_in,

output wire [3:0]s_out,

output wire crp_out);

wire [2:0]crp_n;

biba_sum sum0(.a (a_in[0]),.b (b_in[0]),.cr(cr_in),.s(s_out[0]),.crp(crp_n[0]));

biba_sum sum1(.a (a_in[1]),.b (b_in[1]),.cr(crp_n[0]),.s(s_out[1]),.crp(crp_n[1]));

biba_sum sum2(.a (a_in[2]),.b (b_in[2]),.cr(crp_n[1]),.s(s_out[2]),.crp(crp_n[2]));

biba_sum sum3(.a (a_in[3]),.b (b_in[3]),.cr(crp_n[2]),.s(s_out[3]),.crp(crp_out));

endmodule

Testbench:

`timescale 1ps/1ps

module biba_sum_4_tb;

logic [3:0] a_in, b_in;

logic cr_in;

logic [3:0] s_out;

logic crp_out;

biba_sum_4 uut_biba_sum_4 (.a_in(a_in), .b_in(b_in), .cr_in(cr_in), .s_out(s_out), .crp_out(crp_out));

initial

begin

a_in<=4'b1;

b_in<=4'b0011;

cr_in<=1'b1;

#100;

a_in<=4'b0010;

b_in<=4'b0101;

#100;

a_in<=4'b1111;

b_in<=4'b1101;

end

endmodule

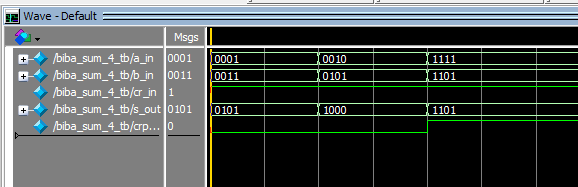

Рис.2 Симуляция работы четырехразрядного сумматора

Программа 4.3

Кодопреобразователь

module biba_coder

(input wire [3:0] data,

output wire [6:0] seg);

reg [6:0]code;

assign seg=code;

always @*

case(data)

4'b0000: code = 7'b1000000;

4'b0001: code = 7'b1111001;

4'b0010: code = 7'b0100100;

4'b0011: code = 7'b0110000;

4'b0100: code = 7'b0011001;

4'b0101: code = 7'b0010010;

4'b0110: code = 7'b0000010;

4'b0111: code = 7'b1111000;

4'b1000: code = 7'b0000000;

4'b1001: code = 7'b0010000;

4'b1010: code = 7'b0001000;

4'b1011: code = 7'b0000011;

4'b1100: code = 7'b1000110;

4'b1101: code = 7'b0100001;

4'b1110: code = 7'b0000110;

4'b1111: code = 7'b0001110;

endcase

Testbench

`timescale 1ns/1ps

module biba_coder_tb;

logic [3:0] data;

logic [6:0] seg;

biba_coder uut_biba_coder (.data(data), .seg(seg));

initial begin

data=4'b1011;

#10

data=4'b0001;

#10

data=4'b1011;

#10

data=4'b1010;

end

endmodule

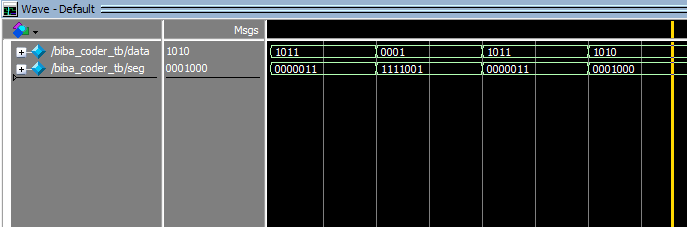

Рис.3 Симуляция работы кодопреобразователя

Программа 4.4

4-разрядный сумматор с сохранением результата в регистре

module biba_summ_4

(input wire [3:0]op_a,op_b,

input wire op_c, sync,

output wire led,

output wire [6:0]hex);

wire [3:0]sm;

wire c_y;

wire [4:0]y;

assign led=y[4];

biba_sum_4 block1(.a_in(op_a), .b_in(op_b), .cr_in(op_c), .s_out(sm), .crp_out(c_y));

biba_latch_rgstr block2(.d_in({c_y,sm[3:0]}), .clk(sync), .d_out(y));

biba_coder block3(.data(y[3:0]), .seg(hex));

endmodule

Testbench

`timescale 1ns/1ps

module biba_summ_4_tb;

logic [3:0] op_a, op_b;

logic op_c, sync;

logic led;

logic [6:0] hex;

biba_summ_4 uut_biba_summ_4 (.op_a(op_a), .op_b(op_b), .led(led), .hex(hex), .op_c(op_c), .sync(sync));

initial begin

sync=1'b0;

forever begin

#5 sync=~sync;

end

end

initial begin

op_a<=4'b0001;

op_b<=4'b0011;

op_c<=1'b1;

#10;

op_a<=4'b0010;

op_b<=4'b0101;

#10;

op_a<=4'b1111;

op_b<=4'b1101;

end

endmodule

Рис.4 Симуляция работы 4-разрядного сумматора с сохранением результата в регистре